- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

标准线性集成电路的电诱发损坏

简介

电子器件对瞬态电气过应力事件的灵敏度是众所周知的问题,随着集成电路的不断发展,这一问题日益严重。几何尺寸缩小,电路密度增加和分配给片内保护的面积有限都会使此灵敏度趋于增加。为了将每一特定系统实施环节的成本降至最低,瞬态保护的任务往往转而采用其它效率更低的方式。

防止“击穿”的技术取决于制造的阶段。制造集成电路和装配电子设备期间,保护通过使用我们所熟知的措施来实现,比如静电耗散桌面、防静电手环、电离空气吹风机、防静电包装套管等。此处,仅简要讨论这些方法与静电放电(SD)保护相关的部分。同样,本应用笔记并不旨在说明设备运输、安装或维修期间所采取的预防措施。而是,重点主要集中在印刷电路板装配期间、设备正常工作(操作人员经常未接受预防措施培训)期间以及在瞬态环境可能不具有良好特性的服务条件下所需要的保护。

瞬态环境千变万化。汽车系统、机载或船载设备、空间系统、工业设备或消费电子产品等所经历的瞬态环境存在很大不同。所有类型的电子器件都会受到毁坏或损害。1甚至电容、继电器、连接器、印刷电路板等阈值水平远高于集成电路的器件都是易受影响的。微波二极管和晶体管是当中最敏感的器件。但是,本应用笔记将针对用途较广泛的标准线性集成电路进行说明,以限制文章涵盖的范畴。

本应用笔记首先将回顾集成电路在工作环境中所受威胁的本质,然后会针对以下问题简要讨论总体的设备保护:(1)由人员操作、自动板插入设备等引起的ESD事件;(2)由于上电/关断时序误差、连接器边缘松动引起的浮动地等问题而产生的闩锁;最后,(3)电源、电路板缺陷、电路板检修期间等造成的高电压瞬态。

静电放电

静电放电是由以下原因导致的单次快速高电流的静电电荷传输:

• 两个处于不同电位的物体之间的直接接触传输,或者

• 两个物体靠近时之间产生的高静电场。

静电的主要来源基本都是绝缘器并且一般都是合成材料,例如乙烯基树脂或塑料工作台、绝缘鞋、成品木椅、透明胶带、气泡袋、未接地的烙铁等。这些来源产生的电平极高,因为它们的电荷并不容易分布在表面上或者传导给其他物体。

两个物体相互摩擦产生静电被称为摩擦电效应。例如,高RH(60%)环境下,摩擦静电电荷产生的来源包括:

• 在地毯上走过 — 产生1000 V–1500 V。

• 在乙烯基树脂地板上走过 — 产生150 V-250 V。

• 手持由干净塑料包装保护的材料 — 产生400 V–600 V。

• 手持聚乙烯袋 — 产生1000 V–1200 V。

• 将聚氨酯泡沫塑料倒入盒中 — 产生1200 V– 1500 V。

• IC滑入一个开口的防静电包装套管中 — 产生25V–250 V。

注意:在低RH(<30%)环境中,可以产生上述10倍以上的电压。

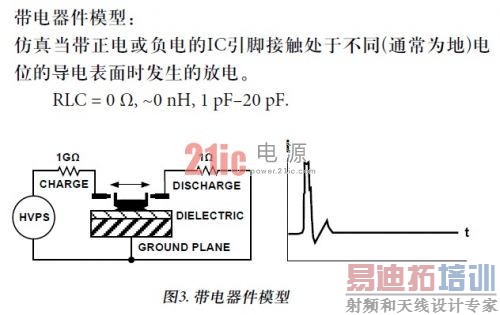

ESD模型

为了评估器件对仿真应力环境的敏感性,已开发出大量测试波形。目前普遍用于仿真半导体或分立器件中的ESD事件的三个最主要的波形是:人体模型(HBM)、机器模型(MM)和带电器件模型(CDM)。这三种模型的测试电路和电流波形特性如图1至3所示。每个模型代表一种根本上不同的ESD事件。因此,这些模型的测试结果之间的相关性微乎其微。

[p]

[p]

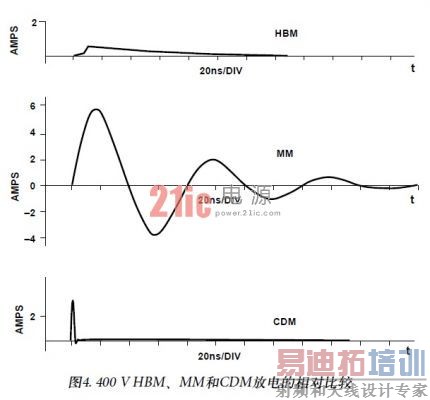

HBM、MM和CDM波形的比较

图4显示在相同的电流-时间标度下的400 V HBM、MM和CDM放电波形。这些波形在预测特定类型器件由于这三种模型之一仿真的ESD事件而可能会产生何种故障机制方面作用显著。

HBM波形的上升时间小于10ns(一般为6ns至9ns),此波形以大于150ns的下降时间成指数规律衰减到0V。MIL-STD-883 3 Method 3015《静电放电灵敏度等级》要求上升时间小于10 ns,延迟时间为150 ± 20 ns(Method 3015将延迟时间定义为波形从90%峰值电流降至36.8%峰值电流的时间)。HBM波形的峰值电流约等于400V/1500或0.267A。虽然该峰值电流远低于400 V HBM和MM事件的峰值电流,但整个HBM事件的持续时间相对较长,这导致放电能量相对较高。

MM波形由正向和负向正弦波峰值组成,峰值幅度以指数规律衰减。初始MM峰的上升时间约为14 ns,即略大于单一HBM峰的上升时间。MM波形的总持续时间与HBM波形相当。但是,400V MM事件的第一个峰的峰值电流约为5.8A,是三种模型中最高的。接下来的四个峰值电流虽然在下降,但幅度仍全部大于1A。因为不存在电流限制,R = 0,这几个持续时间很长的高电流峰值导致目前三种模型之中最高的总体放电能量。

CDM波形对应于现实中已知最短的ESD事件。套接式CDM波形的上升时间为400ps,CDM事件的总持续时间约为2ns。CDM波形本质上是单极性的,不过在CDM事件结束时会发生某种轻微的振铃,这会导致部分负向峰值。

使用400 V带电电压,套接式CDM放电将具有2.1 A的峰值电流。但是,总体CDM事件的持续时间极短,这导致总体放电能量相对较低。

ESD模型小结

表I是比较三种ESD仿真模型的最重要特性的参考。

预防

审查将采取ESD保护措施的设备时,应考虑以下因素:

• 必须有一个接地工作台来处理静电敏感器件,结合使用以下装置:

a)个人接地带(防静电手环)

b)导电托盘或分流器等

c)导电工作台

d)导电地板或地垫

e)一个公共接地点

• 所有用于存储器件的钢架或机柜必须接地。

• 应控制相对湿度;理想范围是40%至60%。在无法维持高相对湿度水平的地方,应使用电离空气来驱散静电

电荷。

• 区域中使用的所有电气设备必须接地。

• 禁止使用易产生静电的器材,例如透明胶带。

• 后续至少每隔三个月做一次ESD审查。

• 培训:切记有效ESD控制程序的关键是“培训”。所有接触集成电路的人员都应进行培训并且培训要记录归档作认证之用,例如ISO9000审计。

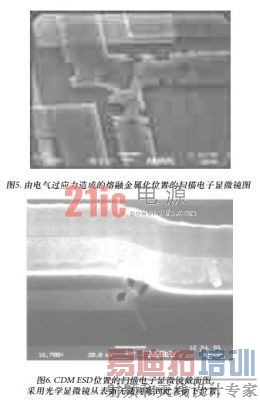

确定器件是否是由于ESD或电气过应力(EOS)而发生故障较为困难,一般最好交由故障分析工程师处理。执行电气分析和内部可视分析时,ESD损害一般没有EOS的损害明显。对于ESD,1 kV或以上(取决于器件的ESD额定值)的事件会毁坏氧化层(管芯的层间电介质)并在10ns以内损坏结点(见图6)。或者,EOS条件导致持续时间大于1 ms的1至3 A电流,使焊线产生足够多自热效应而被熔断。闩锁会造成此类条件发生。较低的电流会导致芯片金属化层及其他互连层的快速熔化(见图5)。

[p]

[p]

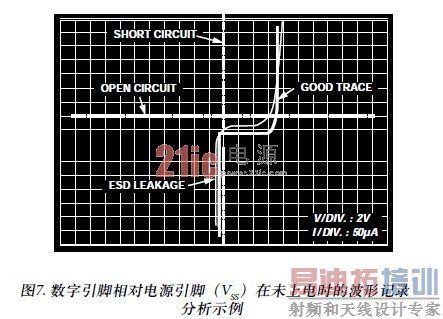

可以在相应位置上执行快速分析来评估器件是否受到过应力或可能遭受ESD事件。为了执行此分析,比较嫌疑器件和已知正常器件的引脚到引脚I/V结果,应使用波形记录器或类似设备。12位DAC的数字输入引脚(以VSS电源引脚为参考)上的一组典型短路、开路或ESD泄漏I/V迹线如图7所示。

闩锁

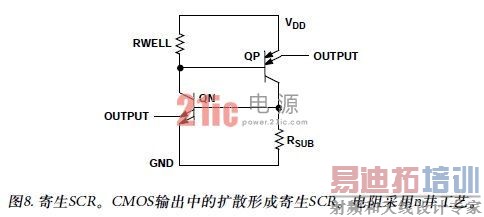

闩锁是一种潜在破坏性情况。这种情况会触发一个寄生有源元件,造成正负电源短路。如果电流不受限制,会发生电气过应力。闩锁的典型情况发生在CMOS输出器件中,两个寄生基-射结之一在过压事件期间暂时正向偏置时,驱动器晶体管和井形成pnpn SCR结构。SCR的开启本质上造成VDD和地之间的短路。

触发机制

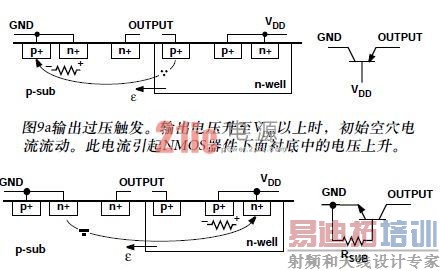

有两种主要触发机制。首先,如果输入/输出(I/O)引脚电压升至正电源电压以上,或降至负电源电压以下,寄生晶体管之一会开启。通过集电极返回电源的电流引起第二寄生晶体管的基极-发射极上的压降。然后,第二晶体管的集电极电流使第一晶体管的基极-发射极上保持正向偏置。如果两个晶体管增益之积大于单位增益,该条件可能自持续,并且甚至在消除外部电压之后仍持续存在。

如果在I/O引脚处存在过度电压过冲,或者如果在给器件供电之前有信号到达输入端,或者由于静电放电原因,便会发生此触发机制。此闩锁一般限于直接连接到引脚的元件。

图9b电流倍增。衬底电压上升主动将第二个寄生晶体管偏置为导通。然后,电子电流在n井里引起压降,进一步开启第一个晶体管。如果电流增益之积大于1,电源之间的最终电流可以自持续,仅受内部电阻(即,SCR)限制。

虽然触发是由过压事件(一般只是在电源电压之上或之下一个二极管压降)引起,行业惯例是根据在内部寄生电阻上产生出足以维持闩锁条件的压降之前引脚在过压条件下能耐受的过电流量(源电流或吸电流)对I/O进行分类。一般认为能耐受100 mA已足够,若能耐受200 mA则认为该器件不受闩锁影响。

第二种触发机制是在电源电压升至足以击穿一个内部结的条件下发生,可将电流注入前述SCR中。此触发机制可由电源瞬态或由旁路到一条供电轨的静电放电引起。与I/O触发情况不同,闩锁可发生在管芯的任何地方,并不限于外部电源连接或I/O引脚附近。

对电源过压的耐受性通常受制造器件的加工工艺限制,可查阅数据手册的“绝对最大额定值”规格。如果超过此额定值,可能发生永久EOS损害。使器件工作在接近最大额定值可能会降低器件的长期可靠性。同样,电气规格仅适用于数据手册上规定的电源,超出这些额定值范围将不予保证。

设计规则

以下是所有使用CMOS和Bipolar-CMOS IC的设计人员需要遵守的一组规则:

1. 在任何时候都不允许数字输入和输出超过VDD 0.3 V以上。这包括VDD = 0 V时的关断情况。

2. 亦不允许数字输入和输出降至低于DGND –0.3 V以上。

3. 对于混合信号器件,不允许DGND超过AGND 0.3 V。

4. 对于CMOS或Bipolar-CMOS DAC,一般不允许IOUT降至低于AGND 0.3 V以上。部分DAC可容许较大IOUT电流,无任何闩锁危险。 [p]

闩锁预防技术

在所有的CMOS和Bipolar-CMOS IC应用中,如果违反了一条或多条上述规则,一般应采取以下建议:

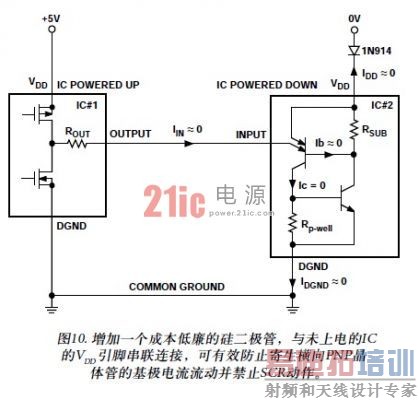

1. 如果任何时候器件的数字输入或输出会超过VDD,使用与VDD串联连接的二极管(如1N914)将防止SCR动作及随后的闩锁。这样做起作用的原因是二极管可防止寄生横向PNP晶体管的基极电流流出VDD引脚,从而防止

SCR触发。这如图10所示。如果认为上电时序是故障机制,二极管也是一种可靠的解决方案。这种情况下,在逻辑输入和VDD供电轨(二极管的阳极连接到逻辑输入)之间插入一个肖特基二极管将确保逻辑输入不超出VDD电源0.3 V以上,从而防止器件发生闩锁。

但是,此规则的一个例外情况是,器件的输入范围超出器件的电源电压范围时,例如(通过设计12位A/D子系

统AD7893-10),输入范围为±10V,电源电压为+5 V。

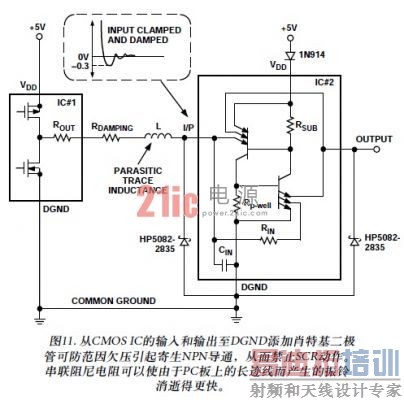

2. 如果任何时候器件的数字输入和输出会降至DGND以下,将一个肖特基二极管(如HP5082-2835)从这些输入

或输出连接到DGND会将负偏移有效箝位于–0.3V至–0.4V。这会防止寄生NPN晶体管的射-基结开启,还会

防止SCR触发。图11所示为肖特基二极管的连接。

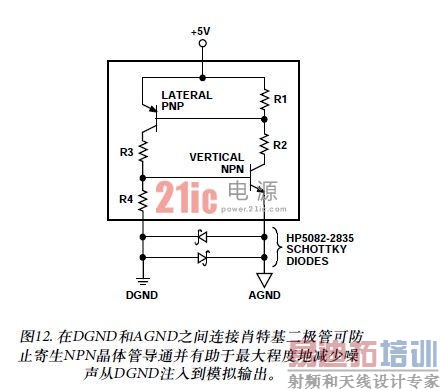

3. 如果DGND电位会偶尔地超出AGND 0.3V以上,位于器件两个引脚之间的肖特基二极管将防止相关寄生NPN

晶体管导通。这提供额外的闩锁保护,如图12所示。将额外二极管与刚刚提及的二极管反向并联可在另一方

向上提供DGND至AGND的箝位并将有助于最大程度地减少数字噪声注入IC。

为了识别上面(2)、(3)点中描述的过压和欠压,建议使用存储示波器,并将其每个引脚设置为最大额定值规格。将示波器的Time/Div.设置为最小设置(最好在ns范围内)。此项测试的进行时间应较长,例如整夜。

4. 在CMOS IC的IOUT引脚可拉至AGND以下的电路中,Iout引脚和AGND两端之间的肖特基二极管箝位可防止敏感IC的闩锁。这种情况有时会发生在DAC后面用作电流-电压转换器的高速双极性运算放大器。在上电或掉电转换期间,运算放大器的反相输入呈现从IOUT至负供电轨的低阻抗。不使用推荐的肖特基二极体箝位至AGND的无保护的DAC可能会出故障。

5. 如果设计中在PC板上的器件间具有较长的数字迹线并因此容易发生电感振铃问题,使用10 –100 的串联阻

尼电阻会比较有帮助。此电阻增加等效串联RLC网络的阻尼系数并使振铃衰减得更快。这将有助于防止输入

或输出保护二极管导通。

高电压瞬态

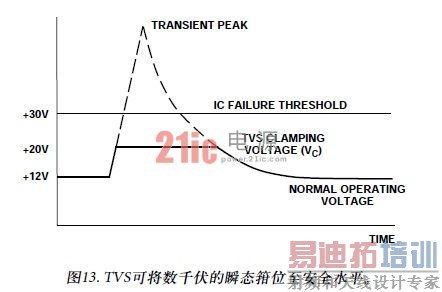

如果认为电源过压是故障机制,可靠的解决方案是插入一个TransZorb*瞬态电压抑制器(TVS)。什么是TVS及其工作原理如何

瞬态电压抑制器6(TVS)是用于保护易受干扰电路免受电气过应力(如由ESD、感性负载开关和闪电导致的线路瞬态造成的电气过应力)影响的器件。在TVS内,破坏性的电压尖峰会受可靠的硅pn结的箝位或雪崩动作限制,该pn结将瞬态的幅度减低至无损水平。

在一个电路中,TVS应“不可见”除非瞬态出现。击穿电压(VBR)、待机(泄漏)电流(ID)和电容等电气参数应不影响正常电路性能。 [p]

为了限制待机电流并允许TVS的温度系数所引起的VBR变化,TVS击穿电压一般比反向截止电压(VR)高10%,这接近于电路的绝对最大工作电压。瞬态发生时,TVS即刻箝位以将尖峰电压限制在一个安全的水平,即箝位电压(VC),同时将潜在破坏性电流导离受保护器件。

TVS是设计、规定并测试用于瞬态电压保护的,而齐纳二极管设计并规定用于电压调整的。因此,针对瞬态保护,应选择TVS而非齐纳二极管。

TVS的浪涌功率和浪涌电流能力与其结面积成正比。硅TVS系列的浪涌额定值通常按给定波形期间峰值脉冲功率(PP)的千瓦值规定。早期的器件采用10/1000 μs波形(10 μs升至峰值和1000 μs指数式衰减至一半峰值)规定,而最新的器件规定采用8/20μs测试波形。额定功率范围从5 kW(10/1000μs)降至400 W(8/20 μs)。此功率由TVS上的峰值电压与传导通过器件的峰值电流之积计算得出。

TVS提供电路工作电压从5V至376 V递增的各种系列。由于可用的额定电压和功率范围较宽(以及瞬态电压的普遍存在),TVS被用于各种电路和应用。

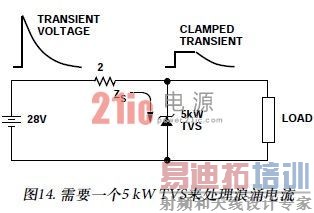

例如,考虑将工作电压为28 V的压力传感器置于会遭遇140V峰值的瞬态电压的环境中,源阻抗为2,持续时间为10/1000 μs。该传感器的故障阈值为40 V,因此,TVS必须箝位在40 V或更低。此瞬态输出的电流为:

I = (140 V – 40 V)/2 = 50 A

注意,TVS的电压箝位动作会造成一个分压器,通过该分压器,瞬态的开路电压出现在源阻抗和TVS器件的组合上。因此,瞬态电压减去TVS箝位电压,得到一个100V的净源电压。当与瞬态峰值电压相比,箝位电压较高时,电流显著降低。

此电路可采用一个额定功率5 kW的TransZorb TVS进行保护,该TVS可轻松承受浪涌电流。

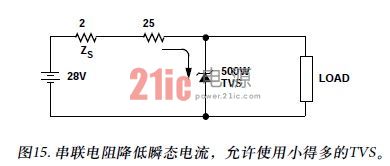

另一种更经济的替代方法是增加一个串联电阻来有效增加源阻抗,从而限制浪涌电流,如图15所示。因为传感器在正常工作条件下消耗的电流较小(典型值小于20 mA),所以性能不受电源电流降低的影响而变差。

对于10 mA的较小负载电流,增加的电阻上的压降很低,对于一个25 的电阻约为250 mV。增加此电阻可将浪涌电流降低至:

I = (140 V – 40 V)/(2 + 25 ) = 3.7A

这低于不使用该电阻情况的浪涌电流的十分之一。功率额定值较低的TVS就能够处理这个电流。这种情况下,500W抑制器可取代5 kW器件,节省了板空间和成本。

由于能耗性能,此应用建议采用碳质电阻。该电阻的稳态功耗(V×I)为2.5 mW,只需额定功率最低的电阻就有足够的裕量。

典型TVS应用

直流线路应用

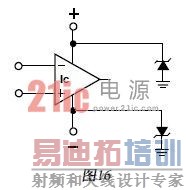

电源线上的TransZorb TVS防止瞬态、电源反相或电源开关切换期间造成的IC故障(图16)。

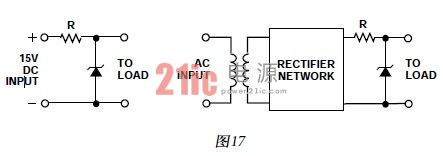

对于采用TransZorb TVS的电源,需选择反向截止电压等于或大于直流输出电压的TransZorb TVS。对于这类应用,可能需要用一个电感来取代串联电阻(R)(图17)。 [p]

信号线路应用

输入引脚易受到低能量、高电压静电放电或传输到信号线的串扰影响。箝位二极管或IC基板内的输入网络可提供有限保护(图18)。

线路上发生的瞬态在持续时间上可从几微妙至数毫秒变化,幅度可高达10,000 V。过电流流过二极管会造成一个开路条件或缓慢降低电路性能。位于信号线路上的TransZorbTVS可吸收此过剩能量(图19)。

欲进一步了解有关使用TransZorb保护电路的问题,请参见ADI公司应用笔记AN-311《如何切实有效地保护CMOS电路不受电源过压影响》。

小结

设计能够最大限度保护集成电路的应用非常具有挑战性,其解决方案取决于许多因素。下面简单总结了本应用笔记所讨论的保护方案:

1. 应就EOS/ESD损害预防对人员进行合理操作技术培训。

2. 应采用良好的设施接地系统,包括设备和数据线路屏蔽。

3. 审慎使用瞬态抑制器,即检查电源线路和接地线路上是否存在可能超出这些引脚最大额定值的尖峰。

4. 查看器件的上电时序是否适当。正确的顺序一般应为:GND、主电源(如可能,首先是基板电源)、VCC、

VREF+/–和所有其他引脚。

5. 查看数据手册,尤其是最大额定值部分。

应对同批次中可能受到错误测试或遭受与任何故障器件一样条件的其余器件进行评估,以确定是否可能存在潜在损害。应该执行此项分析是因为过应力条件的存在可能不会立即造成故障,但其引起的微小损害会导致长期可靠性问题。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:线性电源与开关电源的区别

下一篇:开关电源IC中误差放大器的自激振荡及解决方法