- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

大功率VDMOS(200V)的设计研究

功率MOS场效应晶体管是新一代电力电子开关器件,在微电子工艺基础上实现电力设备高功率大电流的要求。自从垂直导电双扩散VDMOS(VerticalDou-ble-diff used Metal Oxide Semiconductor)新结构诞生以来,电力MOSFET得到了迅速发展。本文分别从管芯的静态参数设计方面,介绍了VMDOS(200 V)设计的方法以及仿真的结果,并对流片结果进行了比较。

1 芯片设计

1.1 芯片设计思路设计

高压的VDMOS器件,希望得到高的耐压容量,低的特征导通电阻。降低导通电阻的方法主要是:减薄外延厚度、降低外延层电阻率、增加栅长LG、降低P-body的结深(xp+wo);而高的耐压容量要求:增加外延层厚度、增加外延电阻率、减小橱长LG,P-body的结深对耐压的影响取决于P-body间距的减小和外延耗尽厚度的减薄哪个因素对耐压的影响更大。高压VDMOS的静态参数优化设计主要矛盾集中在外延的选择、栅长及P-body的结深的确定上。

1.2 VDMOS耐压的设计

使半导体器件耐压受到限制的电击穿有雪崩击穿与隧道击穿2种,隧道击穿主要发生在耐压小于7 V的低压器件中。在这里只讨论高压器件所涉及到的雪崩击穿。计算雪崩击穿的公式:

αeff=1.8×10-35E7cm-1

式中:E以V/cm为单位。

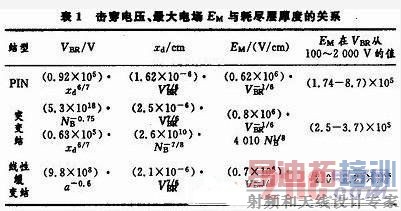

表1中列出了几种结的击穿电压、最大电场EM与耗尽层厚度的关系。

表1中:VBR的单位V,NB的单位为cm-3。NB对单边突变结代表轻掺杂区的杂质浓度,对双边突变结代表:

![]()

式中:NA及ND是两边的杂质浓度;a代表线性缓变结杂质浓度梯度单位为:cm-4。

当衬底杂质浓度NB低而a值大时,VBR过渡到最下方的斜线,与单边突变结一致;当NB高而a值小时,VBR与NB无关,这相当于线性缓变结的情形。

由于导通电阻随击穿电压猛烈增长,使得提高表面击穿电压在功率MOS中显得格外重要,因为若表面击穿电压低于体内很多,即等于此耐压的管子要以无谓增大导通电阻作牺牲来达到。为了提高表面击穿电压,功率MOS常用的终端技术有浮空场限环、场板等,有时还将这些技术结合起来使用,使表面击穿电压达到体内击穿电压的70 %~90%。

现代的终端技术已能使表面击穿电压达到体内理想一维电场分布的击穿电压的90%,在这种情况下,另一影响击穿电压的因素需要考虑,这就是每一个阱边角上的电场集中效应。当两个P阱之间距离很近时,边角电场出现峰值并不明显,击穿电压没有多大下降,但是P阱靠近则导通电阻也变大。由此可见,在这种情形下,高压器件的元胞图形对导通电阻又发生影响。计算表明方形阱最差,因为其角上为球面结,击穿最低。条状结构的P阱没有角,只有边,边上为圆柱结,击穿电压稍高,但条状结构有较高的导通电阻,仔细的研究结果表明,最优的结构是圆形元胞,而且两个P阱之间的距离应比由边缘电场决定的距离稍大。但是,圆形在制版过程和工艺对准方面有一定的困难,所以近似圆形的六角形成为最佳的选择。 [p]

1.3 阈值电压的设计

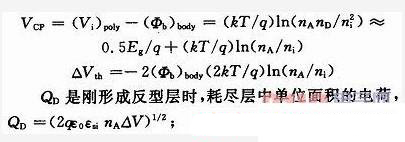

对于多晶硅栅的NMOS管,阈值电压可写作:

![]()

式中:Vcp是高浓度N+掺杂的多晶硅栅和P-body区的接触电势,△VTh是强反型下的表面势:

当达到和超出阈值电压时,△V=△Vth=(kT/q)ln(nA/ni);Qss是Si-SiO2界面杂质引入的电荷,通常它带负电。

1.4 导通电阻的设计

导通电阻Ron=Rcs+Rbs+Rch+Ra+Rj+Re+Rbd+Rcd。各部分的含义为:Rcs为源极引线与N+源区接触电阻,该电阻可通过适当的金属化工艺而使之忽略不计;Rbs源区串联电阻;Rch沟道电阻;Ra栅电极正下方N-区表面积累层电阻;RJ相邻两P阱间形成的J型管区电阻;Re高阻外延层的导通电阻;Rbd漏极N+层(即衬底)的导通电阻,由于此处杂质浓度较高,因此Rbd可忽略不计;Rcd为漏极接触电阻,其阻值较小,可忽略不计。

在200 V的器件中Rch起着主要作用:

![]()

理论上可以通过减小沟道长度或增加沟道内电子迁移率的办法来减小沟道电阻。但对于N沟道MOSFET器件,电子迁移率可近似看作常数,而沟道长度受到沟道穿通二次击穿的限制。目前通过增加沟道宽度即提高元胞密度是减小沟道电阻的主要方法。

1.5 参数的仿真结果

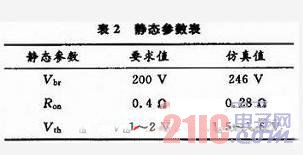

该器件用Tsuprem 4和Medici软件混合仿真。关键工艺参数为:外延厚度20μm,外延电阻率5Ω·cm;栅氧厚度52 nm(5+40+5 min);P阱注入剂量在3×1013cm-3,推阱时间为65 min。表2给出了静态参数表。

各参数仿真图如图1,图2所示。

1.6 结终端仿真结果

结终端结合自对准工艺,P等位和场限环的形成依靠多晶和场氧进行阻挡,利用多晶硅作为金属场板。使用了1个等位环和3个场限环,耐压可以达到242 V,仿真结果如图3~5所示。

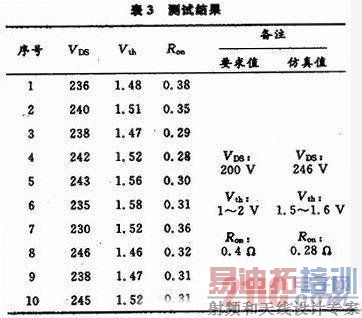

2 制造结果

在基于设计和封装控制的基础上,进行了样品的试制。采用的是TO-257的扁平封装。管芯试制样品后,对相关参数进行了测试,测试结果见表3所示。因为导通电阻是在封装之后测试,在封装后会引入一定的封装电阻,所以导通电阻比仿真时略有增大。随后对管芯进行了封装,试验产品出来后,发现有近一半产品的阈值电压有所缩小,有的甚至降到1V以下。出现这一问题,及时查找原因,发现烧结时间过长可能是阈值电压缩小的主要原因。由于本产品外形的特殊性,烧结时,每一船放的产品只数不能过多。而量少了,原来的烧结时间就显得过长。烧结时使用的是氢气保护,烧结时间长了,使氢离子在栅极上堆积,致使阈值电压下降。于是尝试着将烧结时间缩短,可是烧出来又出现了新的问题:很多产品的烧结焊料熔化不均匀,使芯片与底座烧结不牢,用探针一戳,就掉下来了。为了解决这一矛盾,反复试验将烧结时间用秒数来增减。最终达到在焊料完全均匀熔化的前提下,又使阈值电压不至于缩小。 [p]

3 结语

200V VDMOS器件的设计主要受到击穿电压和导通电阻两个参数的相互影响和相互制约,在设计中应优化两个参数的范圈。在满足其中一个的条件下使另一个达到最优的选择,采用仿真设计可大大减少设计成本。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...