- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

KAI-02150的CCD模拟前端采集电路设计

摘要 针对Kodak公司生产的CCD图像传感器KAI-02150,设计了双通道模拟前端采集电路。给出了电路的结构组成,根据KAI-02150的驱动和输出参数要求设计了各个模块的具体电路。通过SPI接口对AD9920A的寄存器进行配置,可以满足多种工作模式切换的需要。与传统的CCD模拟前端采集方案相比,文中的设计更加灵活简单、稳定可靠。测试表明,设计的输出驱动时钟满足KAI-02150的输入要求,可以驱动CCD输出模拟信号,并完成相关双采样和A/D转换得到数字视频信号。

关键词 KAI-02150;CCD;模拟前端采集;AD9920A

KAI-02150图像传感器是Kodak公司设计生产的全高清行间转移CCD(Charge-coupled Device),有效图像分辨率为1 920×1 080,支持四通道输出,图像最高输出帧率可达64fip·s-1,主要用于工业图像、医疗图像、安防监控等领域。

CCD的模拟前端采集电路设计主要用于对CCD提供水平和垂直驱动时钟信号,放大调理CCD输出的模拟信号,对CCD输出模拟信号进行模数转换,提供必要的帧和行的同步信号来进行数字视频信号的输出。所以CCD模拟前端采集电路的设计对于整个数字摄像机的最后成像质量起着重要的作用。一般如SONY公司针对所生产的CCD都提供了相应的前端采集电路的参考设计方案,但Kodak公司没有在技术文档中提供相关信息。文中针对KAI-02150的参数特点设计了双通道模拟前端采集电路,性能稳定可靠,模式设置方便灵活,减轻了软件设计的负担。

1 KAI-02150图像传感器芯片简介

Kodak公司生产的KAI-02150是一款1080p的2/3”大小的逐行扫描行间转移CCD传感器,其主要特征有:噪声低、动态范围宽、成像性能出色、信号读出结构灵活,支持1、2或者4通道信号同时采集,全分辨率图像最高采集速度可达64 fip·s-1。KAI-02150在水平时钟频率达到40 MHz时,其双通道输出帧率可以达到33 fip·s-1,完全满足普通安防监控的需要。

2 双通道模拟前端采集电路的设计

2.1 模拟前端采集电路总体设计思路

KAI-02150在进行光电转换的同时需要外部对其提供水平和垂直时钟等驱动信号,使得每个像素的模拟电压值进行串行输出。CCD信号采集处理芯片AD9920A可以在提供必要的水平和垂直时钟时序信号的同时对CCD模拟输出信号进行模数转换,并输出相应的视频同步信号。由于KAI-02150的驱动信号电平要求与AD9920A时序信号输出电平不相符,需设计时钟驱动电路对水平、垂直驱动与电子快门等信号进行电平的转换,同时起到隔离、缓冲、提高带负载能力等功能。在整个采集过程中,需要对AD9920A进行初始化和对采集到的双通道视频信号进行帧图像的合成和预处理,文中使用FPGA精确控制AD9920A的初始化和视频采集传输过程。

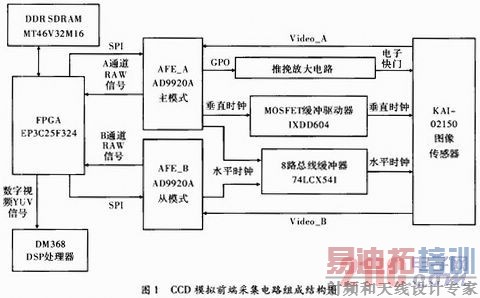

文中采用的模拟前端采集电路主要由CCD传感器、时序控制采集电路、时钟驱动电路组成,组成结构如图1所示。FPGA对模拟前端采集电路进行初始化并对采集到的视频进行预处理。 [p]

2.2 时序控制采集电路的设计

传统CCD时序控制采集电路主要由CPLD和相关双采样A/D芯片组成,垂直时钟由CPLD提供,而水平时钟和电荷复位时钟则由A/D芯片提供。为满足多种工作模式的切换,必须预存多种驱动时钟的输出样式,这样需要在CPLD中编写多种垂直时钟时序样式,大大增加了代码开发的工作量。此外传统方案外围电路复杂,驱动时钟信号源需要CPLD和A/D同时提供,在集成度、灵活性和稳定性上都有所欠缺。

文中采用两片Analog Device公司生产的AD9920A来进行精确的CCD时钟信号时序的输出和对CCD信号的进行A/D转换。AD9920A主要特点如下:12位40.5 MHz模数转换器;内置相关双采样控制电路;集成精确时序控制器;支持24路可编程垂直时钟信号输出。由于所有驱动时钟和复位信号均由AD9920A提供,与传统方案相比,文中采用的方案可以通过SPI接口配置AD9920A自身寄存器,预存多种时钟驱动样式,更加灵活方便地进行配置出多种摄像机工作模式,并且具有更高的稳定可靠性。

方案中所采用的两片AD9920A中一片工作在Master模式,用来提供CCD所需的水平垂直时钟、电荷复位信号和电子快门信号,并对通道A的CCD信号进行采集。另外一片工作在Slave模式,对通道B进行信号采集。工作在Master模式的AD9920A产生的HD和VD同步信号输入到Slave模式的AD9920A,以便同步CCD数字信号输出,在FPGA中双通道采集的图像可以得到还原。

2.3 时钟驱动电路的设计

KAI-02150的时钟驱动信号高低电平要求各不相同,前级AD9920A所提供的TTL时钟信号必须通过时钟驱动电路来进行电压转换,以符合CCD驱动电平的要求。

时钟驱动电路主要作用是为时钟信号提供直流偏置与增大时钟驱动能力。文中采用DC12V电压供电,由双通道DC/DC转换器LT3471得到16 V和-10 V电压,后经LDO稳压芯片LT1964和LT1761得到CCD垂直时钟所需的-9 V和12 V直流偏置电压。而水平时钟信号、复位信号和电子快门的直流偏置电压则主要由两片双极性D/A转换器AD5734R产生,后经LT1010电源缓冲器来提高电流输出能力。

前级Master模式的AD9920A输出的水平时钟信号与复位信号经74LCX541 8路三态CMOS缓冲器输入。为避免信号产生过多失真,在PCB布线时HL、H1、H2和RG走线的电感应非常低。为使互感最小,互补信号H1和H2的布线应尽可能对称并靠近。H5和H6信号也应如此。CCD对HL和H1至H6有很大的瞬变电流要求,因此使用较宽的PCB走线。

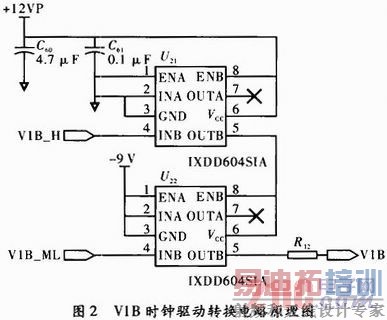

垂直时钟信号经IXDD604高速MOSFET驱动器输入到CCD,垂直时钟信号VIB有高中低3个电平状态。文中使用AD9920A输出的两个垂直时钟信号经过两片IXDD604来产生所需要的V1B时钟。如图2所示,当V1B_H为低时,U22的VCC为0 V,V1B可以根据V1B_ML输出中低电平。当V1B_H为高时,U22的VCC为12 V,保持V1B_ML为高使得V1B输出12V。

电子快门信号的直流偏置电压由AD5734R和LT1761提供,VSUB信号由AD9920A的GPO经过三极管推挽放大电路后产生。

[p]

3 AD9920A的寄存器相关设置

3.1 相关双采样控制与水平时钟时序设置

CCD理想的模拟信号输出波形如图3所示。图3(a)中,在时刻1,电荷复位信号RG清除输出电荷存储器中的电荷,在时刻2,输出电压为CCD复位噪声电平RSL,在时刻3,输出电荷存储器中的电荷转化为电压输出,输出电压为感光信号电平、复位噪声电平与暗参考电平的和SGL。使用相关双采样技术来对SGL与RSL的差值△V进行采样,得到感光信号电压值,并消除了复位噪声电平的影响。同时对暗参考电平进行采样,△V减去暗参考电平得到感光信号电平。

AD9920A中内置相关双采样电路,主要由寄存器SHPLOC和SHDLOC来控制RSL和SGL的采样时刻。SHP、SHD是通过将主时钟周期分为64个边沿时刻,相对于寄存器值被映射到4个象限中,每个象限包含了16个边沿时刻。而数据输出DATACLK相位可以通过DOUTPHASE寄存器进行编程,可以设置从0~63的任何时刻。通过配置0x38地址的寄存器来设置SHPLOC和SHDLOC的值,从而对应了RSL和SGL在一个像素周期中的采集时刻。为使切换噪声最小,应将DOUTPHASE寄存器设置为与SHP采样位置相同的边沿,或者设置为SHP采样位置之后最多11个边沿时刻,不应处于SHD采样位置与SHD位置之后的11个边沿之间。

在每个CCD感光器件的周围都有一些不感光的区间,这些就是暗像素区。通过AD9920A寄存器设置,将CLPOB使能在这些区间。当CLPOB使能后,AD9920A内部的电路就会自动计算出这些暗参考电平的平均值。最终AD9920A输出的数据是减掉暗参考电平后的有效值。暗像素参考电平采样位置取决于CCD,对于KAI-02150,取行首的前20个暗像素来计算暗参考电平。

3.2 水平垂直时钟时序设置

CCD水平时钟时序的设置主要是对Master模式的AD9920A的寄存器0x30~0x34进行配置,从而确定H1、H2、HL、RG在一个像素周期内上升沿和下降沿的位置。进一步设置寄存器0x36和0x37来配置AD9920A的水平时钟输出的驱动电流强度。

AD9920A的垂直时钟时序设置比较灵活,通过预设多组V-Pattern、V-Sequence、Field寄存器可以组合出多种工作模式。在摄像机工作时,只需修改Mode寄存器就可以在多种工作模式间进行切换。根据KAI-02150的Datasheet提供的垂直时钟时序图所示,CCD最后一行像素输出所需垂直时钟和其他行不同。所以对工作在Master模式的AD9920A设置了2组V-Pattern寄存器、2组V-Sequence寄存器,并根据需要设置了3组Field寄存器,来获得3种工作模式。

3.3 电子快门设置

文中采用AD9920A的GPO04作为CCD的电子快门信号。AD9920A的GPO04既可以作为普通I/O口使用,又可以和片内XSUBCK信号相连而作为XSUBCK输出。通过配置0x8E、0x8F、0x90寄存器的值,来控制电子曝光时间的长短。

4 实验测试结果

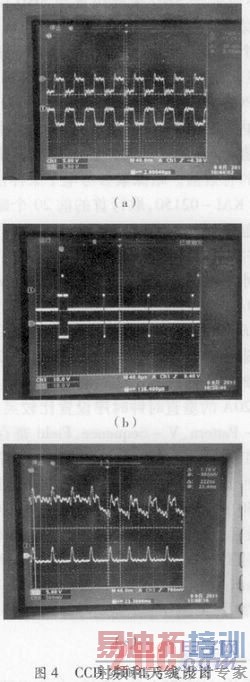

通过后级FPGA按照AD9920A的Datasheet上提供的上电顺序进行寄存器配置,AD9920A就可以输出采集到的BAYER阵列格式的数字视频信号。经过一系列的调试后,保证CCD水平垂直驱动时钟信号、电荷复位信号、电子快门信号均符合KAI-02150的参数需求,获得数字高清图像。示波器采集到的主要信号波形如图5所示,其中,图4(a)是水平驱动时钟,上方是H1Sa,下方是H2Sa;图4(b)是垂直驱动时钟,上方是V1B,下方是V3B;图4(c)是CCD输出的模拟信号与RG复位信号,上方是Video_A,下方是RG_a;最终通过后级DSP处理模块网络输出到上位机的图像如图5所示。

[p]

[p]

5 结束语

文中针对Kodak公司的KAI-02150设计了完整的CCD双通道模拟前端采集电路。相对于传统的CPLD与CDS&A/D转换器的设计方案相比,采用两片AD9920A的设计方案更加灵活可靠,可以满足更多工作模式切换的需要。通过FPGA对一主一从两片AD9920A进行寄存器配置,经过时钟驱动电路的调理,输出满足KAI-02150时序要求的驱动信号,驱动KAI-02150输出模拟视频信号。最后通过AD9920A的相关双采样、可变增益和模数转换输出数字视频信号。经过上位机处理得到图像,验证了整个硬件设计方案和AD9920A寄存器配置的正确性。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...