- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

浅谈低压差线性稳压器的拓扑结构与应用

1 低压差线性稳压器的发展现状及应用领域

随着现代科技的进步,便携式电子产品正朝着高效节能、短小轻薄的方向发展。而传统的集成线性稳压器的输入/输出压差较高,这就大大限制了它在低压供电领域中的应用。LDO 是一种线性稳压器。线性稳压器使用在其线性区域内运行的晶体管或 FET,从应用的输入电压中减去超额的电压,产生经过调节的输出电压。所谓压降电压,是指稳压器将输出电压维持在其额定值上下 100mV 之内所需的输入电压与输出电压差额的最小值。正输出电压的LDO(低压降)稳压器通常使用功率晶体管(也称为传递设备)作为 PNP。这种晶体管允许饱和,所以稳压器可以有一个非常低的压降电压,通常为 200mV 左右;与之相比,使用 NPN 复合电源晶体管的传统线性稳压器的压降为 2V 左右。负输出 LDO 使用 NPN 作为它的传递设备,其运行模式与正输出 LDO 的 PNP设备类似。更新的发展使用 MOS 功率晶体管,它能够提供最低的压降电压。使用 功率MOS,通过稳压器的唯一电压压降是电源设备负载电流的 ON 电阻造成的。如果负载较小,这种方式产生的压降只有几十毫伏。

近年来问世的低压差线性稳压器,它一经问世便显示出强大的生命力,并以低功耗、高效率、低噪声、高抗扰、体积小、重量轻等显着优点,LDO是low dropout regulator,意为低压差线性稳压器,是相对于传统的线性稳压器来说的。传统的线性稳压器,如78xx系列的芯片都要求输入电压要比输出电压高出2v~3V以上,否则就不能正常工作。但是在一些情况下,这样的条件显然是太苛刻了,如5v转3.3v,输入与输出的压差只有1.7v,显然是不满足条件的。针对这种情况,才有了LDO类的电源转换芯片。由PNP型驱动管和NPN型调整管构成的准低压差稳压器(QLDO,Quasi Low Dropout Linear Regulator);由导通电阻非常低的功率场效应晶体管构成的超低压差线性稳压器(VLDO,Very Low Dropout Linear Regulator)。

低压差线性稳压器特别适合采用电池供电的便携式电子产品,如笔记本电脑、手机、MP3播放器、数码相机、数码摄录像机、数字视频光盘(DVD)、可视电话、全球定位系统(GPS)、机顶盒(STB)、便携式仪表、汽车电子设备等。

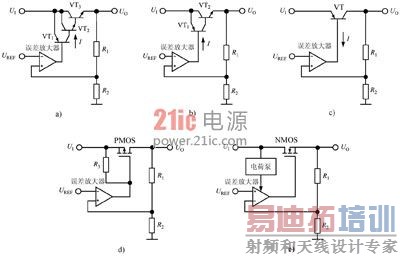

图1 线性稳压器的5种拓扑结构

a)传统的NPN型稳压器 b)准低压差线性稳压器(QLDO) c)低压差线性稳压器(LDO) d)PMOS超低压差线性稳压器 e)NMOS超低压差线性稳压器

2 线性稳压器的拓扑结构

近几年来,随着半导体技术的发展,表面贴装的电感器、电容器、以及高集成度的电源控制芯片的成本不断降低,体积越来越小。由于出现了导通电阻很小的MOSFET可以输出很大功率,因而不需要外部的大功率FET。例如对于3V的输入电压,利用芯片上的NFET可以得到5V/2A的输出。其次,对于中小功率的应用,可以使用成本低小型封装。另外,如果开关频率提高到1MHz,还能够降低成本、可以使用尺寸较小的电感器和电容器。有些新器件还增加许多新功能,如软启动、限流、PFM或者PWM方式选择等。

线性稳压器的5种拓扑结构如图1所示。a图为传统的NPN型线性稳压器,其输入/输出压差超过2.5~3V,I为驱动电流(下同)。b图为准低压差线性稳压器(QLDO),其压差可减小到0.9~1.5V。c图为PNP型低压差线性稳压器(LDO),其压差仅为0.3~0.6V。d图为由P沟道MOS管构成的PMOS超低压差线性稳压器(VLDO),其压差可降至100mV左右。e图为由N沟道MOS管构成的NMOS VLDO,其压差可低至几十毫伏。

上述5种线性稳压器的压差计算公式见附表1。

3 低压差线性稳压器的主要特点

低压差线性稳压器的主要特点是可最大限度地降低调整管压降,从而大大减小了输入-输出压差,使稳压器能在输入电压略高于额定输出电压的条件下工作。例如,传统的线性稳压器7805或LM317,要求输入电压必须比输出电压高出2.5~3V才能正常工作。为获得+5V输出,就需要+8V的输入电压。与之相比,新型低压差稳压器的输入电压只需高于+5.3V,即可获得+5V输出。从电源效率上看,LM317工作在+3.3V、1A时的效率低于50%。

低压差线性稳压器与开关稳压器相比,主要有以下6个优点:①稳压性能好;②低噪声(可达几十个微伏,无开关噪声)、低纹波(电源抑制比可达60~70dB),这对于无线电和通信设备至关重要;③低静态电流(超βLDO的静态电流可低至几微安至几十微安),低功耗,当输入电压与输出电压接近时可达到很高的效率;④具有快速响应能力,能对负载及输入电压的变化做出快速反应;⑤外围电路简单(仅用两只电容器),使用方便;⑥成本低廉。

低压差线性稳压器与其他稳压器的性能比较见表2。

低压差线性稳压器的应用

低压差线性稳压器的基本应用有以下5种。

1 交流供电的低压差线性稳压器

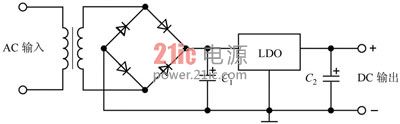

采用交流供电的低压差线性稳压器电路如图2所示。交流输入电压首先经过电源变压器降压,再通过整流滤波器送至低压差线性稳压器(LDO),最后获得直流稳压输出。

图2 采用交流供电的低压差线性稳压器电路

2 采用电池供电的低压差线性稳压器

采用电池供电的低压差线性稳压器电路如图3所示。低压差线性稳压器在采用电池供电时更具有明显的优势。

图3 采用电池供电的低压差线性稳压器电路

3 开关电源的后置线性稳压器

开关电源的后置线性稳压器电路如图4所示。开关电源以电源效率高而着称,但其输出噪声和纹波较大。将线性稳压器接在开关稳压器后面构成的复合式稳压电源,兼有开关电源和线性稳压电源的优点,不仅电源效率很高,而且稳压性能好,输出噪声极低,可获得纯净的直流输出电压。 [p]

图4 开关电源的后置线性稳压器电路

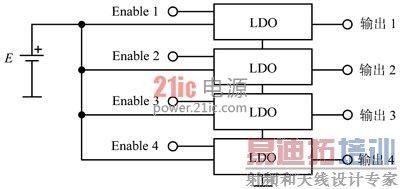

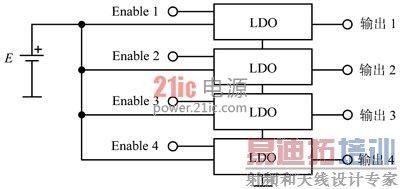

4 多路输出式低压差线性稳压器

多路输出式低压差线性稳压器电路如图5所示,利用4个使能端(Enable 1~Enable 4)可分别控制各路稳压输出的通、断。通信系统中各子系统的模块通常是由各自的稳压器供电的,即使它们采用相同的电源电压。

图5 多路输出式低压差线性稳压器电路

5 低压差线性稳压器在微处理器电源系统中的应用

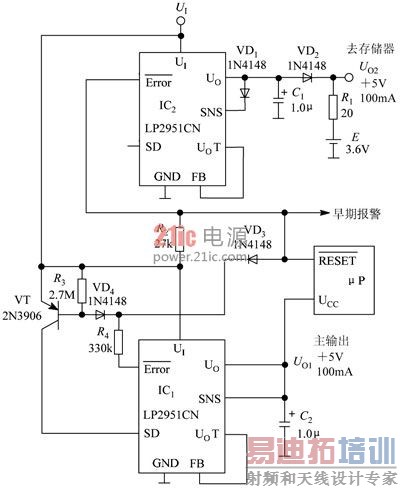

LP2951是SIipex公司推出的低压差线性稳压器系列产品,其最高输入电压为30V,最大输出电流为100mA。固定输出式的输出电压有 3种规格:+5.0V、+3.0V和+3.3V。它具有静态电流小(仅为75μA)、输出电压精度高(±0.5%)、电压调整率及负载调整率高(可达±0.05%),低压差(满载输出时的压降为380mV)、低温度系数(20×10-6/℃)等优点。

图6 由两片LP2951CN构成的微处理器电源检测及辅助输出电路

由两片LP2951CN(IC1、IC2)构成的微处理器电源检测及辅助输出电路如图6所示。LP2951CN的输出电压为 +5V。IC1为主电源,UO1为主输出,给μP供电。IC2为辅助电源,UO2为辅助输出,可作为存储器的备用电源并给镍镉蓄电池(NiCad)充电。LP2951CN的SNS(SNSES)为检测端,UOT接内部取样电阻分压器的抽头,FB为反馈端。

低压差线性稳压器使用注意事项

● 使用低压差线性稳压器时不得超过芯片的最高输入电压(UIM)、最大功耗(PDM)、最高结温(TjM)等极限参数值。最大功耗PDM=(UIM-UO)IOM。一般讲,芯片的封装尺寸越小,功耗越低。

● 输入电压必须大于预期的输出电压与输入-输出压差之和,即UI>UO+ΔU,否则低压差线性稳压器无法正常工作。

● 为延长电池使用寿命,应选择相对于负载电流而言,静态电流IQ较小的LDO。例如,为使IQ只增加0.02%的电池消耗,在100mA负载电流的情况下,采用IQ=200μA的VLDO比较合理。某些器件是在室温条件下规定的,或只提供IQ与温度关系的典型曲线。必要时可实测IQ值。

● 输出电压的精度亦称允许偏差。线性稳压器的输出电压精度一般不超过额定值的±5%。对大多数应用而言,该精度已经足够了。

● 由于输出电容是用来补偿LDO的,因此在选择输出电容器时应格外仔细。一般情况下,采用等效串联电阻(ESR)较低的大电容器,可提高电源抑制比,降低噪声电压并改善瞬态响应。但ESR过高或过低,也可能造成振荡。

● 手机、MP3、游戏机及多媒体PDA等便携式设备,适配300~500mA的LDO。为获得良好的音频质量,这种LDO在20Hz~20kHz的音频范围内应具有噪声电压低、电源抑制比(PSRR)很高的特性。

● 为满足精密电子设备的供电要求,应尽量减小LDO的输出噪声。LDO的输出噪声主要来源于基准电压电路,它所产生的噪声经过放大后送至输出端。影响LDO输出噪声的其他因素还有LDO内部放大器的极点、零点和输出极点,外部输出电容的容量、输出电容的等效串联电阻(ESR)及负载值。

● 在查阅LDO的产品资料时,应注意所给出精度指标是在室温下,还是在整个工作温度范围内,是满载条件下还是在中等负载或空载条件下。

● LDO有多种压差数据,应区分轻载、中等负载、满载条件下的压差最小值、典型值和最大值。满载条件下压差的最大值最具有实际意义,设计时应以此为依据,确保低压差线性稳压器在最坏的情况下仍能正常工作。

● 使用LDO时,需要装合适的散热器,以便将芯片内部产生的热量及时散发出去,避免因散热不良二导致管芯温度超过最高结温,使LDO无法正常工作,甚至损坏芯片。

● 由LDO构成PC主板电源时必须具有良好的瞬态响应,以利于推动高速变化的负载,确保输出电压保持稳定。

● 利用低压差线性稳压器专用设计软件(例如美国Micrel半导体公司开发的免费设计软件LDO-It),可实现LDO的优化设计。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:LDO低压差线性稳压器

下一篇:FPGA电源需求中三种供电要求解析方案