- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的OLED真彩色显示的实现

摘要 利用FPGA控制模块,设计了OLED真彩色动态图像驱动控制电路。介绍采用FPGA实现OLED外围控制电路和256级灰度的方法,并分析电路中模块的作用及整个电路的工作过程。电路系统采用基于Altera公司的FPCA技术进行设计,以Verlog HDL为描述语言,Modelsim仿真结果表明,该方案能够实现预定目标,实现480×RGB×640彩色OLED屏256级灰度显示。

关键词 OLED;FPGA;256级灰度;外围控制电路

作为第3代显示器,有机电致发光器件(Organic Light Emitting Diode,OLED)由于其主动发光、响应快、高亮度、全视角、直流低压驱动、全固态以及不易受环境影响等优异特性,具有LCD无法比拟的优点,在手机、个人电子助理(PDA)、数码相机、车载显示、笔记本电脑、壁挂电视以及军事领域都具有广阔的应用前景,因而得到了业界广泛的关注。OLED发展至今,已经由最初的单色发展到现在的全彩,与此同时对驱动电路也提出了更高的要求,由最初的无灰阶单色静态驱动,到彩色动态驱动。

目前,OLED的研究重点是研制高稳定性的器件以达到实用化的要求,但同时研究实现高质量动态显示的驱动技术也很重要,因为只有结合良好的驱动技术,提高反应速度和分辨率,才能表现出OLED的优异特点。然而,单色OLED显示就要求驱动电压具有较高的控制精度,彩色OLED显示如要同时精确地控制RGB三基色的灰度,实现起来难度更大。为实现真彩色,R、G、B三基色要各自实现256级灰阶。文中所述电路属于全彩色动态驱动电路,将对其256级灰度显示以及外围驱动进行研究与设计,为今后大尺寸OLED显示器提供一个可行的技术方案。

1 驱动控制系统设计

显示器性能的好坏,一方面取决于显示器的制作材料,另一方面取决于显示器的驱动电路系统。驱动电路系统是保证显示器正常工作必不可少的部分,对显示性能起着举足轻重的作用,驱动电路系统的不同会导致显示器显示色彩、亮度以及显示的灰度、响应时间、功耗等显示器参数。而OLED显示屏需要专用的控制驱动芯片,只有OLED屏与驱动控制芯片的成功结合,才能推动OLED的发展从而取代LCD。然而,目前国内外对OLED研究的热点主要在器件与材料上,关于驱动电路和灰度控制方面的研究相对较少,现有的OLED驱动电路集成度低,针对OLED特性的扫描效率优化度也不高。因此,设计高性能的OLED驱动电路,成为显示领域一个亟待解决的问题。文中在现有的研究基础上,自行设计了分辨率为480×640彩色OLED屏外围驱动电路,并对256级灰度实现方法进行了优化,使其与OLED完美结合,从而进一步推动OLED向前发展。

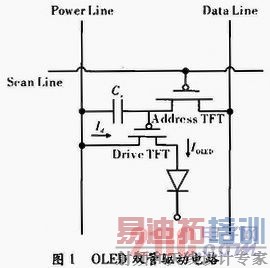

1.1 OLED像素单元电路

对于OLED驱动控制系统的实现,关键技术在于数据的写入和扫描控制,图1是单个像素的双管驱动电路。一个TFT用来寻址,另一个是电流调制晶体管,用来为OLED提供电流。为防止OLED开启电压的变化导致电流变化,使用的是P沟器件,这样,OLED处于驱动TFT的漏端,源电压与有机层上的电压无关。

[p]

Data Line与寻址TFT的源级相连,Scan Line使地址TFT选通,数据线上的内容通过漏电流写入到存储电容CS上,并以电荷的形式暂存。

当Power Line为高电平时,驱动TFT的源级为高电平,同时CS上的电荷,将选通驱动TFT,其漏电流流过OLED显示器件,驱动其发光。数据线电平的高低决定了像素的亮暗。

1.2 256级灰度显示

所谓图像的灰度等级就是指图像亮度深浅的层次,将基色的发光亮度按强度大小划分,就是灰度级。显示屏能产生的灰度级越高,显示的颜色和图像层次就越多。而且人的视觉系统对亮度强弱的感受不仅与亮度本身的强弱相关,还与发光时间和点亮面积有关,在一定时间范围内,点亮时间越长、面积越大,人眼感觉的发光强度就越强。因而利用人眼对快速的亮暗闪烁并不敏感的“暂留”效应,变换发光体的点亮时间和面积来区分亮度,就会形成一种不同灰度级画面的视觉,一般灰度级越高,所显示的颜色和图像层次就越多,图像越柔和,图像层次越逼真。高灰度级以及有效的灰度调制方式对高清晰度显示的发展极其重要,目前OLED显示驱动一个亟需解决的是灰度的精确性问题。

OLED显示屏是可以用传统的模拟电压控制法来实现灰度,问题在于:亮度和数据电压之间呈非线性关系,缺少一个渐变的易于控制的线性区间,因此,采用模拟电压法调节发光强度,难以精确、有效地实现OLED的灰度级显示,现在总的趋势是使用数字驱动电路。

数字驱动电路的困难在于工作频率比模拟驱动电路高得多,现阶段较为实用的灰度调制方法主要有两种。一种是脉宽调制法,即对驱动脉冲实现占空比的控制;另一种方法是子场控制法,这种方法将发光时间按1:2:4:8:…划分为若干个子场,不同的子场导通组合,就能实现不同的灰度等级。但采用脉宽调制法,其时序复杂,要求显示屏有较高响应速度;而采用子场法要求驱动频率较高,对高灰度级的实现难度大。

考虑到帧频与OLED屏体显示效率的折中,使驱动电路工作频率在一个合理水平,在脉宽调制和子场原理的基础上,对这两种方法进行优化,256级灰度采用通过对图像数据按位分时显示的方法实现,即对输入的8 bit像素信号RGB,通过给每种颜色字节的不同位分配不同的显示时间达到灰度显示的目的,使每位的显示时间为128:64:32:16:8:4:2:1,利用其组合可以得到256级灰度显示所对应的子像素发光时间,实现视觉上的256级灰度即1 667万色显示,以实现高质量的显示画面。

为实现256级灰度,将一个像素点的扫描时间分成19个单位时间t,8 bit灰度数据q[7:0]从高位到低位所占的时间分别为8t,4t,2t,t,t,t,t,t。为使不同位显示时间成一定比例,从q[3]开始引入t/2的消影时间,q[2]引入t/4的消影时间,d[1]引入t/8的消影时间,d[0]引入t/16的消影时间,如图2所示,由控制电路产生消隐信号进行消隐。由此计算OLED屏亮度百分比λ=(8+4+2+1+1/2+1/4+1/8+1/16)/19=83.9%。

[p]

1.3 FPGA控制器

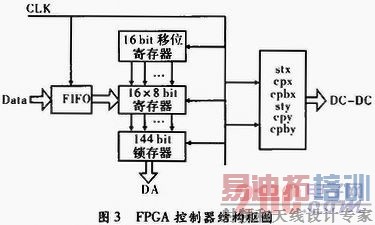

利用FPGA的处理速度和数据宽度高的优势以及芯片中可利用的丰富资源,为分辨率为480×RGB×640的OLED显示屏设计了外围驱动控制电路。其主要作用是向OLED显示屏提供扫描控制信号及进行OLED显示数据的数字信号处理。

根据OLED显示屏周边接口的结构和特性,利用FPGA芯片为其设计外围的驱动控制系统,为OLED屏提供控制信号以及传输所要显示的数据信号。

如图3所示,经解码后的图像数据存入FIFO(First In First Out)缓存中,在主时钟的控制下,FIFO中的图像数据将被载入到一个16×8的数据装载寄存器,当这16个8位数据装载寄存器装满时,将被一个144位的锁存器锁存,等待进入D/A转换模块;同时FPGA控制器还将在主时钟的控制下产生行列移位时钟和行列扫描起始脉冲,产生的时钟和脉冲进入DC-DC转换模块。

1.4 各种控制信号周期及频率

为使FPGA控制器能工作于一个合理的驱动频率以及提高显示屏的亮度,在结构上采用标准单元块的形式。对于分辨率480×3×640的显示屏,以8×16个显示像素灯管构成一个单元块,将480×3行分组组合成为90个块(Block),即每块由一组列信号同时驱动16行像素。设计列扫描驱动电路时,将640列电极分组组合成为80个块(Block),每个块并行驱动8列像素。

OLED显示屏的刷新频率是60 HZ/s,即显示一帧图像的时间为1/60 s,设为T,所以,行扫描起始信号stx的周期T为16 667μs,占空比为1:90;因为OLED显示屏480×3行电极分组组合成为90个Block,所以每一块的选通时间为T/90,即185.185μs。而cpx和cpbx是一对反相不交叠的脉冲信号,占空比为50%,在脉冲信号的高电平和低电平时,都有一个Block行像素被选通,即在cpx和cpbx一个周期内有两个Block行像素被选通,所以行扫描驱动脉冲cpx和cpbx的周期为T/45,即370.370μs。

同理,OLED显示屏的列被分为80个Block,每个列Block的选通时间为2.315μs,列扫描起始信号sty的周期为185.1 85μs,占空比为1:80。列驱动脉冲cpy和cpby亦是一对反相不交叠的脉冲信号,占空比为50%,在脉冲信号的高电平和低电平时,都有一个Block被选通。由于每个列Block的选通时间为2.315μs,所以列扫描驱动脉冲cpy和cpby的周期为4.630 μs。

在每个列Block选通期间,从FIFO中并行读出的8个8 bit数据进入数据锁存器锁存。在每个BLOCK选通期间都将进行一次数据的锁存,所以数据锁存信号Lock的周期为2.315μs。因为当16个8位的数据装载寄存器都载满数据的时候才进行这144个数据的锁存,所以16位移位寄存器时钟clk_reg的周期为0.145μs。从FIFO中读出数据的速度必须和向数据装载寄存器中装载数据的速度一致,则FIFO的读时钟clk_fifo的周期也为0.145μs。对0.15μs(6.896 MHz)进行近似为7 MHz,所以令系统的基本时钟为14 MHz,由FPGA外部晶振产生。读时钟为基本时钟的二分频。

1.5 FPGA工作流程

FPGA处理器是设计的核心部分,其工作流程为,在每个clk_fifo时钟周期下,从8个FIFO缓存中并行读出8个8 bit像素数据,在时钟clk_reg上升沿到来时,16位移位寄存器发生移位,它的输出端接16个8位数据装载寄存器的片选端,这样16个8位数据装载寄存器逐个被选通,此时这些数据就可以载入到16个8位数据装载寄存器中,这16个8位寄存器的输出端接在144位锁存器的输入端上。16个时钟clk_reg上升沿过后,16个8位数据装载寄存器都将依次被装载满,此时数据锁存信号Lock到达,将144个数据锁存到144位数据锁存器中,然后这些数据进入到DA转换模块,转换成16路模拟量,送至OLED显示屏,完成一个Block数据的载入。

在列扫描驱动脉冲cpy和cpby的控制下,80个Block依次被选通,在每一Block被选通期间,都将进行一次144个数据的移位寄存和锁存,当80个Block都锁存完之后,一行数据的载入也就完成了。当第一行的80个Block数据显示完毕后,列扫描起始信号sty过来,又开始从第一列扫描,与此同时,在行扫描驱动脉冲cpx和cpbx的作用下,第二行像素被选通,所以,这时将进行第二行的1到80个Block的数据载入,以此类推,直到90行数据都显示完毕之后,行扫描起始信号stx到来,重新选通第一行,循环往复,一帧帧地显示数据。 [p]

2 仿真结果

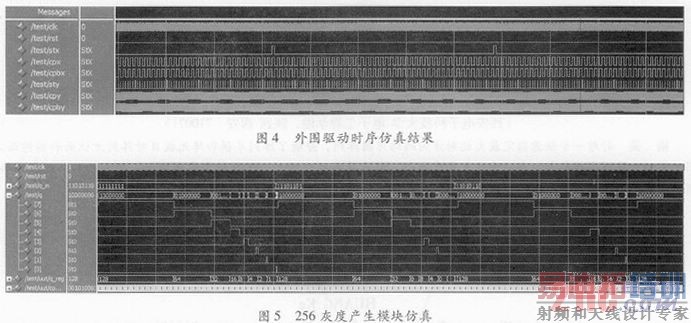

选用Altera公司CycloneⅢ系列芯片EP3C10E144C8为目标芯片,采用Verilog HDL语言进行设计,在GX-SOPC-EDA-EP3C10-STARTER-EDK开发板上进行Modelsim仿真,仿真结果如图4和图5所示。

由图4仿真结果可以看出,80组列扫描脉冲cpv和cpby控制80个Block,80个列扫描脉冲完毕后,列扫描起始信号sty脉冲开始,继续扫描下一行。90行扫描完毕后,stx到来重新选通第一行,依此循环,符合设计的要求。

由图5仿真结果可以看出,对于输入的8 bit像素数据,经灰度产生模块转化为灰度数据。以第一个输入数据8 hff为例,每位的显示时间为128:64:32:16:8:4:2:1,由其不同组合,从而实现了256级灰度的功能。

3 结束语

基于FPGA芯片设计了分辨率为480×RGB×640的真彩色OLED显示屏的驱动电路,在传统的子场原理和脉宽调制占空比实现灰度的基础上,对其进行优化,采用R、G、B单基色像素分时显示的方法,实现了256级灰度功能。经仿真和软硬件协同仿真验证,实现了设计所要求满足的功能。其256级灰度实现方法简单灵活,降低了对FPGA驱动频率的要求,对于在高刷率、高分辨率、高灰阶显示器件上的应用,具有很高的实用价值。利用该电路系统可以实现OLED显示的全彩色实时动态图像的传输,为今后OLED作为大尺寸显示器提供了技术支持。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:X86主板原理

设计经验及总结

下一篇:RS-422/485隔离技术及应用讨论