- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

理解并降低dc/dc开关式转换器的接地噪声

dc/dc开关式电源转换器的物理干扰众人皆知,除非系统和电路图都经过了精心设计。这些转换器会对电气地注入多余的电荷,产生虚假的数字信号、翻转的双倍时钟、电磁干扰、模拟电压误差,还可能是有害的高电压。随着这类设计复杂性的增加以及应用的密集使用,物理电路的实现已开始在系统的电气完整性中扮演一个重要的角色。为解决这些问题,你需要了解如何减少两类主要的地噪声源。

地噪声问题一

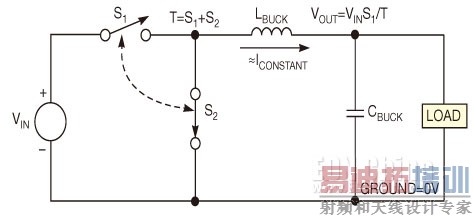

图1是一个有恒定负载电流的理想降压转换器。开关S1和S2作来回转换,斩断着降压电感和降压电容上的输入电压。电感电流或电容电压都不能突然地改变,而负载电流是恒定的。所有开关电压与电流应分别成功地跨过降压电感,或通过降压电容,因为一个理想的降压转换器不会产生地噪声。但有经验的设计者知道,降压转换器是一个臭名昭著的噪声源。这意味着,图1中的电路缺少了一些关键的物理元件。

图1,在一个降压转换器电路中,电感器的电流不能瞬时改变,因此难以判断一个理想降压转换器中的地弹跳来源。

无论何时,只要有电荷移动,就会产生一个磁场。一根导线、一只电阻、一只晶体管、一个超导体,或一个电容极板间的电流都会产生磁场。磁通量是通过一个电流环路面积的磁感应强度,它等于以直角切割环路面积的磁感应强度与环路面积的乘积:φB=B×A,其中φB是磁通量,B是磁感应强度,而A是电流环路面积。以某个距离环绕一根导线的磁感应强度与导线中的电流成正比,B=μoI/2πr,其中r为距离。

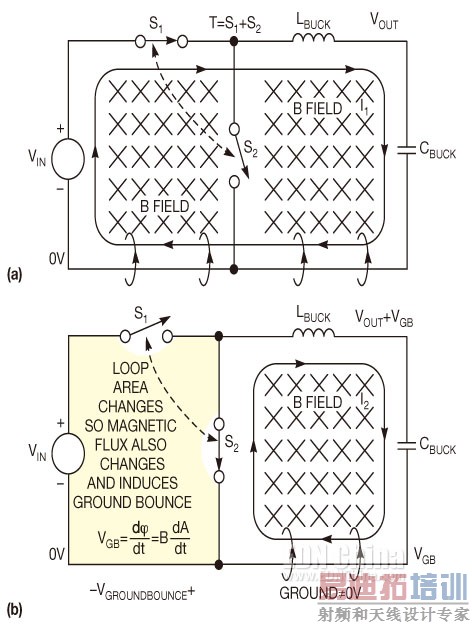

电子元件都有长度,电荷必须沿各个导线段,从一个器件移到另一个器件。移动的电荷就产生了一个磁场,于是我们可以改进图1中的电路。图2是一个简单降压转换器的更好模型。图2中,导线仍保持理想状态,不过电流在从一个电子元件移动到另一个元件时,必须在每段中流过一个距离。当这个电荷流动时,通过S1和S2开关的循环,磁场环绕着通电的导线,并有磁通通过。

图2,变化的磁通会产生电压(a)。当一个降压转换时,变化的电流回路路径产生一个变化的磁通,并导致地弹跳(b)。

S1和S2电流回路面积的变化是开关转换器地噪声的第一个主要来源。在每个开关周期中, 输入电压-S1-地这个回路中的磁通都会增加和衰减。这种变化的磁通会在该回路的各个地方感应出电压,包括理想的接地回路线。没有任何铜箔(哪怕是一个超导体)能够消除这种感应电压。唯一有用的方法是降低变化的磁通。

变化的磁通有三大要素:变化率、磁场强度和回路面积。由于时钟频率和最大输出电流可能有设计上的要求,因此尽量减小回路面积就成为最佳方法。感应系数与磁通量成正比。

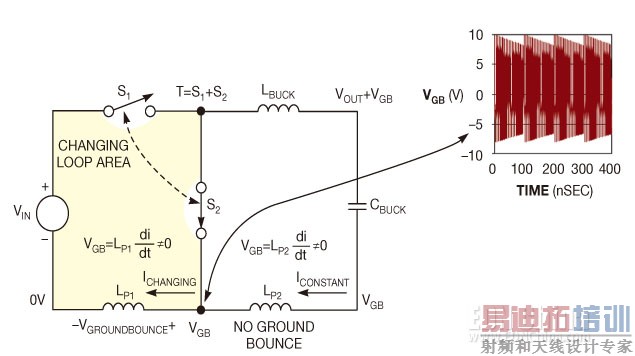

图3是图2的一个电气模型,其中寄生电感LP1中的电流变化产生了地噪声,而寄生电感LP2中的恒定电流则没有贡献。虽然图3以一种类似的方式表述了问题,但它是图2中物理增强模型的一个不良替代品。图3显示了LP1和 LP2上的寄生感应电压,而这种结构会在一个有磁通变化的回路各处都感应出电压。不过,这个电路部件仍能用于展示如何降低感应的地噪声。

图3,LP1中变化的电流产生了地弹跳,而LP2中的恒定电流则没有。

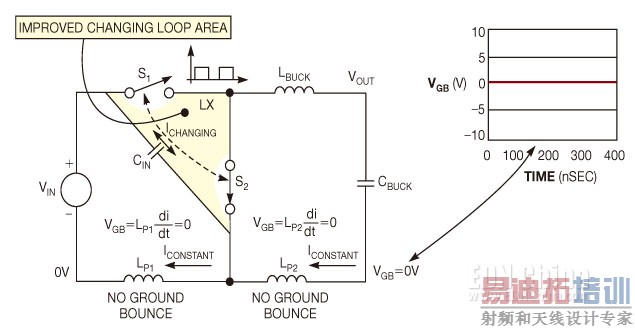

在图3中,地回路电流流过LP1并发生变化,它造成了一种电压弹跳问题。仔细布放输入电容可以减小寄生磁通面积,并让变化的降压电流走一个不包含在接地回路的路径(图4)。此时,寄生电感LP1和LP2中的电流是恒定的,因此地电压稳定不变。磁通面积的减小亦成比例地降低了EMI,以及所有其它有害的感应回路电压。

图4,仔细地布放输入电容,尽量减小变化回路的面积,并仔细地布放地回路的变化电流路径,可以消除地弹跳。

开关转换器接地噪声的第一个重要来源是磁通面积不断变化的结果。良好的PCB设计通过走线的布放和仔细布置的旁路电容,能尽量减少变化的电流回路面积,以及接地回路路径中变化的电流。

地噪声问题二

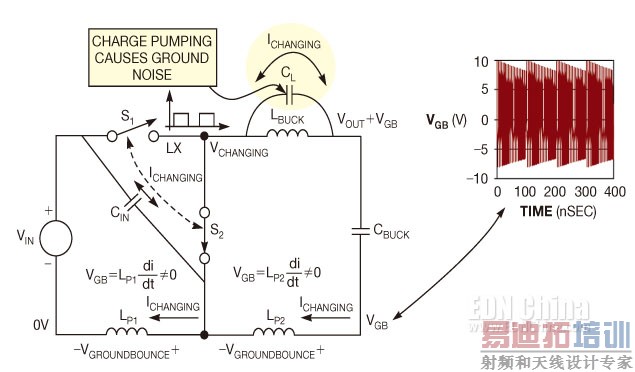

第二个地噪声的主要来源是寄生的电感器电容(图5)。一个电容上的电压不能够瞬时改变,而一个电感上的电流则不能瞬时改变。因此,LX结点上的电压变化就直接耦合到寄生降压电感器电容CL以及降压滤波器电容Cbuck,出现在寄生接地电感LP1和LP2上。

图5,LX结点电压的变化通过寄生降压电感器的电容CL将电荷泵出,并进入寄生接地路径电感器LP1和LP2,产生地噪声。

但开始是没有电荷流动的,在下一个瞬间,所有这些元件上都建立起电流,直到寄生降压电感器的电容能量ECL=1/2CLVLX2转换为导线的寄生磁场,ELP=1/2LPI2CHANGINGMAX,其中,LP是所有寄生回路电感的总和。然后,这个有害的能量在电场和磁场之间来回传送,直到辐射出去或耗散在阻性元件上。

地噪声振荡的峰值电压和持续时间都是问题。峰值电压在结点VGB测量,它是LX结点电压变化、寄生的降压电感器电容以及附加寄生走线电容的函数。一个大的寄生降压电感器的电容会存储更多能量,因此采用一个较小值是一个比较好的方案。选择了降压电感器的值以及额定电流后,要选择有最大自谐振频率的电感,以限制CL的容量。电感器的自谐振频率表示为1/[2π√(LBUCKCL)]。自谐振频率加倍可降低寄生的电感器电容,因而地噪声能量可降低至其四分之一。

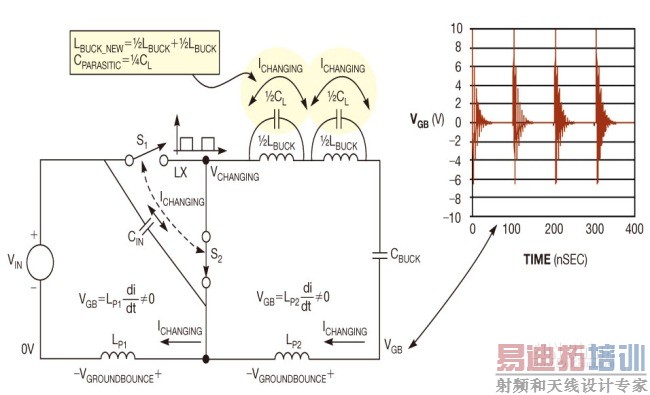

当性能优先于成本考虑时,用两只串联电感替换图5中的单只降压电感,每只电感的值是降压电感值的一半,而总电感值保持不变(图6)。对于制造厂的系列电感产品,寄生电容通常与额定电感值成正比,因此半值电感的寄生电容也只有一半。采用串联电感时,它们的电感值相加,而寄生电容值则是倒数值的和的倒数,从而降低了总的寄生电容。对于两个串联的半值电感,总电感值为LbuckNEW ,而总寄生电容将降低至降压电感器电容的四分之一。这样,降低的寄生电感就减少了地的弹跳。

图6,两个串联电感有相同的电感值,但寄生电容只有四分之一,泵出电荷及因此造成的地弹跳都得到减少。

通过研究各种模型,我们了解了地噪声的两个主要来源和机制,这两种地噪声在dc/dc开关转换器中无处不在,工程师可以在设计的早期阶段、元件选择以及布局时尽量降低这些效应,就能减少以后生产中的麻烦并避免从头设计。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:用一只三相整流器和降压器做离线单相电源

下一篇:X86主板原理

设计经验及总结