- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

DDR3 fly-by拓扑设计

录入:edatop.com 点击:

来源:汉普电子

随着数字存储设备数据传输速率越来越快,拓扑结构对于信号质量的影响越来越大,对于DDR3数据传输速率已经达到1600Mbps以上,设计采用fly-by拓扑结构,但是在使用的过程中我们需要注意一些问题,否则会带来严重的信号完整性和时序问题,导致设计跑不到想要的高速率。

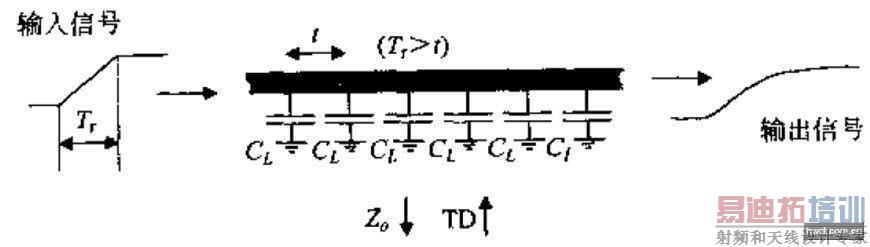

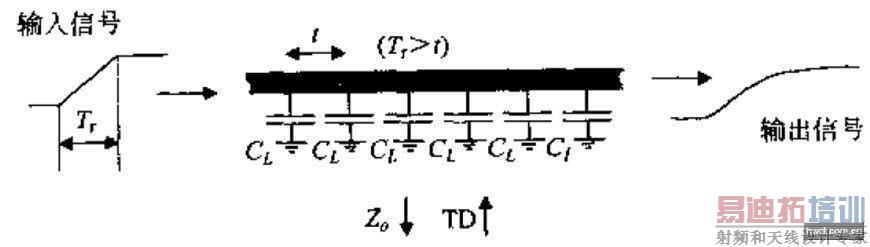

Fly-by拓扑要求stub走线很短,当stub走线相对于信号边沿变化率很短时,stub支线和负载就可以看作电容,该电容的大小为stub电容和硅片I/O电容的总和。当存储颗粒沿分支均匀分布,且各存储颗粒之间的电气时延相比于信号上升/下降时间较小时,stub和硅片引入的电容会显示出分布式效应,从而改变分支走线处的传输线特征阻抗和传播速度。下图描绘了传输线上若干抽头对应的分布式容性负载。对于容性负载均匀的总线,其等效阻抗由下面的公式计算

分布式容性负载的影响

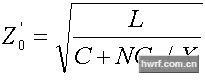

其中,L和C是分布式传输线的寄生效应,CL是负载的总电容,N是负载的数量,X是分布式负载对应的传输线长度,即分支长度。

从上面公式可以看出,负载引入的电容,实际被分摊到了走线上,所以造成走线的单位电容增加,从而降低了走线的有效阻抗。所以在设计中,我们应该将负载部分的走线设计为较高的阻抗,经过负载电容的平均后,负载部分的走线才会和主线段阻抗保持一致,从而达到阻抗连续,降低反射的效果。

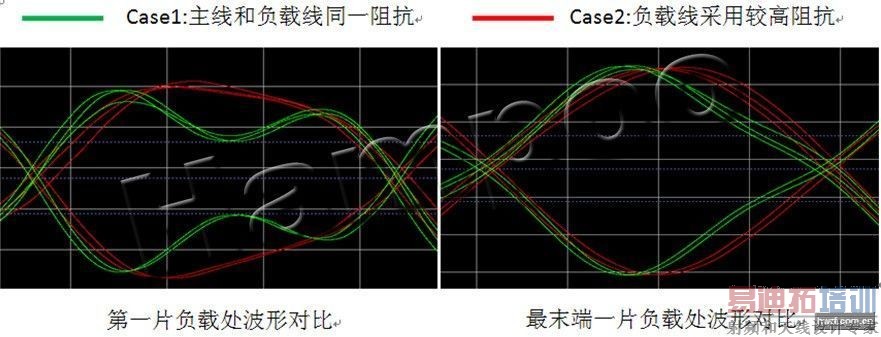

下面用Hampoo在实际中的一个DDR3设计案例,来分析对比采用高阻抗负载走线和采用主线和负载走线同阻抗两种情况的差异。

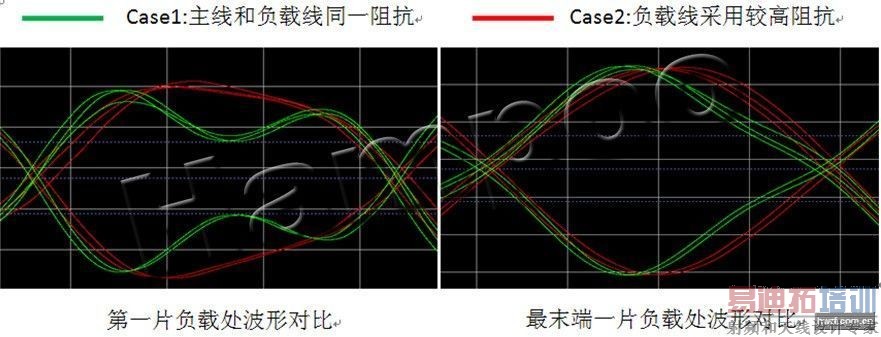

如上图,Case1采用的是从内层控制器到各个SDRAM均为50ohm的阻抗设计。Case2则采用了主线40ohm,负载线60ohm的设计。对此通过仿真工具进行对比分析。

从以上仿真波形可以看出,使用较高阻抗负载走线的Case2在信号质量上明显优于分支主线都采用同一种阻抗的Case1设计。而且对靠近驱动端的负载影响最大,远离驱动端的最末端的负载影响较小。这个正是前面所分析到的,负载的分布电容导致了负载线部分的阻抗降低,如果采用主线和负载线同阻抗设计,反而导致了阻抗不连续的发生。把负载走线设计为较高的阻抗,用于平衡负载引入的分布电容,从而可以达到整条走线阻抗平衡的目的。

通过提高负载走线阻抗来平衡负载电容的做法,其实在以往的菊花链设计中是经常用到的方法。DDR3称这种拓扑为fly-by,其实是有一定的含义的,意在强调负载stub走线足够的短。

负载的stub分支长度也会对走线造成很大的影响,如果分支太长,负载电容会表现出严重的反射效应,和输入信号叠加,导致情况变得复杂。此时已经不能简单的使用将负载电容平均到走线上的方式对电路作出分析了,这时需要借助仿真软件来评估这种长分支对信号的影响。以下为仿真结果对比。

从仿真结果可以看出,长负载分支的眼高、眼宽小于短负载分支的眼高、眼宽,主要就是由上面提到的负载电容反射造成。

针对DDR3 fly-by的设计,依据Hampoo在高速PCB领域的设计经验,我们给出以下设计参考:

1、负载走线阻抗要比主线阻抗高。建议主线阻抗控制到40-45ohm,负载走线阻抗控制到55-60ohm。

2、负载stub尽可能短。建议clock走线 stub<150mils,CTRL 走线stub<200mils,ADD/CMD走线 stub<260mils。来源:http://www.hampoo.com/know-how/detail/281

随着数字存储设备数据传输速率越来越快,拓扑结构对于信号质量的影响越来越大,对于DDR3数据传输速率已经达到1600Mbps以上,设计采用fly-by拓扑结构,但是在使用的过程中我们需要注意一些问题,否则会带来严重的信号完整性和时序问题,导致设计跑不到想要的高速率。

Fly-by拓扑要求stub走线很短,当stub走线相对于信号边沿变化率很短时,stub支线和负载就可以看作电容,该电容的大小为stub电容和硅片I/O电容的总和。当存储颗粒沿分支均匀分布,且各存储颗粒之间的电气时延相比于信号上升/下降时间较小时,stub和硅片引入的电容会显示出分布式效应,从而改变分支走线处的传输线特征阻抗和传播速度。下图描绘了传输线上若干抽头对应的分布式容性负载。对于容性负载均匀的总线,其等效阻抗由下面的公式计算

分布式容性负载的影响

其中,L和C是分布式传输线的寄生效应,CL是负载的总电容,N是负载的数量,X是分布式负载对应的传输线长度,即分支长度。

从上面公式可以看出,负载引入的电容,实际被分摊到了走线上,所以造成走线的单位电容增加,从而降低了走线的有效阻抗。所以在设计中,我们应该将负载部分的走线设计为较高的阻抗,经过负载电容的平均后,负载部分的走线才会和主线段阻抗保持一致,从而达到阻抗连续,降低反射的效果。

下面用Hampoo在实际中的一个DDR3设计案例,来分析对比采用高阻抗负载走线和采用主线和负载走线同阻抗两种情况的差异。

如上图,Case1采用的是从内层控制器到各个SDRAM均为50ohm的阻抗设计。Case2则采用了主线40ohm,负载线60ohm的设计。对此通过仿真工具进行对比分析。

从以上仿真波形可以看出,使用较高阻抗负载走线的Case2在信号质量上明显优于分支主线都采用同一种阻抗的Case1设计。而且对靠近驱动端的负载影响最大,远离驱动端的最末端的负载影响较小。这个正是前面所分析到的,负载的分布电容导致了负载线部分的阻抗降低,如果采用主线和负载线同阻抗设计,反而导致了阻抗不连续的发生。把负载走线设计为较高的阻抗,用于平衡负载引入的分布电容,从而可以达到整条走线阻抗平衡的目的。

通过提高负载走线阻抗来平衡负载电容的做法,其实在以往的菊花链设计中是经常用到的方法。DDR3称这种拓扑为fly-by,其实是有一定的含义的,意在强调负载stub走线足够的短。

负载的stub分支长度也会对走线造成很大的影响,如果分支太长,负载电容会表现出严重的反射效应,和输入信号叠加,导致情况变得复杂。此时已经不能简单的使用将负载电容平均到走线上的方式对电路作出分析了,这时需要借助仿真软件来评估这种长分支对信号的影响。以下为仿真结果对比。

从仿真结果可以看出,长负载分支的眼高、眼宽小于短负载分支的眼高、眼宽,主要就是由上面提到的负载电容反射造成。

针对DDR3 fly-by的设计,依据Hampoo在高速PCB领域的设计经验,我们给出以下设计参考:

1、负载走线阻抗要比主线阻抗高。建议主线阻抗控制到40-45ohm,负载走线阻抗控制到55-60ohm。

2、负载stub尽可能短。建议clock走线 stub<150mils,CTRL 走线stub<200mils,ADD/CMD走线 stub<260mils。来源:http://www.hampoo.com/know-how/detail/281

谢谢分享!

谢谢分享

有没有DDR入门级的学习资料发我一份www.xuescd@126.com 谢谢

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:CB板设计中电源走线的粗细如何选取?有什么规则吗?

下一篇:注意 高频信号布线

射频和天线工程师培训课程详情>>