- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

40G BASE-KR4背板设计案例

录入:edatop.com 点击:

汉普专稿

设计简介:

通信交换系统背板设计,系统由多块业务版、交换板以及背板组成,系统总线带宽40G,单线速度10.3125Gbps,长度高达25.7in,单板最高带宽达到640Gbps。整个系统基于ATCA背板架构,底层链路传输采用IEEE 802.3ba 40GBASE-KR4 / 10GBASE-KR标准。

背板PCB设计参数:

电路板设计相关芯片 CS4322 BCM5674 CN5010 RTL8211CL PEX8112 BCM5482 BCM5396 BCM54680 EPM570 XC6VLX240T NL101024, S19250

电路板设计相关标准及模块 ATCA , 40GBASE-KR4, 10GBASE-KR, CEI-6G-LR, CEI-6G-SR, RGMII,RMII, MDI, XUI, RXUI,DDR3-1600,DDR2-533,QDR-300,TCAM

SI仿真参数

信号速率:10.3125Gbps

最长走线:25.7in走线+2连接器+5过孔+1 AC电容

背板PCB设计难度:

信号速率高达10.315Gbps,信号需穿越业务板,背板,交换板,走线长度达到25.7in,并且需要经过以及两个连接器,和3-5个过孔,所以对走线的阻抗,过孔,连接器,板材的选取,工艺处理,背钻要求,有一项考虑不周,都会造成整个电路板设计的失败。本次在原有的10G信号设计经验上,对链路上的走线情况进行了进一步的优化分析,提高了PCB设计的性能,而且通过SI仿真技术的支持,保证了PCB设计的一次性成功。

背板PCB设计总结:

汉普的多次高速背板设计都是一次性成功,其中SI仿真发挥了很大的作用,汉普在高速链路建模、优化,板材选型与评估,误码率评估,抖动分析,串扰控制,眼图分析,DFE/FFE参数控制等多方面都积累了大量的经验,在单线10Gbps速率下的背板设计中早已驾轻就熟,PCB设计时间大大缩短,PCB设计的可靠性也越来越有保证,也为汉普向更高的PCB设计速率迈进奠定了基础。

客户反馈:

整个PCB设计经客户调试,各个模块均到达设计要求,10.3125Gbps高速链路部分更是一次性成功,客户给予很大的肯定。

设计展示:

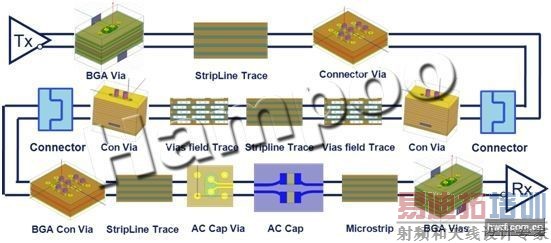

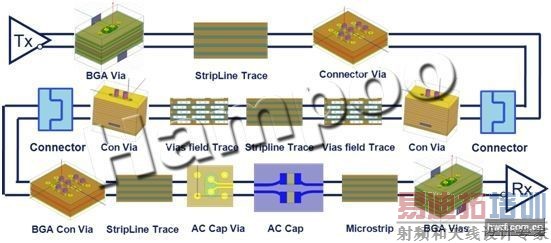

10GBASE-KR链路模型图:

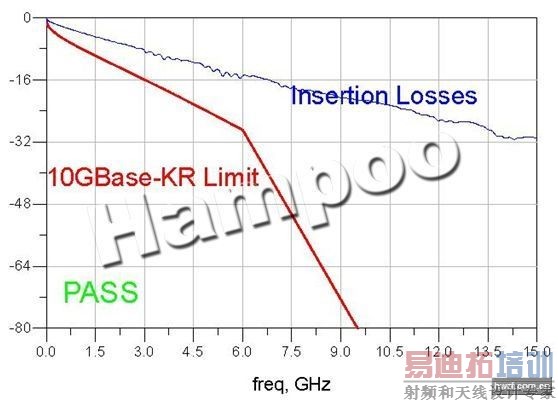

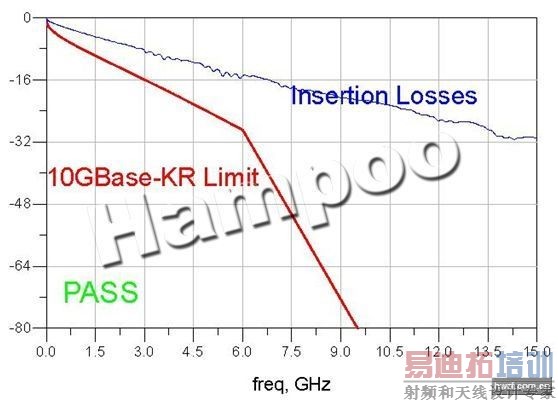

SI仿真优化后的系统最大损耗:

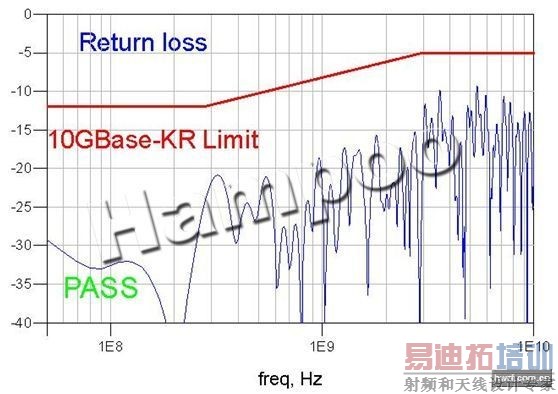

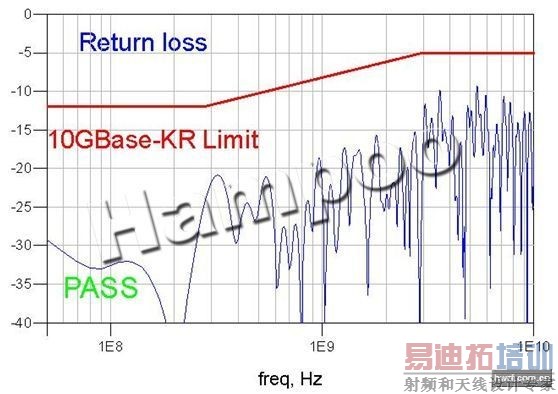

SI仿真优化后的系统回路损耗:

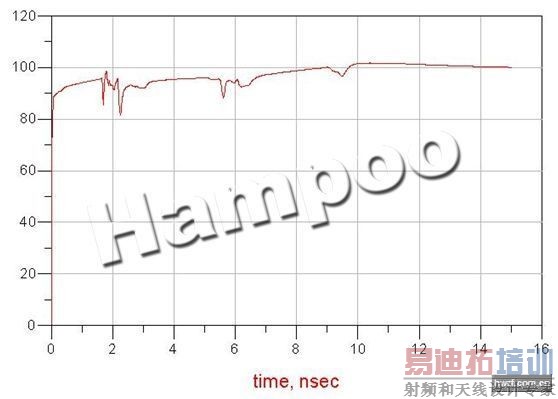

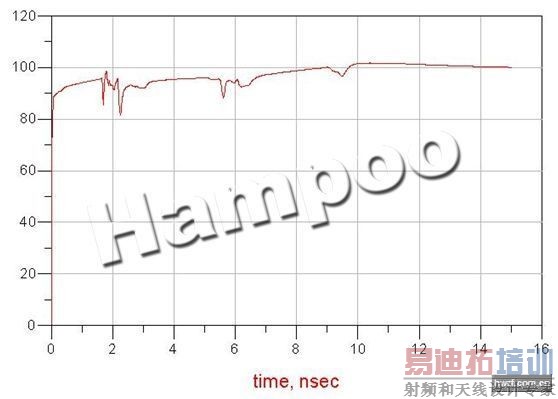

链路的TDR波形:

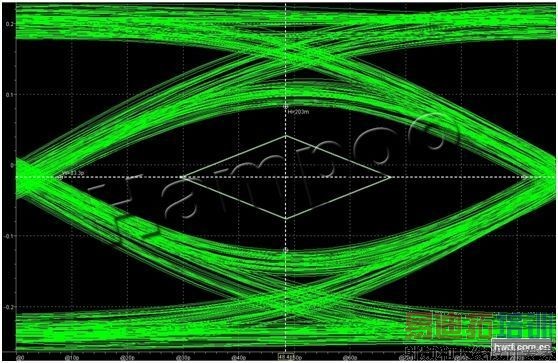

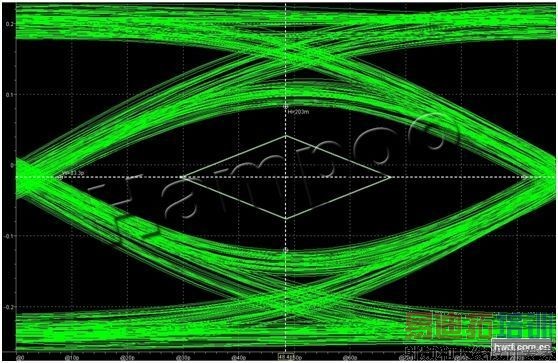

SI仿真眼图输出:

http://www.hampoo.com/cases/caseview/79

设计简介:

通信交换系统背板设计,系统由多块业务版、交换板以及背板组成,系统总线带宽40G,单线速度10.3125Gbps,长度高达25.7in,单板最高带宽达到640Gbps。整个系统基于ATCA背板架构,底层链路传输采用IEEE 802.3ba 40GBASE-KR4 / 10GBASE-KR标准。

背板PCB设计参数:

电路板设计相关芯片 CS4322 BCM5674 CN5010 RTL8211CL PEX8112 BCM5482 BCM5396 BCM54680 EPM570 XC6VLX240T NL101024, S19250

电路板设计相关标准及模块 ATCA , 40GBASE-KR4, 10GBASE-KR, CEI-6G-LR, CEI-6G-SR, RGMII,RMII, MDI, XUI, RXUI,DDR3-1600,DDR2-533,QDR-300,TCAM

SI仿真参数

信号速率:10.3125Gbps

最长走线:25.7in走线+2连接器+5过孔+1 AC电容

背板PCB设计难度:

信号速率高达10.315Gbps,信号需穿越业务板,背板,交换板,走线长度达到25.7in,并且需要经过以及两个连接器,和3-5个过孔,所以对走线的阻抗,过孔,连接器,板材的选取,工艺处理,背钻要求,有一项考虑不周,都会造成整个电路板设计的失败。本次在原有的10G信号设计经验上,对链路上的走线情况进行了进一步的优化分析,提高了PCB设计的性能,而且通过SI仿真技术的支持,保证了PCB设计的一次性成功。

背板PCB设计总结:

汉普的多次高速背板设计都是一次性成功,其中SI仿真发挥了很大的作用,汉普在高速链路建模、优化,板材选型与评估,误码率评估,抖动分析,串扰控制,眼图分析,DFE/FFE参数控制等多方面都积累了大量的经验,在单线10Gbps速率下的背板设计中早已驾轻就熟,PCB设计时间大大缩短,PCB设计的可靠性也越来越有保证,也为汉普向更高的PCB设计速率迈进奠定了基础。

客户反馈:

整个PCB设计经客户调试,各个模块均到达设计要求,10.3125Gbps高速链路部分更是一次性成功,客户给予很大的肯定。

设计展示:

10GBASE-KR链路模型图:

SI仿真优化后的系统最大损耗:

SI仿真优化后的系统回路损耗:

链路的TDR波形:

SI仿真眼图输出:

http://www.hampoo.com/cases/caseview/79

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

射频和天线工程师培训课程详情>>