- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

避开假八层的温柔陷阱----浅谈六层板的叠层

录入:edatop.com 点击:

作者:王辉东、吴均,一博科技高速先生团队队员

在《PCB的筋骨皮》一文中,我们提出了当板厚在1.6mm及以上时,怎样避免使用假八层的叠层,而导致PCB成本增加的问题。感觉大家的回答很踊跃哈,看来这个问题还是比较典型的。本来想截取一些回答放在这里,不过篇幅的关系,大家可以自己去上一篇文章,看看文章后面的精选答复。

在此文中我们结合平时的设计经验,提出了自己的见解,希望给大家一个答案,请大家指导分享。

1、 什么是假八层

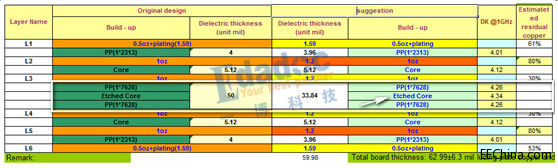

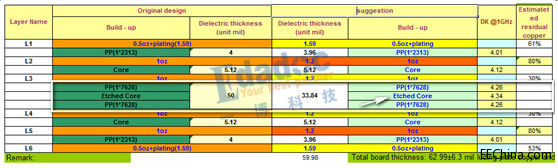

我们常规的六层板叠层,是L2-3一张芯板(core),L4-5(core)一张芯板,其它的用PP加铜箔,最后压合在一起而成的。如图一所示。

图一

但是六层板板厚在1.6mm及以上时,如果要进行常规阻抗控制(单线50欧姆,差分100欧姆),在层叠上会导致3、4层之间的厚度较高,超过3个7628半固化片的厚度。因大部分工厂PP最多只能叠3张(超过3张压合时,PP经高温由半固化状态转变成液态后容易从PNL板边流失)。这时候在生产上通常会用一个光板(没有铜皮的芯板或者把常规芯板两面的铜箔蚀刻掉)添加在3、4层之间来辅助达到预期的层叠厚度,这就是通常所说的假八层。其实那并不是真正的八层板,而是为了满足板子阻抗的需要,而出现的一种特殊叠层方式。比如下图六层板因阻抗或设计所限,中间多用了一张光板,两张芯板加一张光板,这本来是八层的叠构设计,实际做出来是六层的效果。这种就叫假八层板(实际是真六层板)。

当然这只是假八层其中的一种情况,如下图所示,3、4层之间用了2张7628半固化片加一个假芯板的方案,这个做法会增加成本。

图二

你注意到了吗?

图一用的是两张芯板(core),而图二中用的是三张芯板(core),成本有很大的差异。

那么我们怎样去避免这种情况的出现呢,我们推荐了以下几种做法,请大家参考借鉴。

2、 非高密时的解决方案

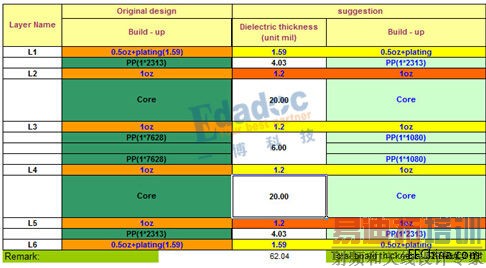

三个布线层方案

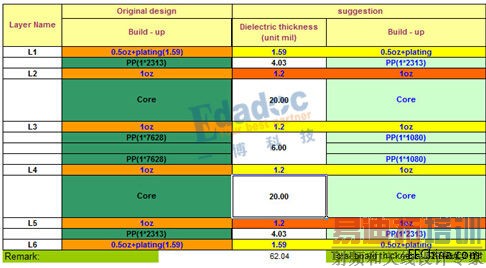

这个答案有人回复了:如果可以实现3个布线层完成设计,那么六层板完全可以设计成为常规层叠。或者关键信号线(高速信号)数量不多,区域集中,也可以使用这个层叠方案,局部高速信号区域对应的相邻层铺地铜,做成局部3层布线(L1&L4&L6)。叠层如下(阻抗计算从略,大家可以自己算算,后面也是一样只写层叠)

图三

缺点:关键信号多的情况下,三个层无法满足布线需求。

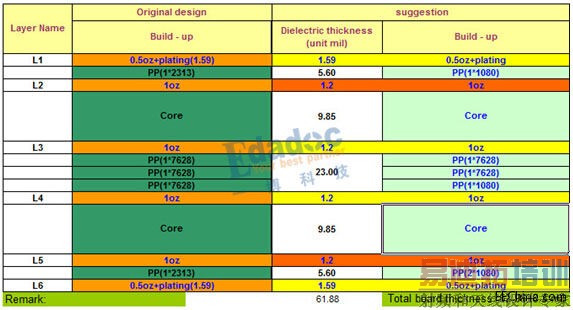

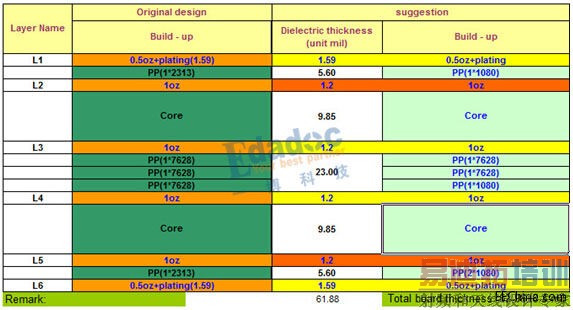

较宽线宽方案

板子的密度不高,没有小间距的器件,可以使用比较大的线宽进行设计的板子(比如8mil左右线宽)叠层和阻抗控制如下:

图四

缺点:以上层叠方案,阻抗线设计为表层8~9mil左右,内层6~10mil存在小间距器件时,以上方案比较难于布线。

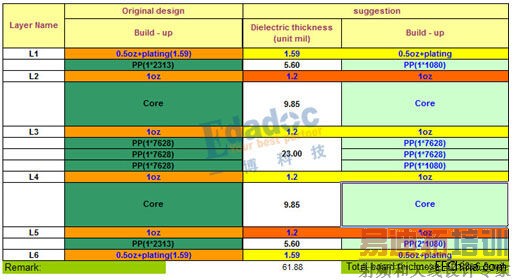

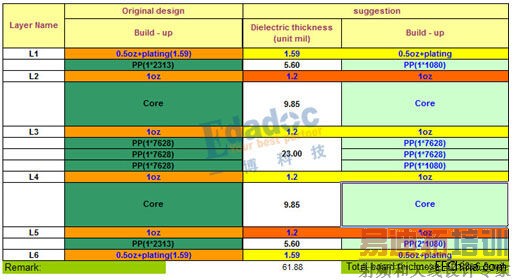

3、 非高速时的解决方案

在一些没什么高速信号,阻抗控制的要求可以稍微降低一点,比如保证各层阻抗一致,但是阻抗的中心值为60~65欧姆,差分线控制在105欧姆左右,叠层和阻抗控制如下:

图五

缺点:这个层叠方案有一定的技术风险,需要评估高速信号的反射。

(篇幅关系,提高阻抗的方案对高速信号的影响,会在后面的文章进行分析)

4、 总结

其他方案还有1、2,5、6作为布线层,3、4为电源地平面的方案,这个方案需要表层走线极短,只进行Fan out的设计,同时1、2之间,5、6之间的阻抗差距极大。

另外在设计时将阻抗设计成共面阻抗,此将叠层厚度调整厚,线宽加大,线到周围铜箔的间距调小也可以实现非假八层的方案来满足阻抗需求及降低成本。

当然,大家的回复里面还有其他方案:比如把板厚改成1.2mm,这需要考虑机械结构的要求,一般情况下无法实现。

其实,明眼人会说上面的所有方案都是有局限性的:

在《PCB的筋骨皮》一文中,我们提出了当板厚在1.6mm及以上时,怎样避免使用假八层的叠层,而导致PCB成本增加的问题。感觉大家的回答很踊跃哈,看来这个问题还是比较典型的。本来想截取一些回答放在这里,不过篇幅的关系,大家可以自己去上一篇文章,看看文章后面的精选答复。

在此文中我们结合平时的设计经验,提出了自己的见解,希望给大家一个答案,请大家指导分享。

1、 什么是假八层

我们常规的六层板叠层,是L2-3一张芯板(core),L4-5(core)一张芯板,其它的用PP加铜箔,最后压合在一起而成的。如图一所示。

图一

但是六层板板厚在1.6mm及以上时,如果要进行常规阻抗控制(单线50欧姆,差分100欧姆),在层叠上会导致3、4层之间的厚度较高,超过3个7628半固化片的厚度。因大部分工厂PP最多只能叠3张(超过3张压合时,PP经高温由半固化状态转变成液态后容易从PNL板边流失)。这时候在生产上通常会用一个光板(没有铜皮的芯板或者把常规芯板两面的铜箔蚀刻掉)添加在3、4层之间来辅助达到预期的层叠厚度,这就是通常所说的假八层。其实那并不是真正的八层板,而是为了满足板子阻抗的需要,而出现的一种特殊叠层方式。比如下图六层板因阻抗或设计所限,中间多用了一张光板,两张芯板加一张光板,这本来是八层的叠构设计,实际做出来是六层的效果。这种就叫假八层板(实际是真六层板)。

当然这只是假八层其中的一种情况,如下图所示,3、4层之间用了2张7628半固化片加一个假芯板的方案,这个做法会增加成本。

图二

你注意到了吗?

图一用的是两张芯板(core),而图二中用的是三张芯板(core),成本有很大的差异。

那么我们怎样去避免这种情况的出现呢,我们推荐了以下几种做法,请大家参考借鉴。

2、 非高密时的解决方案

三个布线层方案

这个答案有人回复了:如果可以实现3个布线层完成设计,那么六层板完全可以设计成为常规层叠。或者关键信号线(高速信号)数量不多,区域集中,也可以使用这个层叠方案,局部高速信号区域对应的相邻层铺地铜,做成局部3层布线(L1&L4&L6)。叠层如下(阻抗计算从略,大家可以自己算算,后面也是一样只写层叠)

图三

缺点:关键信号多的情况下,三个层无法满足布线需求。

较宽线宽方案

板子的密度不高,没有小间距的器件,可以使用比较大的线宽进行设计的板子(比如8mil左右线宽)叠层和阻抗控制如下:

图四

缺点:以上层叠方案,阻抗线设计为表层8~9mil左右,内层6~10mil存在小间距器件时,以上方案比较难于布线。

3、 非高速时的解决方案

在一些没什么高速信号,阻抗控制的要求可以稍微降低一点,比如保证各层阻抗一致,但是阻抗的中心值为60~65欧姆,差分线控制在105欧姆左右,叠层和阻抗控制如下:

图五

缺点:这个层叠方案有一定的技术风险,需要评估高速信号的反射。

(篇幅关系,提高阻抗的方案对高速信号的影响,会在后面的文章进行分析)

4、 总结

其他方案还有1、2,5、6作为布线层,3、4为电源地平面的方案,这个方案需要表层走线极短,只进行Fan out的设计,同时1、2之间,5、6之间的阻抗差距极大。

另外在设计时将阻抗设计成共面阻抗,此将叠层厚度调整厚,线宽加大,线到周围铜箔的间距调小也可以实现非假八层的方案来满足阻抗需求及降低成本。

当然,大家的回复里面还有其他方案:比如把板厚改成1.2mm,这需要考虑机械结构的要求,一般情况下无法实现。

其实,明眼人会说上面的所有方案都是有局限性的:

- 信号较杂乱,必须要4个布线层才能完成布线

- 有高密的BGA,无法走较宽的线

- 速率较高,DDR3/4,高速串行总线,控其他阻抗担心有风险

- ……

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:烧录BGA封装芯片时如何选择精密夹具?

下一篇:如何选择高频高速板材

射频和天线工程师培训课程详情>>