- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

快点PCB原创∣聚焦SI问题之匹配电路设计

本篇文档重点介绍常见信号匹配方式,匹配电路的设计是解决SI问题的重要手段,可以先了解通用的匹配电路方式,再逐步掌握比较复杂拓扑结构下的匹配电路设计。

匹配电路按照所处的位置分为:源端匹配(发送端)、终端匹配(接收端)

按照常见的电路形式分为:串联电阻、并联电阻、戴维南电路、AC电路、肖特基二极管 等。

1. 常见信号匹配电路

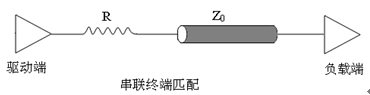

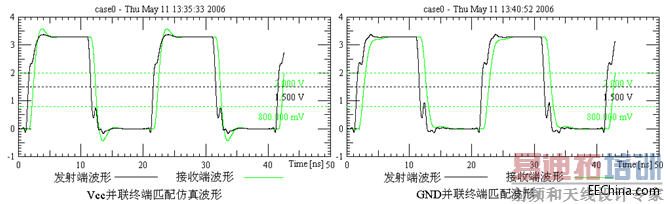

1.1 串联电阻匹配

串联电阻匹配通常用于源端(发送端),即在驱动器输出端和信号传输线之间串联一个电阻。驱动器输出阻抗R0以及电阻R值的和必须同信号线的特征阻抗Z0匹配。

对于这种类型的匹配电路,由于信号会在传输线、串联匹配电阻以及驱动器的阻抗之间实现信号电压的分配,因而加在信号传输线上的电压实际只有部分的信号电压。

而在终端(接收端),由于信号线阻抗和接收器阻抗的不匹配,通常情况下,接收器的输入阻抗更高,因而会导致大约同样幅度值信号的反射,称之为附加的信号波形。因而接收器会马上看到全部的信号电压(附加信号和反射信号之和),而附加的信号电压会向驱动端传递。然而不会出现进一步的信号反射,这是因为串联的匹配电阻在接收器端实现了反射信号的终端匹配。

串联电阻匹配的优点是在原有电路每一个驱动器仅增加了一个电阻元件,匹配电阻的功耗是最小的,因而驱动器不会增加任何额外的直流负载,也不会在信号线与地平面之间引入额外的阻抗。

对长走线进行串联电阻匹配后仿真波形如下,供参考:

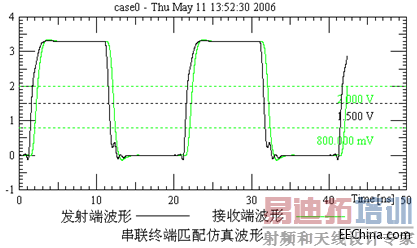

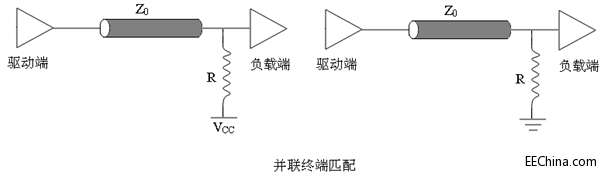

1.2 并联电阻匹配

并联电阻匹配通常用于终端(接收端),即通过一个电阻R将传输线的末端接到地或电源VCC上。电阻R的值必须同传输线的特征阻抗Z0匹配,以消除信号的反射。如果R同传输线的特征阻抗Z0匹配,不论匹配电压的值如何,终端匹配电阻将吸收形成信号反射的能量。并联电阻接到电源VCC可以提高驱动能力、接到地则可以提高电流的吸收能力。

并联电阻匹配的优点是设计和应用简便易行,在电路末端仅需要一个额外的元器件;缺点在于终端并联电阻会带来直流功率消耗。另外并联电阻匹配也会使信号的逻辑高输出电平的情况退化、从而降低了接收器对噪声的免疫能力。

对长走线进行并联电阻匹配后仿真波形如下,供参考:

1.3戴维南匹配

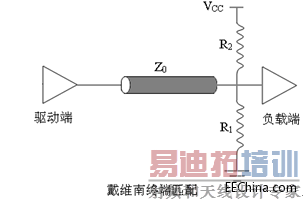

戴维南电路匹配技术也叫做双电阻匹配技术,通常用于终端(接收端)。

采用两个电阻来实现终端匹配,R1和R2的并联组合要求同信号线的特征阻抗Z0匹配。R1的作用是帮助驱动器更加容易地到达逻辑高状态,这通过从VCC向负载注入电流来实现。与此相类似,R2的作用是帮助驱动器更加容易地到达逻辑低状态,这通过R2向地释放电流来实现。

戴维南电路匹配的优势在于终端匹配电阻同时还作为上拉电阻和下拉电阻来使用,因而提高了系统的噪声容限。戴维南电路匹配通过向负载提供额外的电流从而有效地减轻了驱动器的负担,同时还可以有效地抑制信号过冲。

戴维南电路匹配的一个缺点是无论逻辑状态是高还是低,在VCC到地之间都会有一个常量的直流电流存在,因而会导致终端匹配电阻中有静态的直流功耗。

这种终端匹配技术同样也要求两个匹配电阻之间存在一定的比例关系,同时也存在额外的到电源和地的线路连接。负载电容和电阻(Z0、R1和R2的并联组合)会对信号的上升时间产生影响,提升驱动器的输出电压。

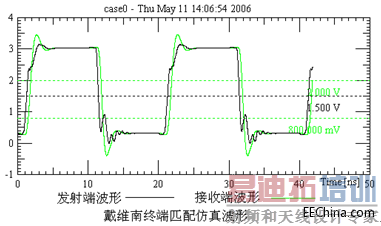

对长走线进行戴维南终端匹配后仿真波形如下,供参考:

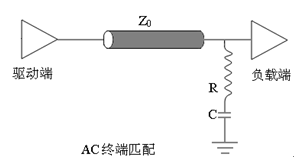

1.4 AC匹配

AC匹配也可称为RC终端匹配技术,由一个电阻R和一个电容C组成,电阻R和电容C连接在传输线的负载端。

电阻R的值必须同传输线的特征阻抗Z0的值匹配才能消除信号的反射,电容值的选择要注意与R值的配合、要确保RC时间常数大于该传输线负载延时的两倍。终端匹配元器件上的功率消耗是频率、信号占空比、以及过去数据位模式的函数。所有这些因素都将影响终端匹配电容的充电和放电特性,从而影响功率消耗。

AC匹配的优势在于终端匹配电容阻隔了直流通路,因此节省了可观的功率消耗,同时恰当地选取匹配电容的值,可以确保负载端的信号波形接近理想的方波,同时信号的过冲与下冲又都很小。

AC终端匹配技术的缺点是信号线上的数据可能出现时间上的抖动,这主要取决于在此之前的数据位模式。

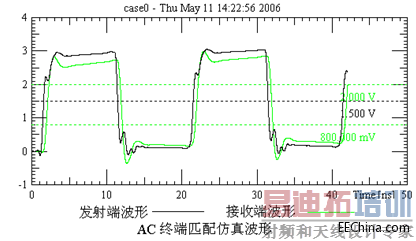

对长走线进行RC终端匹配后仿真波形如下,供参考:

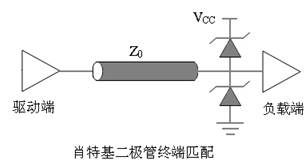

1.5 肖特基二极管匹配

肖特基二极管匹配也称之为二极管终端匹配技术,由两个肖特基二极管组成。传输线末端任何的信号反射,如果导致接收器输入端上的电压超过VCC和二极管的正向偏值电压,该二极管就会正向导通连接到VCC上。该二极管导通从而将信号的过冲箝位到VCC和二极管的阈值电压的和上。

同样连接到地上的二极管也可以将信号的下冲限制在二极管的正向偏置电压上。然而该二极管不会吸收任何的能量,而仅仅只是将能量导向电源或者是地。这种工作方式的结果是,传输线上就会出现多次的信号反射。信号的反射会逐渐衰减,主要是因为能量会通过二极管在电源和地之间实现能量的交换,以及传输线上的电阻性损耗。能量的损耗限制了信号反射的幅度,确保信号的完整性。

不同于传统的终端匹配技术,肖特基二极管终端匹配技术的优势是无须考虑真正意义上的匹配。所以,当传输线的特征阻抗Z0不清楚时,比较适合采用这种终端匹配技术。同时,在肖特基二极管上的动态导通电阻上消耗的功率远远小于任何电阻类型终端匹配技术的功率消耗。事实上,反射功率的一部分会通过正向偏置的二极管反馈回到VCC或者地,同样也可以在传输线上任何可能引发信号反射的位置加入肖特基二极管。二极管终端匹配技术的缺点是多次信号反射的存在可能会影响后续信号的行为。

2. 多负载拓扑电路的匹配设计

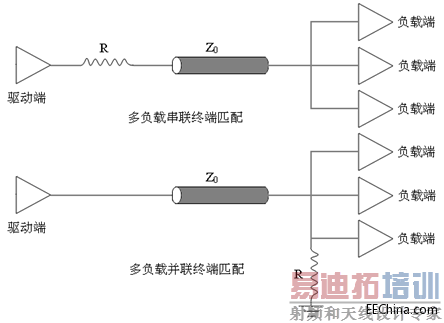

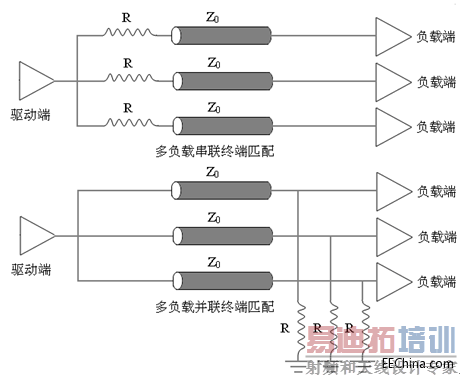

在实际电路中常常会遇到多负载拓扑总线电路结构,这时需要根据负载情况及电路的布线拓扑结构来确定端接方式和使用端接的数量。一般情况下可以考虑以下两种方案。

如果多个负载之间的距离较近,可通过一条传输线与驱动端连接,负载都位于这条传输线的终端,这时只需要一个端接电路。如采用串行电阻匹配,则在传输线源端按照阻抗匹配加入一串行电阻即可;如采用并行端接(以简单并行端接为例),则端接应置于离源端距离最远的负载处,同时,线网的拓扑结构应优先采用菊花链的连接方式,如下图所示:

如果多个负载之间的距离较远,需要通过多条传输线与驱动端连接,这时每个负载都需要一个端接电路。如采用串行端接,则在传输线源端每条传输线上均加入一串行电阻;如采用并行端接(以简单并行端接为例),则应在每一负载处都进行端接,下图所示:

多负载拓扑结构电路的匹配设计比较复杂,是否采用远端串联电阻还需要考虑信号的驱动能力和反射情况,根据具体PCB走线拓扑的情况,需要对终端并联匹配电阻的阻值进行选择,这通常通过电路信号仿真工具来进行。

在仿真工具中,搭建电路拓扑结构,仿真工具支持参数扫描模式,通过多种参数组合仿真、在其中选择最优的匹配设计方案。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...