- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速PCB设计软件allegro16.6版本约束管理界面讲解

录入:edatop.com 点击:

cadence约束管理器在PCB设计规则设置中是必不可少的,它也称为DRC检查规则,用来确定电路板的走线规则是否符合PCB设计要求。本节主要是给大家介绍约束管理器的6个界面。

首先,可以通过菜单Setup/constraints/Constraint Manager…或者点击图标 2016_12_20_1482200678_930859.jpg进入约束管理器。

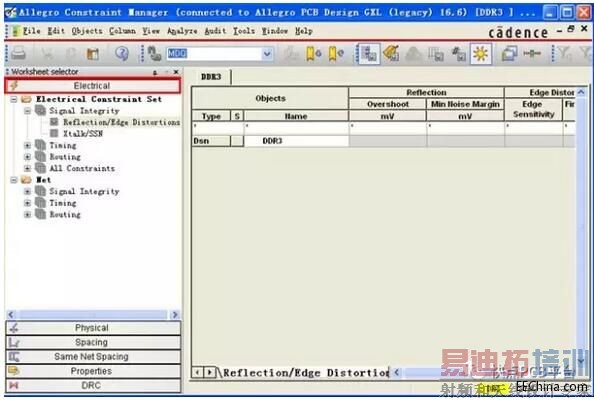

电气规则设置界面

1

Electrical:电气规则设置选项,在Electrical Constraint Set中设置不同的电气规则,在Net下将前面的规则赋予需要的网络

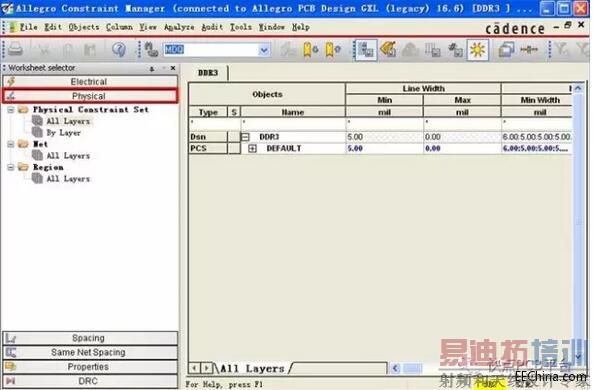

物理规则设置界面

2

Physical:物理规则设置选项,在Physical Constraint Set中设置不同的物理规则,在net下将前面的规则赋予需要的网络;其中Region 是区域规则,主要针对BGA、引脚间距小、出线密度高的器件,需绘制一个区域框并赋予区域规则,区域内线宽和间距都可能小于区域外,物理规则下能够赋予物理规则。

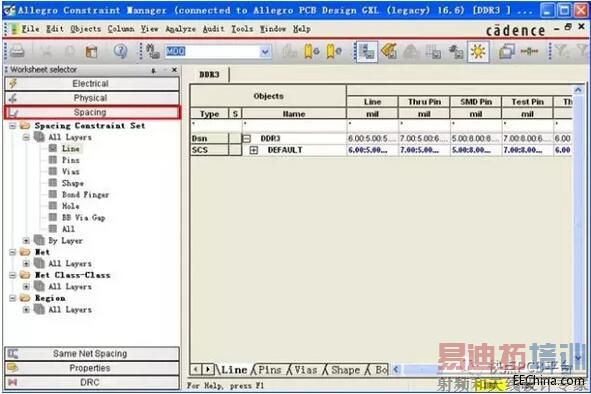

间距规则设置界面

3

Spacing:间距规则设置选项,在Spacing Constraint Set中设置不同的物理规则,在net下将前面的规则赋予需要的网络,Net Class-Class是设置网络类之间的间距,补充网络间距之间的不足。Region中可以赋予区域间距规则。

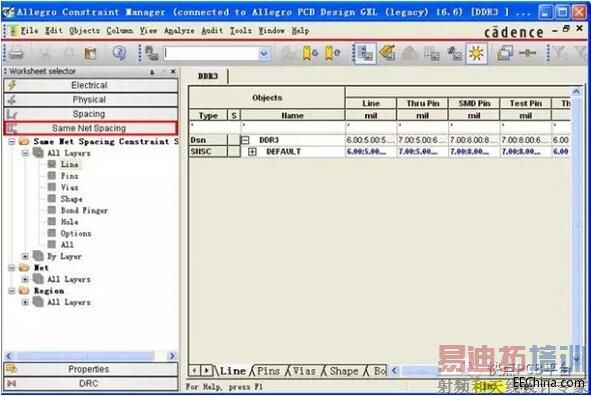

同名网络间距规则设置界面

4

Same Net Spacing:同名网络间距设置选项,即一个网络本身之间的间距,主要是在需要绕线时运用。

属性设置界面

5

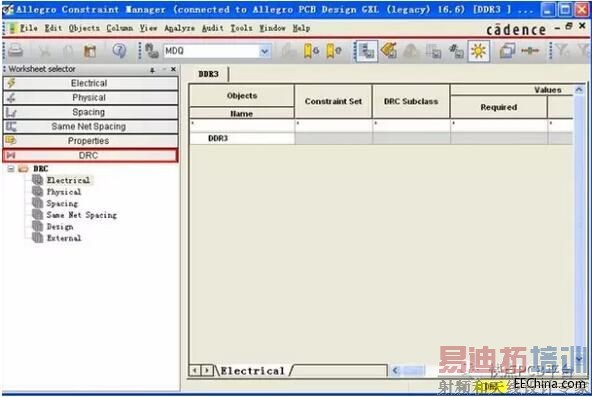

DRC界面

6

DRC:DRC错位查看选项,能够查看不同规则下错误的数量和位置,以及和错误相关的规则约束条件。

对高速PCB设计软件 cadence16.6版本约束管理器界面进行介绍完毕后,下期继续为大家介绍与网络有关的约束与规则的讲解。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:原创|高速PCB设计软件allegro中与网络有关的约束规则设置

下一篇:高速PCB设计软件allegro16.6演示差分规则的设置

射频和天线工程师培训课程详情>>