- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

[原创]申请加精 电容的分类及用法

录入:edatop.com 点击:

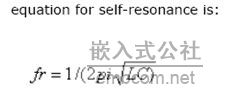

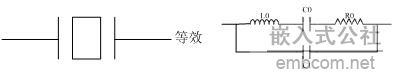

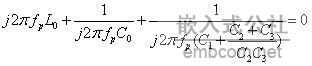

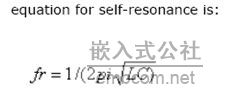

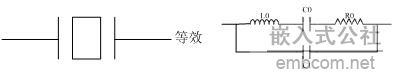

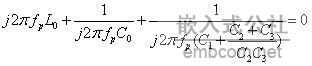

电容的用处其实就是“让交流通过,不让直流通过。”所以电容可以分离交流信号和直流信号。所以当高频信号是干扰时可以用电容将干扰滤掉。要知道电容的选材原则,首先要知道电容的滤波原理:在高频场合或对于高频信号电容等效于一个LCR电路(并联等效可以忽略),当频率达到LCR谐振频率时电容的阻抗最小,该频率的信号最容易通过电容。但是当电路频率高于电容的自谐振频率后,频率越高电容显感性阻抗越来越高,使旁路作用大大下降。自谐振频率受电容值的大小和等效电感的大小决定。电容越大自谐振频率越,等效电感越大自谐振频率越低。自谐振公式如下:

一般0.1uF的表面贴电容的等效电感有3nH。那么,它的自谐振频率为:

也就是说9.2MHz的干扰将很容易通过这个0.1uF的电容被滤掉。

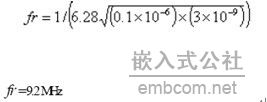

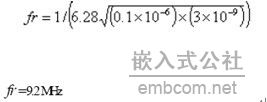

一般可以认为ESL为15nH/in。例如0603封装的就是长0.6in、宽0.3in、ESL=9 nH。下表为通常情况下容值对应的滤波频率(自谐振频率)。

一、滤波电容作用(旁路或去耦,至少在摆放位置上这两者是一样的):

网上参考:通常采用旁路电容来解决稳压器无法适应系统中高速器件引起的负载变化,以确保电源输出的稳定性及良好的瞬态响应。旁路电容是为本地器件提供能量的储能器件,它能使稳压器的输出均匀化,降低负载需求。就像小型可充电电池一样,旁路电容能够被充电,并向器件进行放电。为尽量减少阻抗,旁路电容要尽量靠近负载器件的供电电源管脚和地管脚。这能够很好地防止输入值过大而导致的地电位抬高和噪声。地弹是地连接处在通过大电流毛刺时的电压降。应该明白,大容量和小容量的旁路电容都可能是必需的,有的甚至是多个陶瓷电容和钽电容。这样的组合能够解决上述负载电流或许为阶梯变化所带来的问题,而且还能提供足够的去耦以抑制电压和电流毛刺。在负载变化非常剧烈的情况下,则需要三个或更多不同容量的电容,以保证在稳压器稳压前提供足够的电流。快速的瞬态过程由高频小容量电容来抑制,中速的瞬态过程由低频大容量来抑制,剩下则交给稳压器完成了。其次,旁路电容并联可以减少整体的ESR,这样不仅能让干扰接地的阻抗更小,还能分散每个电容的功耗,延长电容的使用寿命。

个人认为:滤波电容就是要在任何情况下,保证供给给器件的电源或信号质量可以被接受。具体有一下几点。1、负载突然增大电流的需求时,短时间内供给负载电流,保证输入端电压没有大的下降(相当于滤除低频信号)。2、在干扰(高频)进入负载前将其滤除。

电容重要参数作用。

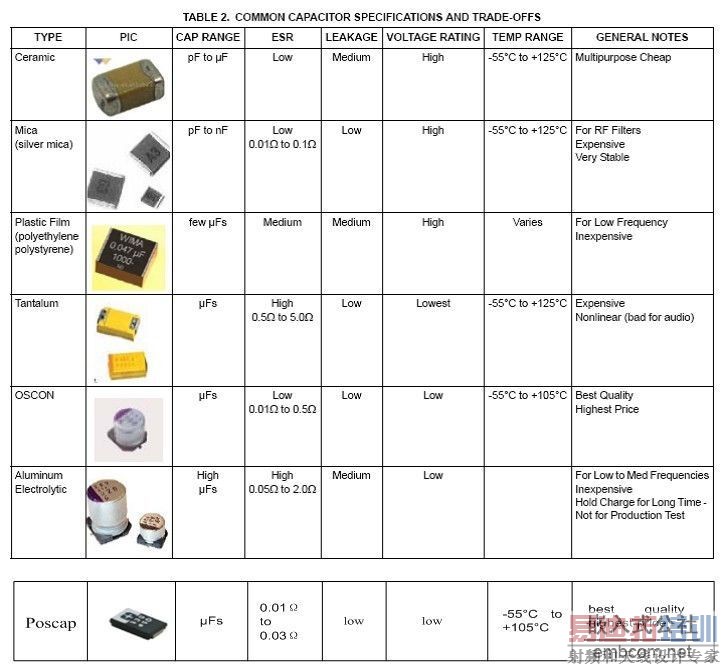

1、ESR:通常越小越好(除非为了减小并联谐振的影响)。干扰电流经过ESR,ESR越小在ESR两端产生的纹波电压越小,即抑制纹波的能力越强。ESR收电容类型影响较大具体见下面选材原则。

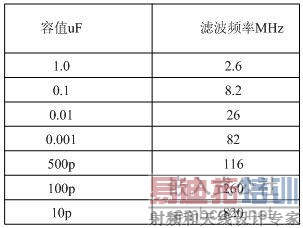

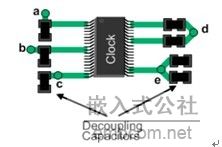

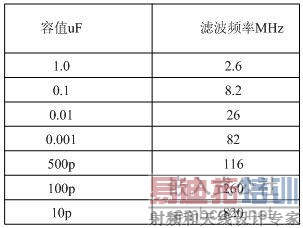

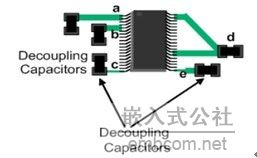

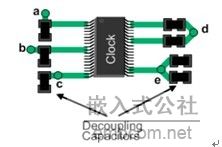

2、ESL:永远越小越好。越小自谐振频率越高,滤高频能力越强。实际设计时,选取的电容如果ESL较大会影响设计效果,使原设计中电容滤除的频率变低。ESL有三方面决定:1、封装。表面贴比插针式的小,封装越小ESL越小。2、引线长度。旁路时要与IC放得尽可能近,越近ESL越小,引线越粗越短ESL越小。如图。

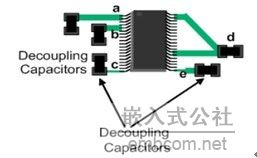

旁路电容的放置要尽量靠近IC,而且要用粗点的走线。例如:

(a)

图中b的放置和走线是最好的。

过孔与旁路电容的放置要点。如下:

(b)

a和b是可以接受的。过孔不能放在旁路电容前面,两个旁路电容不能连到一个孔上。3、电容内的等效电感,实际中不能控制,只有选材时看datasheet。

3、容值C:越大则滤波频率越低,但存储的能量越多,越高则滤波的频率越高,虽然能更快速提供存储的能量,但是所存的能量更小。

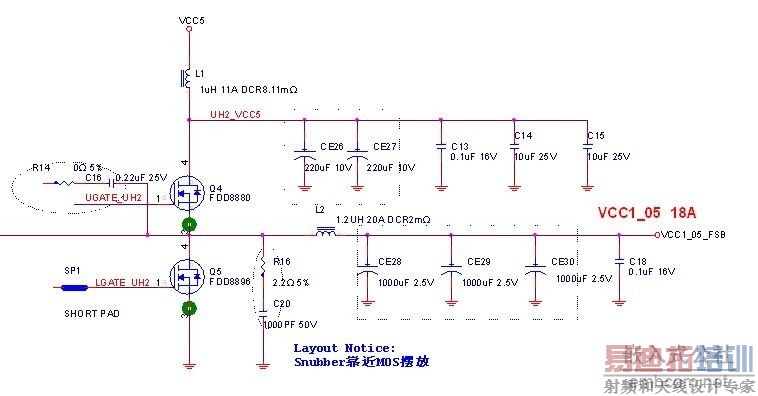

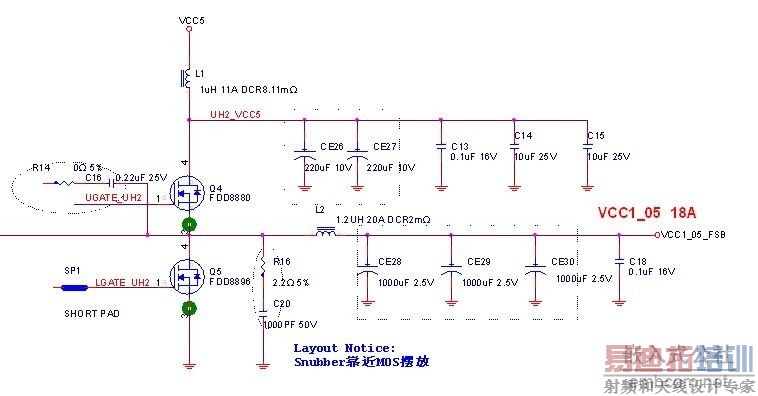

例一、例如下图:

VCC5给BUCK电路供电,MOS管在开启关闭时会有过冲现象。

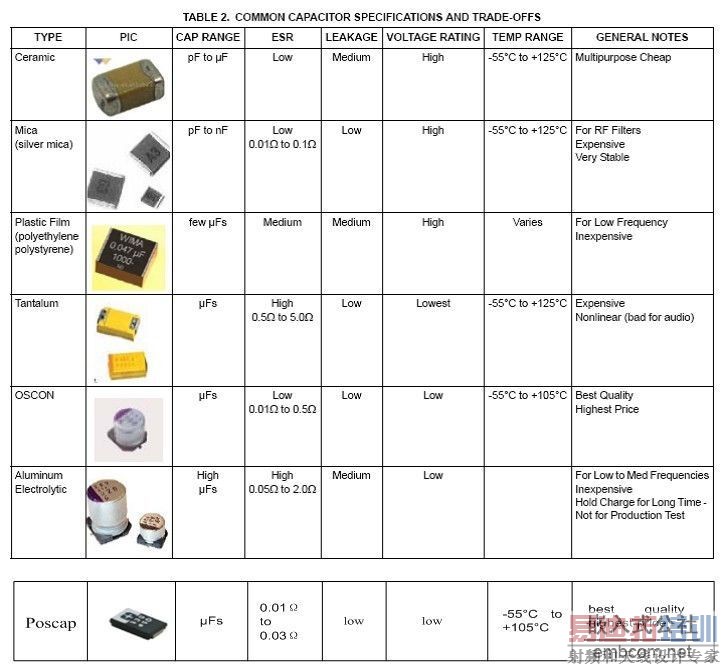

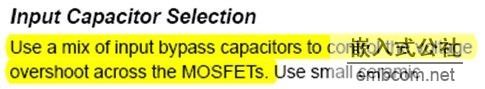

因而需要在VCC5输入端有并联旁路电容。其中,小容值(small ceramic capacitor:C13、C14、C15)电容起到去除高频分量的作用(相当于滤除高频小幅值的纹波),大电容(input bulk capacitor:CE26、CE27)用于Q4导通时瞬间的电流需求,保证5V没有过大的衰减(相当于滤除低频大幅值的纹波)。此处,取材原则如下:

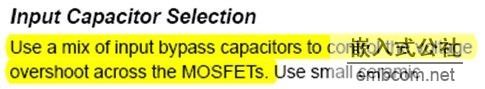

1、选取大电容(input bulk capacitor:CE26、CE27)时参考如下

封装类型:

对于大电容(input bulk capacitor:CE26、CE27)上句说明最好不要用插针式的电容,应该使用表面贴式的电容,表面贴的ESL较插针式的要小,自谐振频率更高,对交流干扰滤波能力就更强(尽管所率频率较低,ESL永远是小越好。

电容类型:

通过比较,选取表面贴式poscap电容,主要考虑EC4板子的大小限制了器件的大小,要在小区域完成高性能旁路作用,所以选poscap电容。其他参数的原因见下。

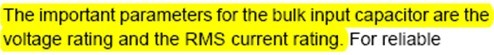

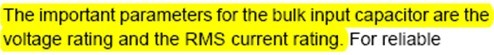

额定电压:

此处要求的是可靠性,所以主要选取条件是额定电压和能承受的最大纹波电流。一般选取电容的额定电压是实际应用的1.5倍以上,此处选取的10TPB220M额定电压是10V为5V的两倍满足要求。

最大承受纹波电流:最大承受纹波电流一般为电容滤波线上直流电流的1/2。此处,1.05V的电流是18A,功率约为18.9W。以BUCK的转化效率推断5V大概需要5A以内的电流。所以此处的10TPB220M电容的最大承受纹波电流是3000mA,满足要求。

等效串联电阻ESR:

ESR小可以带来两点好处:1、提高电容对瞬态事件的反应能力,使电容能及时提供电流给系统。此处,对这点要求较高,所以选取的电容ESR只有40毫欧姆。2、增强减小纹波电压的能力。ESR越小纹波电流经过电容产生的纹波电压就越小。

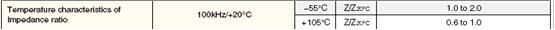

高频特性Poscap电容的高频特性很好,容值随频率升高减少缓慢,特别是在100~5000kHz范围内,其ESR及阻抗都相当低(小于0.1Ω),可减小损耗,并且能很好地减小纹波电压。

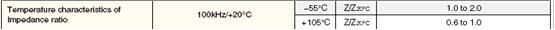

温度特性:

其次,poscap电容的温度特性很好是X6R,10TPB220M在温度从-55℃到105℃变化范围内,其ESR值及阻抗值基本不变。

体积小适合回流焊:10TPB220M 大小为7.3mm*4.3mm,如果用铝电解电容则体积太大,且数量要求更多。适合回流焊。

电容的容值:参考公式:

。其中:

为导通电流强度,

为5V允许的衰减范围, 为5V开关电源能响应电流需求的时间。所以

。再考虑其作为储能电容的作用,所以选取两个220uF,如果实际中发现Q1导通瞬间电压不足可以再并一个220uF电容进行调试。

摆放位置:从公司实际的板子上看,只要是起滤波作用的(旁路、去耦)都一定放在电源入IC的端口附近。即使是图中CE28、CE29这样的大整流电容(相当于滤低频)也不是放在开关电源的输出端,而是放在IC的电源输入端。

2、小容值电容(small ceramic capacitor:C13、C14、C15)选取参考如下:

小容值电容主要是高频小幅值滤波,因此主要考虑它们的滤波频带宽度和滤波能力。

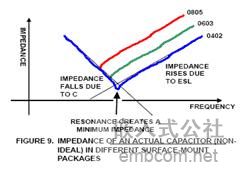

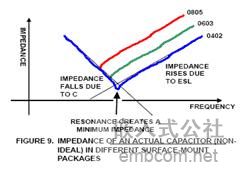

上图是同一容值的不同封装的阻抗曲线,封装越大ESL越大,自谐振频率越小。

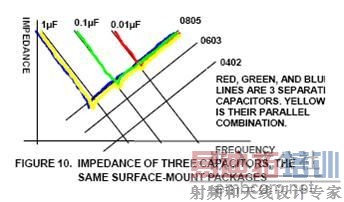

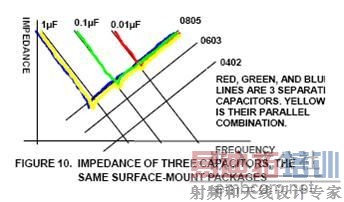

上图是不同容值相同封装的阻抗曲线,当ESL一定(概率上)时,电容值越小自谐振频率越高,滤高频效果越好。

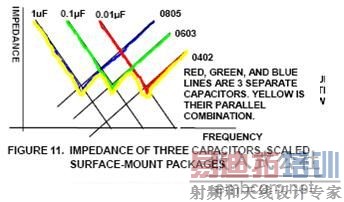

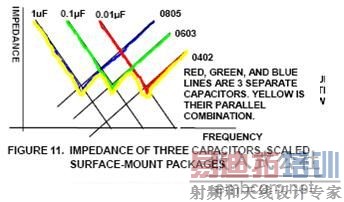

上图是较理想的阻抗曲线,每一个容值的电容封装都做到最小,这样每个电容都能发挥全部的滤波能力。所以滤波可以选取不同的容值,尽量小的封装的电容。

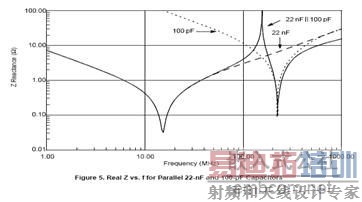

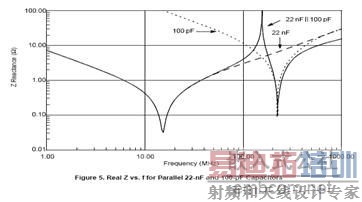

其次,很重要的一点是,不同容值的电容并联可能会引起并联谐振。例如。

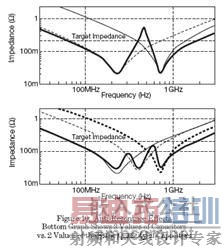

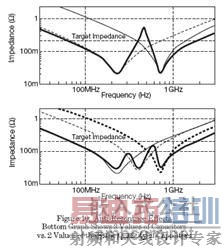

对在两个电容自谐振频率之间的信号来说,一个电容显感性,一个电容显容性,则会在某个频率上发生并联谐振,使阻抗变得很大。但是当需要在一个较宽的范围频带上滤波的话则必须要不同容值的电容,避免或减小并联谐振的方法是:

增大ESR、减小ESL和使用多量不同容值的电容。实际中,由于板子的大小限制不可能放很多数量的电容,因此可以尽量选取不同容值的电容。其次,实际中,不能增加ESR那样会增大纹波,所以只能选择小ESL的电容。

上图是相同数量,两种容值和三种容值的阻抗曲线。

电容类型:现在小封装的MLCC是高频滤波的首选,表贴陶瓷电容或者表面贴多层陶瓷电容(MLCC)具有更小的 ESR和更小的ESL。所以此处选择表面贴的片状陶瓷电容可以获得最好的高频滤波效果。

电容数量:此处是DC/DC,属于低频大电流场合。高频或中高频干扰幅值应该不是很强,所以用了一个0.1uF和两个10uF的电容就可以了。如果实际调试中,发现高频滤波效果不理想可以在加几个0.01uF电容。

封装类型:滤波电容的引脚会产生等效电感,降低自谐振频率,影响高频滤波效果,所以应该使用表面贴式的电容。

额定电压:一般选取电容的额定电压是实际应用的1.5倍以上,此处选取的CRM31C有25V的额定电压,CRM155有16V的额定电压,均满足要求。

体积小适合回流焊:CRM155大小为1mm*0.5mm;CRM31C大小为3.2mm*1.6mm。

适合回流焊。

高频等效阻抗特性:优良的高频特性。

CRM31C、CRM15的高频等效阻抗很小,很适合滤除高频干扰。

电容的容值:由于5V的之前有大量去耦电容的滤波,此处的高频干扰幅值不会很大所以用一个0.1uF、两个10uF的电容可以在较宽的频带上滤除幅值较低的干扰。

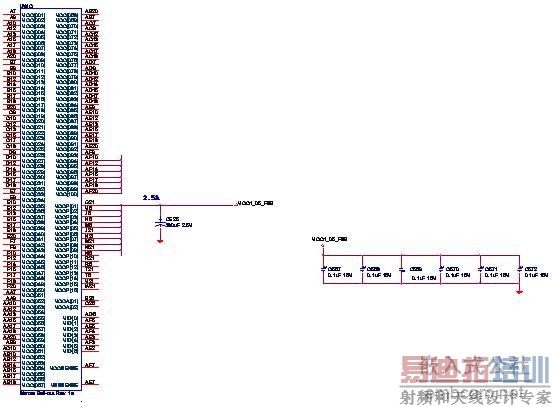

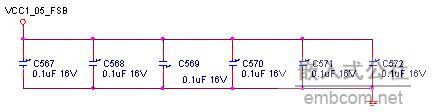

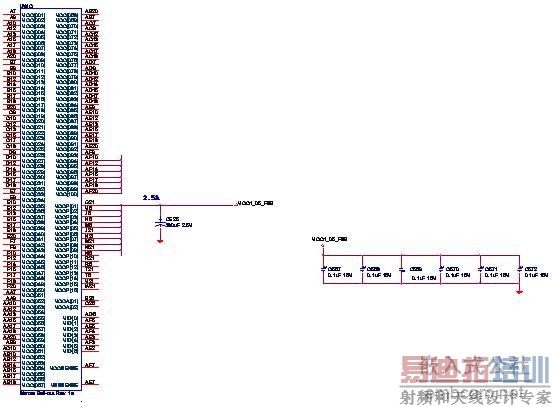

例二、

放大:

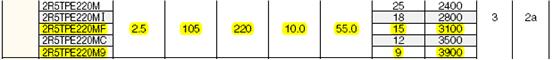

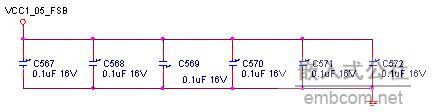

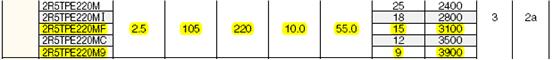

VCC1_05_FSB进入CPU前先进行一个220uF和6个0.1uF的旁路滤波。

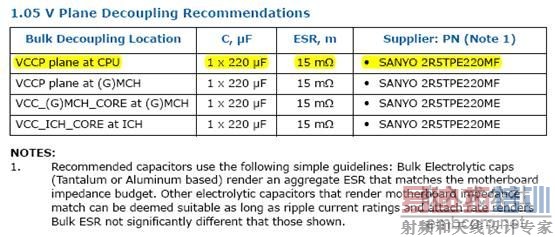

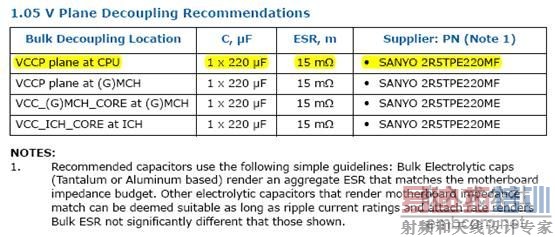

1、选取大电容(input bulk capacitor:CE25)时参考如下

在designguide上说此处的bulk电容可以选用sanyo的2R5TPE220MF或者ESR和最大纹波等效电流这两个指标符合要求的电容也可以。

实际中,选用了性能更好的2R5TPE220M9。

它的ESR更小和最大承受纹波电流更高。这样系统的性能将更稳定。

其他参数见上一例。

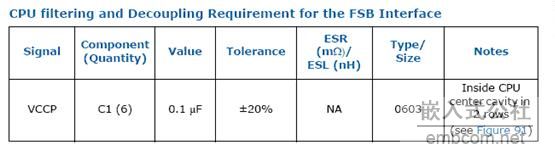

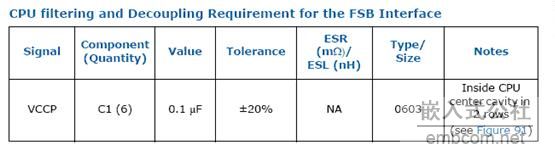

二、小容值电容(small ceramic capacitor:C567~C572)选取原则如下:

根据designguide如下

电容类型:高频滤波时,小容量电容0.1μF 量级就能很好满足要求。表贴陶瓷电容或者多层陶瓷电容(MLCC)具有更小的 ESR。所以此处选择表面贴的片状陶瓷电容。

电容数量:此处,高频干扰幅值较大,所以用了六个0.1uF电容。多个电容并联可以减少整体的ESR,这样不仅能让干扰接地的阻抗更小,还能分散每个电容的功耗,延长电容的使用寿命。

其他参数见上一例。

滤波电容选取的总结:1、先看IC的datasheet和designguide里面会告诉我们该IC允许的纹波参数(尽管我们可以选取高价电容或大量电容把纹波抑制到远远优于datasheet和designguide的指标,但那样不见得在投入产出上达到平衡)

以及参考电路或推荐电容。2、如果datasheet和designguide中没有明确指定电容的用法,可以分别根据滤高频和低频两个方面去注意电容选取使用的原则,实际中可以用示波器查看纹波是否满足要求。3、如果实际中发现纹波波动太大,可以根据噪声的频率等参数和本文的介绍对电容进行优化使用。4、本人认为储能电容就是滤低频的电容,因为储能电容的作用为芯片提供所需的电流,将电流的变换局限在小范围内,如果把这种电流的需求看成是一种噪声的话,那么储能电容就是在起到一个滤低频的作用,无非低频的分量有时很大,需要电容有较大的容值可以储存或释放较大的电流。

二、耦合电容的作用:让高频数据(有价值的信号)通过电容,把直流信号(无价值的信号)隔离,这样可以减小直流信号的干扰。保证高频信号的质量。

例如:

上图是RTL8111C和南桥的PCI-E上的耦合电容差分信号。差分信号除了要等长等间距的原则外,如果是高速信号一般还要加上耦合电容,经过实验发现不加耦合电容,会发生IP获取时间延长或找不到IP的情况。

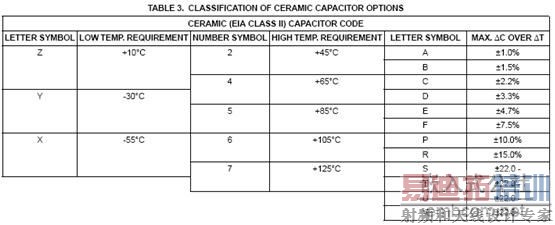

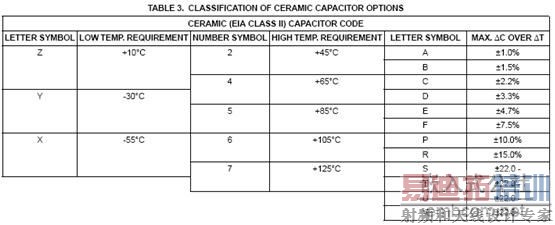

耦合电容的选取原则:1、电容的精度要高,一般要选10%的,在RTL8111C和南桥的PCI-E上的耦合电容,选取80%~-20%的电容时就会出现传输错误,找不到IP。2、温度稳定性要高至少要选取X7R的。3、容值一般选取0.1uF的,在RTL8111C和南桥的PCI-E上的耦合电容,选取0.01uF电容时就会出现找不到RTL8111C的问题。耦合电容只要有滤除直流的功能就行了,所以不宜选的太小,除非考虑传输时有连续“0”或“1”的情况,但这在工控机上很少见,可以忽略。

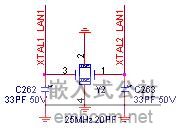

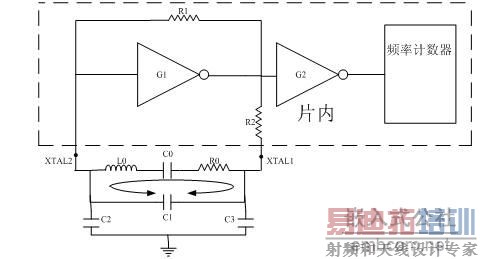

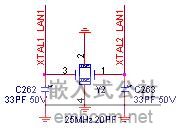

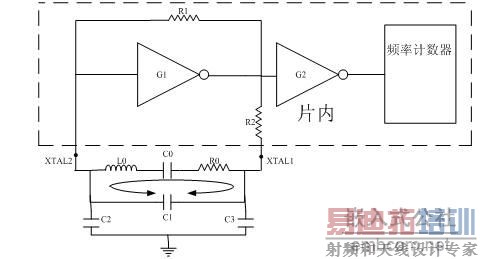

三、晶振调谐电容(load capacitor)的作用:仅调节晶振的频率。

晶振的等效图如下。

实际应用中,如图所示。

等效图。

其中,R1是给G1提供反馈,帮助晶振起振的,一般做在IC内,如果没有也可以与晶振并联在片外,一般选个大电阻例如10M欧姆。图中,晶振和谐振电容组成的电路发生并联谐振。所以可以得到如下公式。

设

。解上述方程得

式中我们可以控制的只有

此处的调谐电容选取原则是:1、绝对参数要满足要求。2、容值的精度要尽可能高,因为CL的变化可以决定实际晶振的频率,一般选取精度是最高的5%。3、温度稳定性要最好的电容,一般选取NP0的,即不管什么温度下CL的变化都不大,保证晶振的频率。4、ESL、ESR越小越好,这样能使并联回路的阻抗更加接近理论值使晶振频率更加准确。5、容值参考晶振datasheet。6、容值越大晶振频率越低,容值越小晶振频率越高,可以根据这个规则去调节晶振频率。

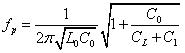

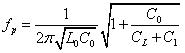

四、RC电容的作用:1、以延长电平上升或下降的时间为代价,消除噪声对系统稳定性的影响。2、或者起到延迟信号相位的作用。

其中R的作用是限制C充电或放电的电流,相当于调节C两端电压变化快慢的阀门。

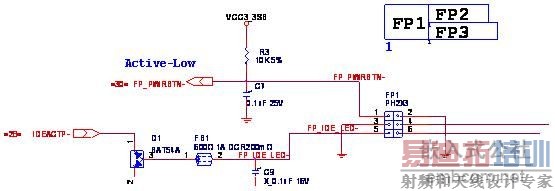

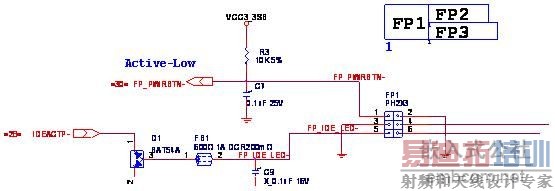

例如1:

图中R128、C108就是一个RC电路。C108两端的电压不能瞬间变换,除非有大的电流,通过R128来限制C108充放的电流强度。从而使Q26基极电压在上升或下降时,显单调变化使得RI-这个重要的唤醒信号质量得到保证。

此处电容的选取原则是:1、绝对参数要满足要求。2、当系统处于S5状态时,COM1_RI_CN-由COM口拉高,使PM_RI-变有效。不知道COM1_RI_CN-拉高的时间,这里时间常数为0.2ms。以5倍时间常数的习惯,看COM1_RI_CN-拉高的时间可能大于1s。个人认为时间常数不要去太大。3、容值精度对消除噪声的影响不大,但有关于唤醒、复位等关键信号必须小心处理,所以选材质量要有保证,此处选择10%的电容。4、同样温度稳定性选取X7R,才能保证关键部位的正常。

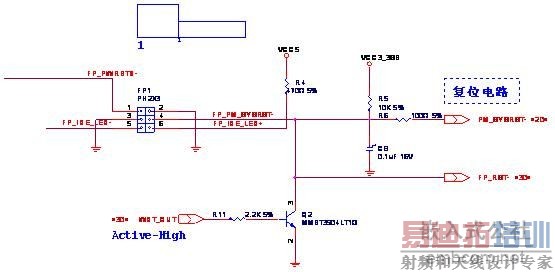

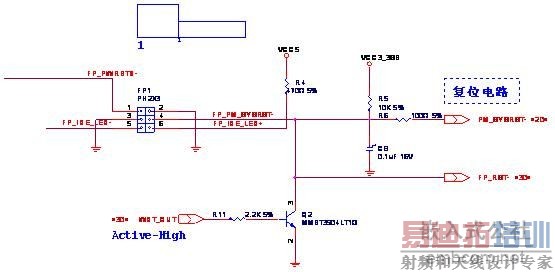

例如2:

C7、R3就是一个RC去噪电路。时间常数是1ms,一般手按键的时间最快也要20ms。时间常数的5倍安全时间远小于20ms,所以这个RC既能去噪又能不影响按键开机的成功率。选取原则同上。

例如3:

图中C8、R5组成一个RC滤波电路,原理同上。图中看门狗的复位信号其实也是通过Q2做了一个隔离。但是三级管的隔离效果要远小于RC,三极管的隔离原理是把开关信号由低变高时,在开启电压以下的波动滤除。或这把开关信号由高变低时,在开启电压以上的波动滤除。而像按键时产生的抖动是“0”、“1”间的波动,对此三极管隔离就不够了。

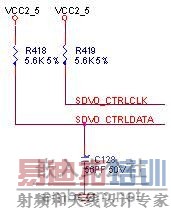

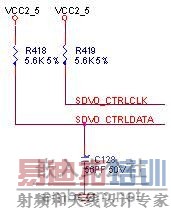

例如4:

在北桥和DVI传输芯片的控制信号通过SMBUS完成。但可能965的芯片控制DATA线的速度太快,导致了DVI传输芯片无法识别总线的数据。于是在DATA线上加一个56pf电容,这个问题就解决了。原理是电容延缓了DATA线上数据的改变,延长了数据的hold时间。此处电容选择的原则:1、满足极限条件。2、容值一定要高精度,因为容值决定延迟时间,而延迟时间是解决问题的关键。3、温度稳定性一定要好,一般选NPO的。4容值的选择可以做实验或参考AN。

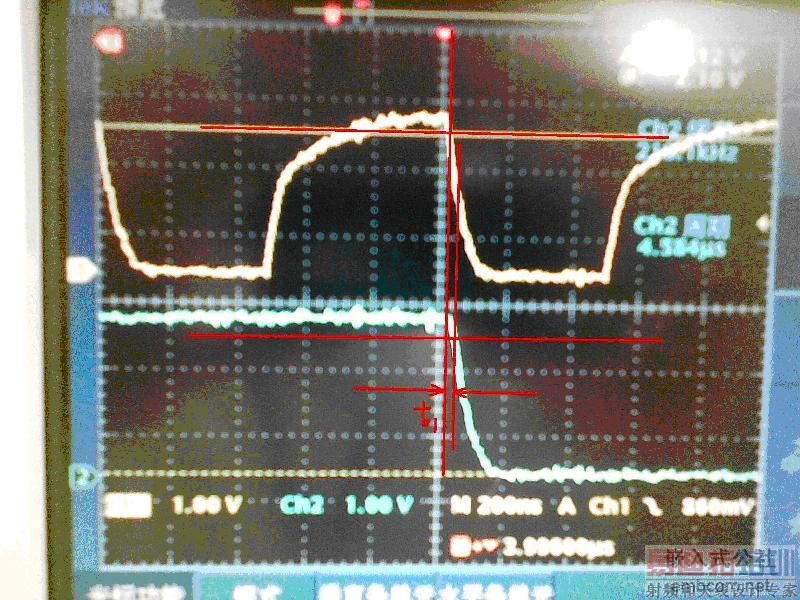

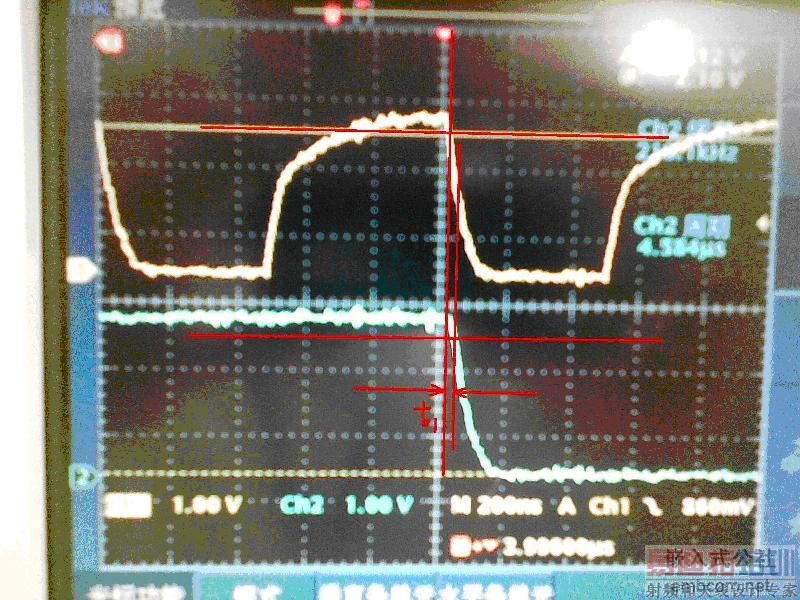

以下是不加电容和加电容波形图的比对。

编辑完毕,请楼主审查!

一般0.1uF的表面贴电容的等效电感有3nH。那么,它的自谐振频率为:

也就是说9.2MHz的干扰将很容易通过这个0.1uF的电容被滤掉。

一般可以认为ESL为15nH/in。例如0603封装的就是长0.6in、宽0.3in、ESL=9 nH。下表为通常情况下容值对应的滤波频率(自谐振频率)。

一、滤波电容作用(旁路或去耦,至少在摆放位置上这两者是一样的):

网上参考:通常采用旁路电容来解决稳压器无法适应系统中高速器件引起的负载变化,以确保电源输出的稳定性及良好的瞬态响应。旁路电容是为本地器件提供能量的储能器件,它能使稳压器的输出均匀化,降低负载需求。就像小型可充电电池一样,旁路电容能够被充电,并向器件进行放电。为尽量减少阻抗,旁路电容要尽量靠近负载器件的供电电源管脚和地管脚。这能够很好地防止输入值过大而导致的地电位抬高和噪声。地弹是地连接处在通过大电流毛刺时的电压降。应该明白,大容量和小容量的旁路电容都可能是必需的,有的甚至是多个陶瓷电容和钽电容。这样的组合能够解决上述负载电流或许为阶梯变化所带来的问题,而且还能提供足够的去耦以抑制电压和电流毛刺。在负载变化非常剧烈的情况下,则需要三个或更多不同容量的电容,以保证在稳压器稳压前提供足够的电流。快速的瞬态过程由高频小容量电容来抑制,中速的瞬态过程由低频大容量来抑制,剩下则交给稳压器完成了。其次,旁路电容并联可以减少整体的ESR,这样不仅能让干扰接地的阻抗更小,还能分散每个电容的功耗,延长电容的使用寿命。

个人认为:滤波电容就是要在任何情况下,保证供给给器件的电源或信号质量可以被接受。具体有一下几点。1、负载突然增大电流的需求时,短时间内供给负载电流,保证输入端电压没有大的下降(相当于滤除低频信号)。2、在干扰(高频)进入负载前将其滤除。

电容重要参数作用。

1、ESR:通常越小越好(除非为了减小并联谐振的影响)。干扰电流经过ESR,ESR越小在ESR两端产生的纹波电压越小,即抑制纹波的能力越强。ESR收电容类型影响较大具体见下面选材原则。

2、ESL:永远越小越好。越小自谐振频率越高,滤高频能力越强。实际设计时,选取的电容如果ESL较大会影响设计效果,使原设计中电容滤除的频率变低。ESL有三方面决定:1、封装。表面贴比插针式的小,封装越小ESL越小。2、引线长度。旁路时要与IC放得尽可能近,越近ESL越小,引线越粗越短ESL越小。如图。

旁路电容的放置要尽量靠近IC,而且要用粗点的走线。例如:

(a)

图中b的放置和走线是最好的。

过孔与旁路电容的放置要点。如下:

(b)

a和b是可以接受的。过孔不能放在旁路电容前面,两个旁路电容不能连到一个孔上。3、电容内的等效电感,实际中不能控制,只有选材时看datasheet。

3、容值C:越大则滤波频率越低,但存储的能量越多,越高则滤波的频率越高,虽然能更快速提供存储的能量,但是所存的能量更小。

例一、例如下图:

VCC5给BUCK电路供电,MOS管在开启关闭时会有过冲现象。

因而需要在VCC5输入端有并联旁路电容。其中,小容值(small ceramic capacitor:C13、C14、C15)电容起到去除高频分量的作用(相当于滤除高频小幅值的纹波),大电容(input bulk capacitor:CE26、CE27)用于Q4导通时瞬间的电流需求,保证5V没有过大的衰减(相当于滤除低频大幅值的纹波)。此处,取材原则如下:

1、选取大电容(input bulk capacitor:CE26、CE27)时参考如下

封装类型:

对于大电容(input bulk capacitor:CE26、CE27)上句说明最好不要用插针式的电容,应该使用表面贴式的电容,表面贴的ESL较插针式的要小,自谐振频率更高,对交流干扰滤波能力就更强(尽管所率频率较低,ESL永远是小越好。

电容类型:

通过比较,选取表面贴式poscap电容,主要考虑EC4板子的大小限制了器件的大小,要在小区域完成高性能旁路作用,所以选poscap电容。其他参数的原因见下。

额定电压:

此处要求的是可靠性,所以主要选取条件是额定电压和能承受的最大纹波电流。一般选取电容的额定电压是实际应用的1.5倍以上,此处选取的10TPB220M额定电压是10V为5V的两倍满足要求。

最大承受纹波电流:最大承受纹波电流一般为电容滤波线上直流电流的1/2。此处,1.05V的电流是18A,功率约为18.9W。以BUCK的转化效率推断5V大概需要5A以内的电流。所以此处的10TPB220M电容的最大承受纹波电流是3000mA,满足要求。

等效串联电阻ESR:

ESR小可以带来两点好处:1、提高电容对瞬态事件的反应能力,使电容能及时提供电流给系统。此处,对这点要求较高,所以选取的电容ESR只有40毫欧姆。2、增强减小纹波电压的能力。ESR越小纹波电流经过电容产生的纹波电压就越小。

高频特性Poscap电容的高频特性很好,容值随频率升高减少缓慢,特别是在100~5000kHz范围内,其ESR及阻抗都相当低(小于0.1Ω),可减小损耗,并且能很好地减小纹波电压。

温度特性:

其次,poscap电容的温度特性很好是X6R,10TPB220M在温度从-55℃到105℃变化范围内,其ESR值及阻抗值基本不变。

体积小适合回流焊:10TPB220M 大小为7.3mm*4.3mm,如果用铝电解电容则体积太大,且数量要求更多。适合回流焊。

电容的容值:参考公式:

。其中:

为导通电流强度,

为5V允许的衰减范围, 为5V开关电源能响应电流需求的时间。所以

。再考虑其作为储能电容的作用,所以选取两个220uF,如果实际中发现Q1导通瞬间电压不足可以再并一个220uF电容进行调试。

摆放位置:从公司实际的板子上看,只要是起滤波作用的(旁路、去耦)都一定放在电源入IC的端口附近。即使是图中CE28、CE29这样的大整流电容(相当于滤低频)也不是放在开关电源的输出端,而是放在IC的电源输入端。

2、小容值电容(small ceramic capacitor:C13、C14、C15)选取参考如下:

小容值电容主要是高频小幅值滤波,因此主要考虑它们的滤波频带宽度和滤波能力。

上图是同一容值的不同封装的阻抗曲线,封装越大ESL越大,自谐振频率越小。

上图是不同容值相同封装的阻抗曲线,当ESL一定(概率上)时,电容值越小自谐振频率越高,滤高频效果越好。

上图是较理想的阻抗曲线,每一个容值的电容封装都做到最小,这样每个电容都能发挥全部的滤波能力。所以滤波可以选取不同的容值,尽量小的封装的电容。

其次,很重要的一点是,不同容值的电容并联可能会引起并联谐振。例如。

对在两个电容自谐振频率之间的信号来说,一个电容显感性,一个电容显容性,则会在某个频率上发生并联谐振,使阻抗变得很大。但是当需要在一个较宽的范围频带上滤波的话则必须要不同容值的电容,避免或减小并联谐振的方法是:

增大ESR、减小ESL和使用多量不同容值的电容。实际中,由于板子的大小限制不可能放很多数量的电容,因此可以尽量选取不同容值的电容。其次,实际中,不能增加ESR那样会增大纹波,所以只能选择小ESL的电容。

上图是相同数量,两种容值和三种容值的阻抗曲线。

电容类型:现在小封装的MLCC是高频滤波的首选,表贴陶瓷电容或者表面贴多层陶瓷电容(MLCC)具有更小的 ESR和更小的ESL。所以此处选择表面贴的片状陶瓷电容可以获得最好的高频滤波效果。

电容数量:此处是DC/DC,属于低频大电流场合。高频或中高频干扰幅值应该不是很强,所以用了一个0.1uF和两个10uF的电容就可以了。如果实际调试中,发现高频滤波效果不理想可以在加几个0.01uF电容。

封装类型:滤波电容的引脚会产生等效电感,降低自谐振频率,影响高频滤波效果,所以应该使用表面贴式的电容。

额定电压:一般选取电容的额定电压是实际应用的1.5倍以上,此处选取的CRM31C有25V的额定电压,CRM155有16V的额定电压,均满足要求。

体积小适合回流焊:CRM155大小为1mm*0.5mm;CRM31C大小为3.2mm*1.6mm。

适合回流焊。

高频等效阻抗特性:优良的高频特性。

CRM31C、CRM15的高频等效阻抗很小,很适合滤除高频干扰。

电容的容值:由于5V的之前有大量去耦电容的滤波,此处的高频干扰幅值不会很大所以用一个0.1uF、两个10uF的电容可以在较宽的频带上滤除幅值较低的干扰。

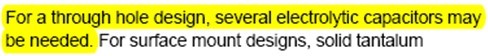

例二、

放大:

VCC1_05_FSB进入CPU前先进行一个220uF和6个0.1uF的旁路滤波。

1、选取大电容(input bulk capacitor:CE25)时参考如下

在designguide上说此处的bulk电容可以选用sanyo的2R5TPE220MF或者ESR和最大纹波等效电流这两个指标符合要求的电容也可以。

实际中,选用了性能更好的2R5TPE220M9。

它的ESR更小和最大承受纹波电流更高。这样系统的性能将更稳定。

其他参数见上一例。

二、小容值电容(small ceramic capacitor:C567~C572)选取原则如下:

根据designguide如下

电容类型:高频滤波时,小容量电容0.1μF 量级就能很好满足要求。表贴陶瓷电容或者多层陶瓷电容(MLCC)具有更小的 ESR。所以此处选择表面贴的片状陶瓷电容。

电容数量:此处,高频干扰幅值较大,所以用了六个0.1uF电容。多个电容并联可以减少整体的ESR,这样不仅能让干扰接地的阻抗更小,还能分散每个电容的功耗,延长电容的使用寿命。

其他参数见上一例。

滤波电容选取的总结:1、先看IC的datasheet和designguide里面会告诉我们该IC允许的纹波参数(尽管我们可以选取高价电容或大量电容把纹波抑制到远远优于datasheet和designguide的指标,但那样不见得在投入产出上达到平衡)

以及参考电路或推荐电容。2、如果datasheet和designguide中没有明确指定电容的用法,可以分别根据滤高频和低频两个方面去注意电容选取使用的原则,实际中可以用示波器查看纹波是否满足要求。3、如果实际中发现纹波波动太大,可以根据噪声的频率等参数和本文的介绍对电容进行优化使用。4、本人认为储能电容就是滤低频的电容,因为储能电容的作用为芯片提供所需的电流,将电流的变换局限在小范围内,如果把这种电流的需求看成是一种噪声的话,那么储能电容就是在起到一个滤低频的作用,无非低频的分量有时很大,需要电容有较大的容值可以储存或释放较大的电流。

二、耦合电容的作用:让高频数据(有价值的信号)通过电容,把直流信号(无价值的信号)隔离,这样可以减小直流信号的干扰。保证高频信号的质量。

例如:

上图是RTL8111C和南桥的PCI-E上的耦合电容差分信号。差分信号除了要等长等间距的原则外,如果是高速信号一般还要加上耦合电容,经过实验发现不加耦合电容,会发生IP获取时间延长或找不到IP的情况。

耦合电容的选取原则:1、电容的精度要高,一般要选10%的,在RTL8111C和南桥的PCI-E上的耦合电容,选取80%~-20%的电容时就会出现传输错误,找不到IP。2、温度稳定性要高至少要选取X7R的。3、容值一般选取0.1uF的,在RTL8111C和南桥的PCI-E上的耦合电容,选取0.01uF电容时就会出现找不到RTL8111C的问题。耦合电容只要有滤除直流的功能就行了,所以不宜选的太小,除非考虑传输时有连续“0”或“1”的情况,但这在工控机上很少见,可以忽略。

三、晶振调谐电容(load capacitor)的作用:仅调节晶振的频率。

晶振的等效图如下。

实际应用中,如图所示。

等效图。

其中,R1是给G1提供反馈,帮助晶振起振的,一般做在IC内,如果没有也可以与晶振并联在片外,一般选个大电阻例如10M欧姆。图中,晶振和谐振电容组成的电路发生并联谐振。所以可以得到如下公式。

设

。解上述方程得

式中我们可以控制的只有

此处的调谐电容选取原则是:1、绝对参数要满足要求。2、容值的精度要尽可能高,因为CL的变化可以决定实际晶振的频率,一般选取精度是最高的5%。3、温度稳定性要最好的电容,一般选取NP0的,即不管什么温度下CL的变化都不大,保证晶振的频率。4、ESL、ESR越小越好,这样能使并联回路的阻抗更加接近理论值使晶振频率更加准确。5、容值参考晶振datasheet。6、容值越大晶振频率越低,容值越小晶振频率越高,可以根据这个规则去调节晶振频率。

四、RC电容的作用:1、以延长电平上升或下降的时间为代价,消除噪声对系统稳定性的影响。2、或者起到延迟信号相位的作用。

其中R的作用是限制C充电或放电的电流,相当于调节C两端电压变化快慢的阀门。

例如1:

图中R128、C108就是一个RC电路。C108两端的电压不能瞬间变换,除非有大的电流,通过R128来限制C108充放的电流强度。从而使Q26基极电压在上升或下降时,显单调变化使得RI-这个重要的唤醒信号质量得到保证。

此处电容的选取原则是:1、绝对参数要满足要求。2、当系统处于S5状态时,COM1_RI_CN-由COM口拉高,使PM_RI-变有效。不知道COM1_RI_CN-拉高的时间,这里时间常数为0.2ms。以5倍时间常数的习惯,看COM1_RI_CN-拉高的时间可能大于1s。个人认为时间常数不要去太大。3、容值精度对消除噪声的影响不大,但有关于唤醒、复位等关键信号必须小心处理,所以选材质量要有保证,此处选择10%的电容。4、同样温度稳定性选取X7R,才能保证关键部位的正常。

例如2:

C7、R3就是一个RC去噪电路。时间常数是1ms,一般手按键的时间最快也要20ms。时间常数的5倍安全时间远小于20ms,所以这个RC既能去噪又能不影响按键开机的成功率。选取原则同上。

例如3:

图中C8、R5组成一个RC滤波电路,原理同上。图中看门狗的复位信号其实也是通过Q2做了一个隔离。但是三级管的隔离效果要远小于RC,三极管的隔离原理是把开关信号由低变高时,在开启电压以下的波动滤除。或这把开关信号由高变低时,在开启电压以上的波动滤除。而像按键时产生的抖动是“0”、“1”间的波动,对此三极管隔离就不够了。

例如4:

在北桥和DVI传输芯片的控制信号通过SMBUS完成。但可能965的芯片控制DATA线的速度太快,导致了DVI传输芯片无法识别总线的数据。于是在DATA线上加一个56pf电容,这个问题就解决了。原理是电容延缓了DATA线上数据的改变,延长了数据的hold时间。此处电容选择的原则:1、满足极限条件。2、容值一定要高精度,因为容值决定延迟时间,而延迟时间是解决问题的关键。3、温度稳定性一定要好,一般选NPO的。4容值的选择可以做实验或参考AN。

以下是不加电容和加电容波形图的比对。

没加电容DATA和CLK几乎同时变化。

编辑完毕,请楼主审查!

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:EMI/EMC设计讲座(五)映像平面的分割与隔离

下一篇:毕业5年决定你的命运

射频和天线工程师培训课程详情>>