- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的双备份多路数据采集存储系统的设计与实现

随着信息技术的发展以及数字集成电路速度的提高,实时处理大量数据已经成为现实,但在一些特殊条件下,无法实时传输数据,必须使用存储测试方法。该方法是在不影响被测对象或在允许的范围下,将微型存储测试系统置入被测体内,现场实时完成信息的快速采集与存储,并回收存储器,由计算机处理,再现被测信息的一种动态测试技术[1]。实际应用中,由于在不同的条件下对采样速率和采样精度的要求有所不同,系统的实现方法也各有特点。为了增加系统数据回收的可靠性,本文介绍了基于双备份存储的数据采集存储系统的设计与实现方法。

1 技术要求

在某飞行体遥测系统中,为了获取飞行体的参数,需要设计一种数据采集存储系统,要求实现对23路模拟信号的采集、编帧存储。要求输入信号电平为0~5 V,系统总采样率为245.76 kHz, 记录时间不小于500 s,对速变信号的采样率为5.12 kHz,缓变信号的采样率为160 Hz, 23路模拟量信号输入中包括9路速变信号和14路缓变信号。

2 整体方案的设计

信号采集存储系统是基于双备份的数据存储器设计而成,整个系统以FPGA为核心控制器,控制数据的采集、编帧存储。系统结构如图1所示。

2.1采编器电路的设计

采编器[2]主要完成对各种被测信号的采集,并对数据进行实时编码、逻辑控制和实时存储控制,分为速变、缓变信号采集模块和采集控制模块,两者通过内部总线相连。

速变、缓变信号采集模块主要完成23路输入模拟信号的调理、选择、A/D采集等功能,包括输入接口电路、滤波跟随电路、模拟通道切换电路、信号调理电路等。

采集控制模块完成模拟信号的A/D采集控制、编帧、内部时序控制等功能,包括长线接口电路、控制电路、存储器接口电路、帧结构下载电路等。

采编器的主控器件采用XC2S100E型现场可编程门阵列(FPGA),该器件体积小、功耗低、内部延时小,全部控制逻辑由硬件自动完成,编程配置灵活,可实现程序的并行执行,因而可大大提高系统的工作性能。该采编器的电压采集范围为0~+5 V,采集精度不低于0.1%。由于FPGA本身不具备A/D转换模块,因此各通道的模拟信号分别经信号调理电路后,由模拟多路开关ADG506选择模拟通道,再经外部高速AD7667实现A/D转换,转换的数据在FPGA内编帧后输出到存储器中。具体的每帧数据由各路模拟信号和帧标记FDB1 8540组成。采编器的电源由电源模块提供的5 V电压经TPS70351调理后产生。

采编器电路框图如图2所示。

2.2存储器电路的设计

存储器主要完成数据的存储功能,存储器包括两套独立的存储电路A、B片,两者互为备份。每套存储器内包括与采编器相连的长线接口、FPGA和Flash存储芯片。该双备份设计能进一步提高数据回收的可靠性。

存储器电路框图如图3所示。

技术要求总采样率约250 kHz,记录时间不小于500 s, A/D采集的有效位数为16 bit,则一个采样周期(即4 μs)产生的数据量为2 B, 则1 s的数据量为1×106×2/4=500 000 B,则500 s内的记录数据量为2.5×108 B=238.5 MB, 可见容量为256 MB的闪存芯片便可满足记录要求,本设计采用SAMSANG公司的Flash存储芯片K9K8G08U0M,存储容量达1 GB,是为了留出存储余量,这样就为以后系统的升级和扩展提供可行性解决方案。

3系统软件设计

3.1采集控制逻辑的设计

对于多通道异步时分采集这种形式的电路,由于在电子开关切换的过程中存在着串扰,信号受到该串扰后,滤波放大器的输出在ADC采样前未稳定至其应有的精度,就会对ADC的采样有影响,从而影响采集精度。所以,为了解决串扰问题,只有在实践的基础上,靠经验去选择合适的运放,或者是通过硬件与系统软件优化相结合的方法寻找解决途径。

在确保系统采样率的前提下,本设计通过硬件与软件相结合的方法来解决串扰问题。硬件上采集模块选择SR(压摆率)较高的运放LF247作为滤波跟随器,软件上则以并行的工作方式确保采样前采样通道信号的稳定,即在时序设计上,主程序中采用了两个进程:(1)完成数据的转换、帧计数和数据的传输; (2)根据帧计数frame_cnt控制通道地址信号a和p进行通道切换。这两个进程并行执行。

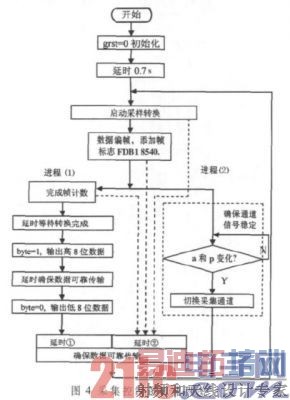

FPGA采集控制逻辑流程图如图4所示。其中,a为通道选择输出,接ADG506的通道选择控制端(A3~A0);P为ADG506选通信号,接ADG506的片选端(EN)。

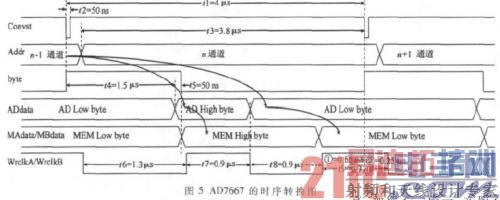

由于存储器采用双备份设计以及对两片存储器的写入操作完全相同,故采集控制逻辑中分别有控制A、B片存储器的控制信号wrclkA和wrclkB,数据通过MAdata、MBdata分别存入存储器的A、B片中,如图5所示。

图5[3]是FPGA的时序转换图。其中,Convst为启动转换信号;Addr为通道地址;byte信号用于控制数据并行输出的模式,低电平为低8位数据,高电平为高8位数据;ADdata 连接到AD7667的数据输出端;数据通过ADdata输入到FPGA。

图5的数据转换过程:A/D转换器的数据采集是从Convst信号下降沿开始,Convst下降沿启动对n-1通道的采样转换, 进入转换进程后,通道地址信号a和p根据帧计数切换到采集通道n, 在等待足够的转换时间t4后,AD7667在byte高电平的控制下从AD[7:0]输出n-1通道高8位的转换数据,高8位数据在写时钟Wrclk的控制下,以足够的时间传输给缓存器,AD7667在byte低电平的控制下从AD[7:0]输出n-1通道低8位的转换数据,低8位数据在写时钟Wrclk的控制下,以足够的时间传输给缓存器,并在传输的同时进入n通道的采集过程,此时n通道信号在经过了时间t3后,已经达到稳定的电平。

在采集的过程中测得的Convst信号波形与运放的输出波形如图6 (a)、(b)所示。

图6 (a)、(b)中,CH1通道为Convst信号,频率约为250 MHz(采样周期4 μs),CH2通道为运放输出信号。 图6(c)、(d)分别为用LM224和LF247作为运放时采集数据的回放波形。从图6 (a)、(b)可以看出,在开关切换的过程中,运算放大器输出的信号存在剧烈抖动。图6(a)中测得的是用LM224作为滤波跟随器(SR为0.3 V/ 滋s)的输出信号,此滤波放大器的输出抖动直到ADC采样前还未稳定,导致采集到的数据波形出现严重失真,如图6(c)所示;在图6(b)中的竖线处,运放的输出也存在一定的抖动,然而,由于滤波运放采用LF247(该运放的SR为16 V/ 滋s),其输出在ADC采样前已经稳定到极高的精度,所以用该运放作为滤波跟随器采集到的数据波形非常准确,如图6(d)所示。

由此可以看出,与传统的流水线顺序相比较,由于硬件描述语言VHDL进程之间具有并发特性(进程(1)与进程(2)的并发性),这样就必然节省了通道切换、采样和保持的时间,同时结合硬件,选择合适的运放,即可保证ADC转换之前转换通道信号的稳定,这就解决了通道串扰问题。

3.2 存储逻辑设计

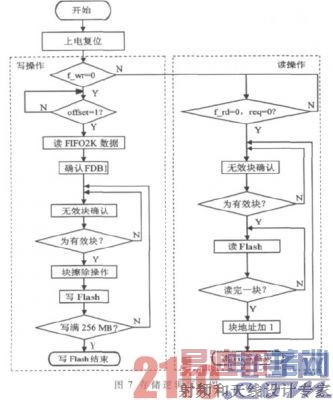

存储逻辑主要包括对Flash的擦除、读写及识别无效块。控制流程图如图7所示。

存储器默认为读状态,上电复位时间设置为0.8 s,复位完成则判断是否处于写状态,若是,则记录采编器传输的数据,若否,则在读请求信号有效时(低电平有效),送出Flash芯片内所存数据,送完256 MB自动停止。若中间读请求信号无效,存储器停止送数,维持当前状态,并等待请求信号再次有效。

当存储器处于写状态时,A、B片同时完成数据的记录;当处于读状态时,在各自读请求信号有效时,分时复用采编器数据总线,先后将两套存储器数据上传。1#存储器为默认优先上传存储器,通过设置采编器通道切换信号为有电流状态,可选择2#存储器上传数据。

备用读数状态下,分别读取两套存储器。

4 测试试验

对数据采集存储系统进行炮击试验,其目的是为了考核记录器的外部结构以及内部电路板的抗过载能力。试验前,采编器采集标准的模拟弹上信源(正弦波、方波、直流量、锯齿波……依次循环),并存入存储器,然后将整个系统安装在飞行体中,飞行体以极高的速度着靶,测试采集存储系统的冲击过载能力。试验后电路板正常无损坏,而其中一块(B片)外部晶体振荡器损坏,因此,存储器采用双时钟源,正常情况下由晶体振荡器提供时钟源,在存储器回收后读取数据时,若晶体振荡器损坏,可由地面测试台提供的备用时钟作为存储器时钟源,这样就避免了回收存储器后更换晶体振荡器的麻烦。试验完成后从A片存储器中回收数据,并与试验前的数据相比较,结果一致,再从B片存储器中回收数据(由于外部晶体振荡器损坏,需用备用时钟源),与试验前的数据相比较,其波形一致,如图8所示。图8中列举了其中4个通道T1~T4的电压信号,试验表明,该系统具有很强的抗过载能力。

本文给出了基于双备份存储器的数据采集存储系统的电路设计和控制逻辑设计。在工程实践的基础上,对多通道异步时分电路的通道串扰现象提出了可行性的解决方案,同时详细地介绍了采用FPGA实现采集控制逻辑以及存储逻辑的方法,也给出了采集控制逻辑的流程和存储逻辑的设计流程。通过飞行试验,该采集存储系统采集了用来评估飞行器的各种技术指标的有用数据,实践证明,双备份设计有效的提高了数据回收的可靠性。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:采用欧氏算法和频谱结构分析相结合的RS硬件解码方案设计

下一篇:Verilog

HDL硬件描述语言:task和function说明语句的区别