- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

通用CPCI数据处理与IO模块的设计与实现

摘要:数据处理与IO模块主要完成数据计算、模拟和数字信号的采集与处理等功能。给出一种通用的CPCI数据处理与IO模块的设计方案,模块采用满足CPCI总线规范的加固型设计,可以实现主控模块和外设模块的自适应转换。讨论了处理器功能电路设计、IO功能电路设计和通用CPCI接口设计,并针对模块功能设计进行验证。

0 引言

嵌入式数据处理与IO模块应用在抗恶劣环境中,主要完成数据计算、模拟和数字信号的采集与处理等功能。随着嵌入式系统对数据处理性能需求的逐步提高,PowerPC微处理器由于其RISC架构、高主频、并行矢量处理技术已经成为许多高性能系统的优选处理器。同时为了提高数据处理与IO模块的开放性、扩展性和维修性,需要采用成熟的标准PCI总线对模块进行规范化、通用化设计Compact PCI(简称CPCI)总线是国际工业计算机制造者联合会于1994年提出来的一种总线接口标准,是以PCI电气规范为标准的高性能工业用总线。CPCI总线充分利用了PCI总线的优点,在电气、逻辑和软件功能方面与PCI总线完全兼容,同时具有热插拔能力,已经广泛的应用在通信与网络、工业自动化等领域中。满足CPCI总线规范的模块采用加固型的结构设计和高可靠的连接器,具有较高的可靠性和较强的环境适应能力。

1 系统架构

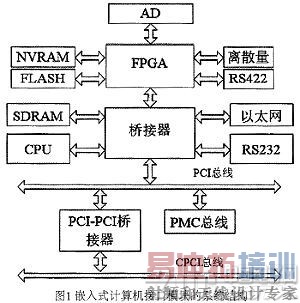

数据处理与IO模块为6U结构,底板采用标准的CPCI连接器。功能电路主要由CPU、CPU桥接器、FLASH存储器、SDRAM存储器、FPGA逻辑电路、AD接口、离散量接口、以太网调试接口、RS232串行接口、RS422串行接口、PCI—PCI桥接器等组成,系统结构如图1所示。

模块的设计采用结构化、层次化的设计方法,各层设计的功能相对独立,各个功能子模块的功能明确。CPU通过桥接器和FPGA实现与板内资源的交互,桥接器同时实现存储器控制器接口,可以直接对接DDR2存储器,处理器,PCI接口都可以通过桥接器对存储器进行访问。模块上提供2路标准的66MHz/64位数据宽度的PMC接口,用于模块的性能、功能扩展,PMC总线通过PCI总线跟桥接器相连。模块内部PCI总线和底板CPCI总线采用PCI—PCI桥接器隔离,使用时可以进行灵活的配置。

2 处理器功能电路设计

2.1 处理器电路设计

CPU模块采用处理器PowerPC 7447A,PowerPC7447A是PowerPC系列处理器中的第四代高性能的处理器,是一款高性能、低功耗,32位精简指令集结构的处理器。处理器主频为1000MHz,可以通过跳线根据PC7447A的手册来更改主频,为节省能耗CPU模块降频到600MHz使用。

处理器通过桥接器访问自己的资源,处理器的资源主要有:DDR2 SDRAM,Flash存储器,NVSRAM存储器,串行接口,PMC接口,以太网接口,中断控制器,可编程看门狗电路等。

处理器桥接器采用Tsi109,桥接器/集成存储器控制器提供PowerPC74XX处理器到PCI总线的接口,Tsi109提供功能有:一个高性能的存储器控制器,两处理器的支持,两通道DMA控制器,一个中断控制器,一路消息控制器,一路I2C接口,一个时钟锁相环电路等。

2.2 复位电路设计

复位电路主要由MAX706ESA芯片实现。模块上电时,FPGA需要配置,在配置过程中IO引脚保持三态,此时输入到MAX706ESA的手动复位通过下拉电阻下拉为低电平,使模块处于复位状态,待FPGA加载完成后,FPGA该IO引脚通过逻辑输出为高,手动复位结束。在工作中通过手动复位可以对模块进行复位,如果MAX706ESA检测到电压+5V低于+4.4V时,产生复位。

3 IO功能电路设计

3.1 AD接口设计

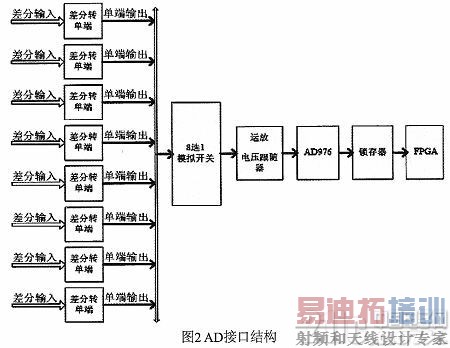

模块提供8路差分AD来完成模拟数据的采集,8路差分模拟量输入在模块内首先被转换成8路单端输入,经过模拟开关后进入AD转换芯片,AD的并行接口输出经过锁存器后进入FPGA,模拟开关与AD芯片之间加运算放大器和电压跟随器。AD接口结构如图2所示。

AD转换芯片选用AD公司的AD976,16位采样精度,采样速率100KSPS,输入电压为±10V,AD976主要由R/C和CS信号控制转换,设计中这俩信号由FPGA实现,软件中只需向FPGA内的一个地址写入低电平,FPGA便会输出R/C和CS两个低脉冲,从而启动AD转换。

3.2 串行接口设计

模块提供8路RS422接口,采用EXAR公司的通用异步收发器XR16C864来实现,该芯片具备4路数据通道,每通道FIFO字节128字节,波特率最高可达2Mbps。可以通过芯片寄存器操作实现接口的操作配置、状态查询、错误管理、中断控制等功能。模块上通过FPGA的控制逻辑实现处理器对协议芯片的配置管理和接口中断控制等功能。

在Vxworks中,串行设备是一种特殊的字符型设备。为了方便操作,软件中调用ttyDevCreate函数将RS422创建为标准的串口设备。应用程序编写时可以完全忽略底层硬件,将RS422看成是IO文件系统的设备,采用iolib系统库提供的接口函数open()、wrire(),read(),close(),ioctl()等函数来对设备进行操作。

4 通用CPCI接口设计

4.1 硬件设计

模块采用CPCI总线,由于要实现主控模块和外设模块的自适应转换,设计中采用PCI6466做为模块内部PCI局部总线到CPCI底板总线的桥接器。PCI6466是PLX公司设计的功能强大的工业用双模式通用PCI到PCI桥接器,可以在桥的主端和从端实现完全异步的操作。PCI6466有透明模式、非透明模式和通用模式三种工作模式,设计时可以根据需求进行灵活的配置。

透明模式工作时,桥的从端的所有设备对主端的主系统是透明的,从端的所有设备只能由主端的主系统对其进行配置和控制,主端和从端的时钟一般必须同步,主端和从端的地址完全透明,在主端和从端之间的地址传递是直接传输,不用进行地址转换。

非透明模式工作时,桥的两端是两个独立的处理器域,从端的资源和地址对主端的处理器是不可见的。允许从端的本地处理器独立地配置和控制其子系统,主端和从端的时钟可以同步或异步。主端和从端的地址完全独立,主端和从端的地址由桥来进行转换。

通用模式下可以通过TRANS#信号将PCI6466设置为通用透明模式和通用非透明模式。为实现模块的主从自适应转换,在本设计中PCI6466被配置为通用模式。

在通用模式下,PCI6466的TRANS#信号可以直接连接到CPCI总线的SYSEN#管脚,SYSEN#管脚是系统主控模块使能信号,CPCI底板中系统槽将它接地,外设槽将该信号拉高。当模块插入系统槽时,SYSEN#信号为低,PCI6466工作在透明桥模式。反之,如果模块被插入外设槽,SYSEN#信号为高,PCI6466工作在非透明桥模式。这样就可以实现模块的主从自适应转换功能。

4.2 PCI接口驱动

VxWorks操作系统中提供了对PCI驱动的良好支持,并且可以根据实际情况进行裁剪,PCI接口驱动开发按照如下步骤进行。

1)PCI配置空间初始化。通过调用PCI配置空间初始化函数完成PCI配置空间的初始化;

2)查找PCI设备。通过函数pciFindDevice来实现PCI设备的查找。该函数可以根据给定的Vendor ID和Device ID来扫描总线,找出设备所在的Bus No、Device No和Func No。

3)地址空间映射。通过操作系统提供的函数访问PCI设备的配置空间,配置PCI设备的基址寄存器、中断、ROM基地址寄存器等,这样可以得到PCI设备的存储空间和I/O地址空间映射、设备的中断号等;

4)具体的设备驱动。根据PCI设备的配置参数,对不同的PCI设备编写初始化程序、中断服务函数以及相应的功能函数。

5 模块功能验证

完成系统和驱动软件的设计后,在具体应用环境中对系统的功能和性能进行验证,系统验证了如下功能:

(1)模块的数据处理功能,利用测试程序对CPU、SDRAM、FLASH、NVRAM等基本CPU资源进行验证,各部分功能正常。

(2)模块的IO功能,利用测试程序对模块的AD、RS422等功能进行验证,AD精度满足要求,RS422数据传输正常。

(3)CPCI的主从自适应功能,在测试工装中分别把模块插入系统槽和外设槽,模块能自动的识别并设置自己的角色,作为主设备时可以完成对外设的配置,作为外设时可以在PCI设备列表中扫描到。

6 结语

本文介绍了一种通用CPCI数据处理与IO模块的设计与实现,满足CPCI总线规范的模块采用加固型的结构设计和高可靠的连接器,具有较高的可靠性和较强的环境适应能力。模块经过系统的测试验证,具备通用性、高可靠性的特点。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:基于SOC的星载微型GNSS接收机设计

下一篇:PCB单点与多点接地有什么区别