- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的电子表决器电路的设计与实现

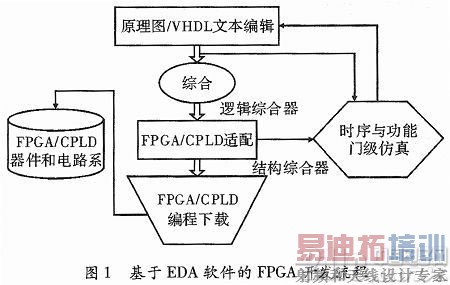

电子设计自动化(Electronic Design Automation,EDA)是以计算机为载体,在EDA软件平台上,用硬件描述语言VHDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。EDA技术的出现,大幅提高了电路设计的效率和可操作性,减轻了劳动强度。利用EDA工具,电子设计师可从概念、算法、协议等方面开始设计电子系统,大量工作可通过计算机完成,并可将电子产品从电路设计、性能分析到设计出PCB版图的整个过程都在计算机上自动处理完成。基于EDA软件的FPGA开发已广泛应用于电子电路的设计与实现中,图1为基于EDA软件的FPGA开发流程。

1 电子表决器电路

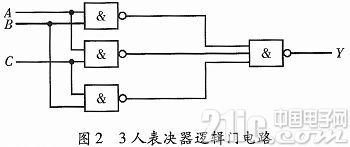

传统的电子表决器通过逻辑门电路实现、功能简单、不易扩展,表1是一种3人表决器的真值表,图2是由逻辑门组成的电路图。

2 基于FPGA的电子表决器

2.1 8人表决器电路

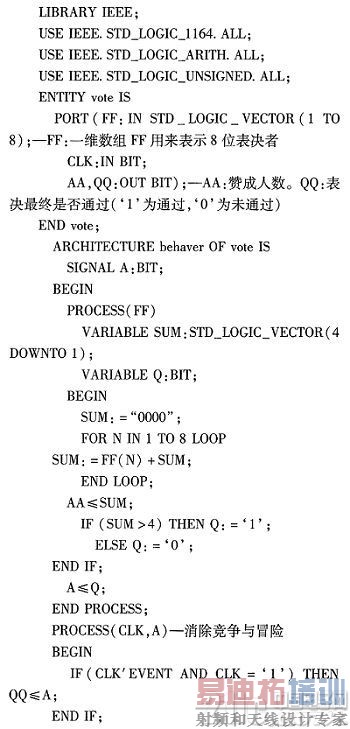

结合VHDL语言在FPGA平台实现电子表决器电路设计,可减小系统面积,方便扩展升级,以下程序是使用VHDL语言描述的8人表决电路。

2.2 10人表决器电路

通过8人表决电路表决通过时电路状态的观察和验证,使用VHDL语言在FPGA平台实现10人表决器电路设计。在8人表决器编程基础上修改程序,实现10人表决器电路的设计。编程中完成参与表决的每个人均可选择赞成、放弃或弃权。同时,增加了控制键,可增加专人在进行表决过程中的控制,实现了表决的开始、结束和数据的锁存。

3 电路仿真

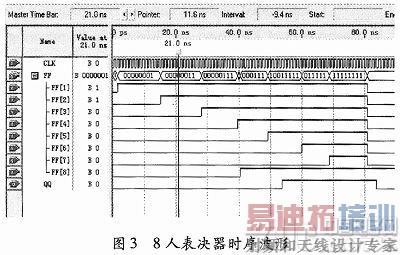

图3是8人表决器电路时序波形,从图中可看出程序实现了设计要求,在8人表决器程序的RTL生成电路界面显示有9个逻辑门和硬件资源组成电路。

按图4所示进行管脚锁定后,即可在实验箱上进行验证,将程序下载到实验平台后,获取实验结果,经验证符合设计要求。

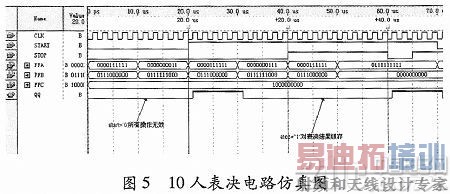

图5为程序仿真结果。在10人表决器的RTL电路界面图中可看出,其比8人表决器程序的RTL电路界面图多出了一些硬件资源,若单独使用逻辑门设计电路将是一件复杂的工作,且不便于修改和测试。

而使用EDA进行设计,还可方便地进行系统扩展,如上述程序中只需增加几个输出端口,将SUMA,SUMB,SUMC的值赋给相应端口,在外接数码管便可显示出赞成、反对、弃权的人数。或增加声音模块,使系统更具实用价值。而进行这些工作只需改变程序,加入现成的元器件即可。

4 结束语

电子表决器,做为投票系统中的客户端,是一种代表投票或举手表决的装置。基于FPGA电子表决器的设计解决了传统投票表决方式存在投票耗时长、计票任务重,且易于出错、易受人控制等缺点,故在表决、选举中获得了广泛应用。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...