- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

利用Xilinx Zynq SoC简化您的“热”测试

本文介绍一种使用Zynq SoC和赛灵思IP核简化高速光学收发器模块热测试的方法。

随着数据中心内部光学收发器模块的传输速度提高到前所未有的高度,数据中心内每个机架的温度也在不断大幅上升。机架中有多个这种发热的高速模块堆叠在一起,加之有多个机架并排摆放,这样,温度倍增。温度的急剧上升可能会导致超过芯片的热限制,从而造成灾难性的芯片故障,继而对整个数据中心系统产生不利影响。因此,工程师在设计光学收发器模块时必须考虑到热属性。设计人员必须要将注意力集中在热源上,并尝试用模块级甚至机架级的高效冷却方法对热源加以控制。

工程师在测试光学模块的热属性时通常有两种选择。他们可以使用复杂的网络数据生成器来创建高速(10-Gbps)链路,然后对光学模块的热属性进行测试;或者充分利用具有可调预设电压和电流的“热等效”模块,这样无需使用真正的高速数据即可仿真模拟热学条件并评估热属性。

这两种方案都不够理想。第一种方案需要专业的高速网络数据生成器,因此操作起来成本很高;而第二种方法又太抽象。热等效模块无法完全反映物理交换行为所引起的温度变化。

不过,最近我的团队在爱尔兰阿尔卡特朗讯贝尔实验室通过使用赛灵思Zynq®-7000全可编程SoC 平台和赛灵思IP核完成光学模块的热属性测试工作,从根本上简化了这一过程。我们来仔细了解一下如何成功简化测试。

预设计分析

这种热测试的基本要求是不断用10Gbps数据激发XFP光收发器,同时使用IR摄相头跟踪和描述温度变化特性。

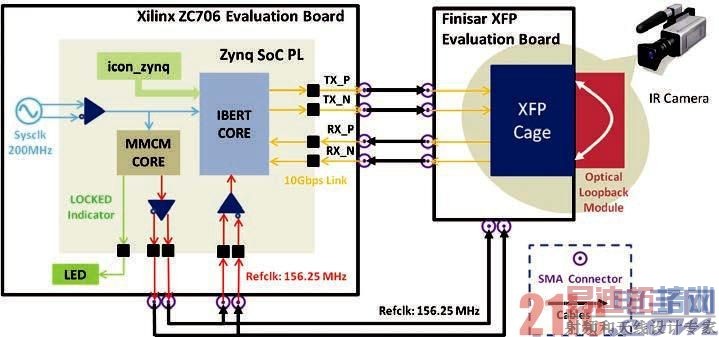

我选择赛灵思ZC706评估板作为开发主机,因为主器件——即Zynq-7000 SoC XC7Z045(速度等级-2)上的GTX收发器可以轻松达到10Gbps的单线数据传输速率。Zynq SoC器件包含一个采用ARM®内核的处理系统(PS)和一个Kintex®-7FPGA可编程逻辑(PL)架构。首先, PL晶片上的资源足以处理10Gbps双工数据传输。然后,我们可在日后需要的时候使用PS生成特定用户数据模式。

我们的热学团队将一块Finisar XFP评估板用作光学收发器的外壳。该FDB-1022评估板可作为功能强大的评估主板,能够很好地评估最先进的10Gbps XFP光学收发器。SMA连接器可用于差分数据输入和输出。该评估板经配置后可直接通过SMA连接器连接1/64时钟(即,156.25 MHz = 10 GHz/64),进而为模块提供时钟。

系统设计

在进行FPGA开发工作的七年时间里,

图1 – 所建议的系统的方框图,包含连接实例。

我发现尽可能多地使用赛灵思内核可以显著缩短设计周期。在本设计中,我采取了相同的策略,并从集成式误码率测试器(IBERT)内核开始着手。您可利用该内核进行数据模式的生成和验证,从而评估Zynq SoC上的GTX收发器。然后,为了对设计正确布线,我创建了一个基于混合模式时钟管理器(MMCM)内核的相位对齐时钟分布单元,可同时对FPGA架构上的GTX收发器和XFP评估板上的光学收发器提供时钟。图1为系统方框图。

针对该设计项目,我使用了赛灵思的老式工具ISE®设计套件,并分三步完成这项工作。

第一步,使用CORE Generator™工具创建IBERT内核。这里提供了一些针对该IBERT 7系列GTX(ChipScope™ Pro)IBERT内核的关键设置。在我的设计中,IBERT系统时钟来自开发板上的外部时钟源,即200MHz差分时钟,P引脚位置= H9,N引脚位置= G9。GTX时钟模式独立于QUAD 111;并且我将线路速率设置为最大速率= 10Gbps。我把GTX的参考时钟设置为

Refclk = 156.25 MHz,且Refclk时钟源= MGTREFCLK1 111。

第二步,我使用CORE Generator创建了一个MMCM内核。首先必须正确设置该工具的时钟向导。为此,我将时钟特性设置为频率综合和相位对齐。输入时钟必须与开发板上的系统时钟相同 (即200MHz)。我还将目标派生时钟设置为156.25MHz,占空比设置为50%。我使用两个额外信号(RESET和LOCKED)来控制和指明MMCM内核。

图2 – ChipScope Pro屏幕截图

第三步,用赛灵思工具对所有元素进行集成。在本项目中,我使用的是ISE设计套件14.4。以后我打算改用Vivado®设计套件,以便最大程度地提高芯片性能。

我首先在ISE中创建一个新的项目,然后将IBERT内核文件夹(example_ibert_gtx.vhd、ib- ert_gtx _top.ucf、ibert_core. ngc和icon_zynq.ngc)移动到ISE项目中。然后,从MMCM内核文件夹(步骤2)将mmcm_core. vhd添加到ISE项目。再然后,将example_ibert_gtx.vhd用作顶层模块,对mmcm_core进行实例化,并将三个新信号(CLK_ OUTPUT_P、CLK_OUTPUT_N和LED_REFCLK)添加到设计中,随后在ibert_gtx_top.ucf中进行相应的引脚分配。

系统测试

在生成.bit文件后,FPGA设计就可随时用于仿真具有10Gbps链路的XFP光学收发器。我把两块开发板连接起来(如图1所示),然后打开ChipScope Pro分析器,用新建的.bit文件配置器件。接下来,双击IBERT控制板,会弹出一个新的图形用户界面(如图2所示)。我们可以使用该界面对预定义的数据模式进行优化,例如Clk 2x (1010….),以及伪随机二进制序列(PRBS),进而彻底评估光学收发器的热性能。

通过将赛灵思内核与ZC706评估板结合起来使用,即可轻松构建用以评估高速光学收发器的测试平台。在本设计中,我们展示了对单个XFP模块的评估。不过,您可以直接应用这种设计方法来快速构建一个用来测试多个光学收发器模块的逻辑内核。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...