- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

用Vivado IPI和赛灵思IP实现更快速的设计输入

本文将介绍如何优化赛灵思内核以便在CPRI远程无线电头端设计中使用Vivado IPI。

新型基于FPGA的设计使用IP核的数量和种类日趋繁多。Vivado®设计套件中的IP集成器 (IPI) 工具和赛灵思通信IP让设计人员能够更加轻松快速地将IP模块连接在一起。

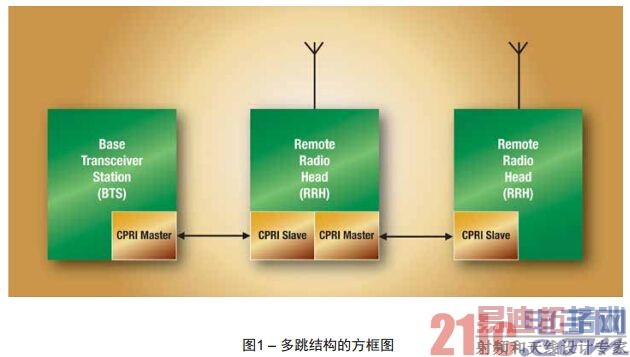

为了更好地阐明IPI方法的强大之处,我们以远程无线电头端 (RRH) 为例。RRH位于天线附近,构成蜂窝通信网络的一部分。它们通常通过光纤连接至上游的基带收发器站,并可以选择性地连接到下游的更多RRH,从而构成多跳拓扑结构(图1)。

通用公共无线电接口 (CPRI) 协议普遍用来连接这些RRH。现在让我们来构建包含一个上行链路CPRI端口和三个下行链路CPRI端口且这些端口连接在一起的实例设计。我们可以利用IPI构建出整个设计中的主体部分。然后我们选用Kintex®-7器件,因为该器件具备低功耗、低成本和高性能等优异特性,因此非常适合此实例设计。速度等级为-2的All Programmable 器件Kintex FPGA和Zynq®-7000 SoC中的GTX 收发器支持使用9.8Gbps CPRI线路速率。

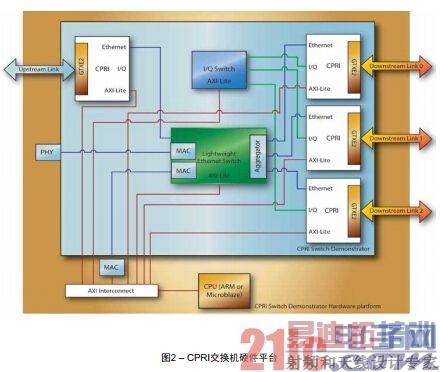

图2展示了我们在IPI中将要创建的内容。我们可建立模块设计,并从IP Catalog中实例化所需的IP。标准赛灵思IP Catalog中提供有CPRI内核。该内核经过优化,不仅可实现资源共享(可能情况下),而且还能简化在IPI中的使用。交换机属于自定义IP。

IP核资源共享

使用多个IP实例时客户遇到的挑战之一是如何高效共享资源。很多通信IP核都支持“共享逻辑”功能。对于CPRI内核,我们可用内核中的可共享逻辑资源配置IP,或者省略这些共享资源。如果共享资源包含在内核之中,它们会提供必要的输出以便让我们将共享资源连接到不含这些逻辑的内核。

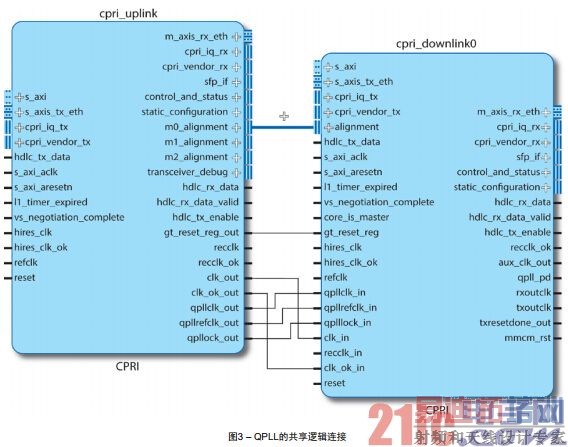

有特殊要求的用户可能希望在内核中移除这些共享逻辑并实现自己的逻辑。在我们的实例设计中,我们将CPRI内核的运行速度配置为9.8Gbps。这该线路速率下,有必要使用LCtank振荡器来提供收发器时钟。Kintex-7器件中的收发器采用Quad布局,每个收发器Quad包含四个收发器通道和一个基于LC-tank的Quad锁相环 (QPLL)。所有内核都有必要共享QPLL以及由上行链路时钟信号生成的时钟。图3中给出了带有定制共享逻辑的上行链路内核上QPLL和时钟输出端口,该上行链路内核的共享逻辑连接到将不含共享逻辑的下行链路CPRI内核的相应输入端口。

CPRI内核间的数据路由

我们还进行了IQ交换机和以太网交换机的实例化,以便让数据在内核之间实现路由。

CPRI网络中的控制和管理数据通过以太网子通道发送。凭借系统中的以太网交换机,可以远程发布固件升级或命令,并将其发送至任意节点。IP旨在使用尽量少的逻辑资源,因为这种情况没必要使用功能齐全的以太网交换机。

IQ交换机能以确定的时延在CPRI内核之间路由任何IQ样本。多跳无线电系统的一个重要特性是可以准确测量链路延迟,而且CPRI标准定义了一种能够协助该测量的方法。

用IPI连接接口

IPI总线接口将定义好的一组逻辑端口映射到IP上的特定物理端口。如果我们尽可能地使用接口,就可以从连接很多信号转变为连接少量接口。IP上的通用总线接口是符合ARM® AXI标准(例如AXI4-Lite和AXI4-Stream)的接口。这种抽象程度的提高使设计输入更简单、更快速,而且使您能够充分利用接口的设计规则检查功能。Vivado IP Packager允许您在IPI中使用自己的IP,并在自己的设计中利用这些接口。

IPI便于将接口连接在一起。只需点击接口,IPI就会指示其可以连接至具体内容。将连接线拖拽到所需的端点,就会建立起来连接。利用该方法,只需点击几次就可连接很多信号。

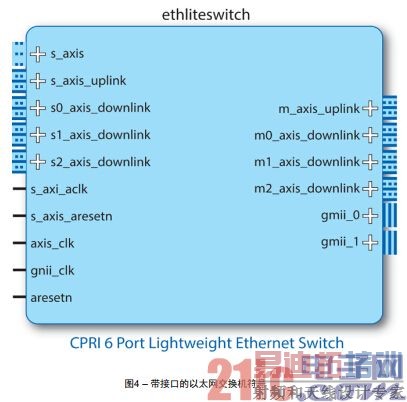

图4显示的以太网交换机提供若干AXI4-Stream接口,两个GMII接口,以及一个AXI4-Lite接口。数据流接口能直接连接到CPRI内核,这样无需在CPRI内核上进行内部缓冲。GMII接口能连接到以太网PHY,可供工程师在现场调试网络问题。AXI4-Lite管理接口用来访问地址表格映射及其它配置选项,例如地址表格老化间隔。

我们继续以这种方式增强系统,在IPI中连接各个接口。您可以灵活地使用任何最适合的输入方法。除了使用GUI连接接口外,还可以通过Tcl控制台直接发命令,或者从脚本获得命令。每次在GUI中做任何操作时,就会返回相应的命令。

整个设计完成后,使用“write_bd_tcl”命令将整个设计导出。该命令创建一个可引用的Tcl文件,用以从头创建整个模块设计,或方便地作为脚本构建流程中的一部分。设计中的所有IP都提供一个AXI4-Lite管理接口,以便让内核连接到主机处理器。IPI中内置的智能功能可以实现自动化连接。凭借这种机制,IPI就能识别出IP上的AXI4-Lite接口将连接到AXI总线互联,并自动配置合适的地址范围,为我们连接到总线。然后,您可借助IPI将该总线连接到主机处理器。本案例中的主机处理器是MicroBlaze™,不过若使用Zynq SoC系列器件,就能方便地将主机处理器改为ARM CPU。

更多优势接踵而至

Vivado IPI功能正在快速增加,以后还将带来更多优势。通过使用正确的IP,我们可以将整个子系统快速集成在一起,并从中受益。

如需了解有关CPRI、以太网交换机或IQ交换机IP方面的更多信息,请发送邮件至:permind@xilinx.com,与赛灵思无线通信部的Perminder Tumber 取得联系。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...