- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

UltraScale为高带宽设计带来板载Interlaken

赛灵思在其UltraScale FPGA上集成了Interlaken IP,可简化包处理系统互联。

带宽是个有趣的东西。十年前,大多数人都不清楚什么是“每秒字节”。而今天,在线视频、智能手机和各种现代化互联社会不可或缺的设备让带宽成为所有人关注的问题。这些应用告诉人们,带宽非常重要,人们也清晰地意识到需要更高的带宽。

遗憾的是,高级堆栈顶层观点会制约为家庭以及便携式设备提供更多比特与字节所需的技术发展。所有这些数据都要求我们的基础设施必须跟上发展要求。过去依靠10Gbps光学技术的互联机制现在已经发展到40乃至100Gbps,而不久的将来还有望推进到400Gbps。

当今产业中的INTERLAKEN

在整个过程中,基础包处理任务和架构并没有发生巨大变化。同样,100Gbps系统面对的许多封装、功耗和热性能限制与其前代技术也一样。这意味着系统所有组件都需要大幅提高速度。更重要的是,这些器件之间的互联必须能够很容易扩展。系统中使用的FIC、NPU、MAC及其它ASSP来自众多不同的供应商,这导致问题进一步复杂化。这些器件采用各种互联宽度和速率来实现目标吞吐量。

现在,赛灵思和Interlaken协议已着手协助解决包处理功能之间的社交互联瓶颈问题。由思科和Cortina合力打造的Interlaken旨在应对这些挑战。赛灵思 FPGA可通过高性能可编程逻辑和高性能收发器轻松实现这项标准。以下三个方面使得Interlaken成为应对这些难题的最佳协议:其具备高度可扩展性;Interlaken非常适用于OTN 和以太网系统;它是一项开放式协议。

从最基本的层面说,Interlaken旨在最大限度地提升灵活性和可扩展性。该规范没有强行要求预定义的线路速度或信道宽度。举例来说,这意味着您实现150Gbps的接口就能对100G以太网数据路径(带其它包头)进行封装,12条信道每条线路12.5 Gbps或者六条信道每条分别为25 Gbps。无论哪种情况,Interlaken的逻辑接口均可得到保持,同时简化了其它设计。此外,这种灵活性也使Interlaken适用于细分市场应用,如与TCAM协同工作的后备接口。

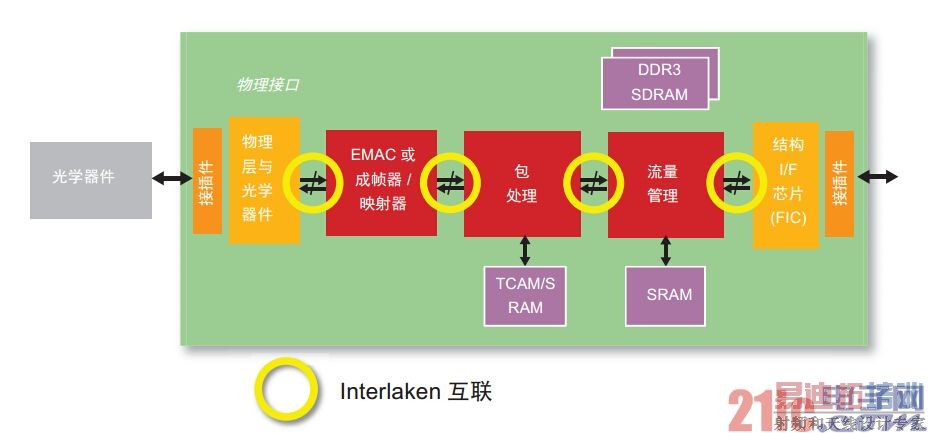

Interlaken在包处理过程中的潜在位置

图1 – 利用Virtex UltraScale的32.5-Gbps GTY高性能收发器(如本视频所示)和集成式Interlaken模块,客户能够在不影响灵活性的同时创建性能更高、功耗更低、集成度更紧密的网络。

无论数据通过多少条信道传输,都要在这些信道上进行分段和拆分。这种方法的优势在于能够减少时延,同时能很好地支持OTN流或以太网数据包。在分段过程中,Interlaken可支持信道化,让设计人员能够灵活地实现数据包优先化等特性,同时能在协议现有的特性集中工作。

图2 – 利用Virtex UltraScale的32.5Gbps GTY高性能收发器(如本视频所示)和集成式Interlaken模块,客户能够在不影响灵活性的同时创建性能更高、功耗更低、集成度更紧密的网络。

Interlaken具有丰富的特性集,而且无需注册,可免费使用,因此非常适合推广。此外,原始定义中包含了各种利益相关方公司,这意味着Interlaken的特性集也能方便地满足多种不同需求。由于能迅速获得各种ASSP和IP,赛灵思FPGA的使用和推广都变得更方便。

赛灵思和INTERLAKEN:一对完美的组合

赛灵思素以帮助设计人员更方便地采用最新高性能标准而闻名。在向100 Gbps乃至更高技术转移的过程中,实践证明赛灵思器件在包处理系统和测试设备方面发挥了重要的主导作用。由于100G以太网MAC、OTU4和Interlaken解决方案的高质量IP随时可供使用,因此配合赛灵思的高速FPGA结构和世界一流的收发器能够为客户带来灵活而强大的解决方案。

从Virtex®-5代开始就面向赛灵思 FPGA提供了Interlaken IP,一开始是通过第三方厂商提供,而在收购了Sarance之后,则是由赛灵思自己提供。UltraScale™系列FPGA是提供Interlaken解决方案的第四代赛灵思器件,其取得了一项重要发展。

在UltraScale FPGA中,赛灵思将Interlaken IP整合到芯片中。通过将Interlaken设为固定的特性,赛灵思能够释放出更多结构逻辑,减少软实现技术带来的时序约束,从而将设计人员从繁重的工作中解脱出来。此外,这款一体化解决方案还能节约动态和静态功耗,而且不会对灵活性造成不良影响。统一的Interlaken模块能以任何线路速度实现多达12条信道,每条信道速度高达12.5 Gbps,或者实现六条信道,整体速度高达25 Gbps。

赛灵思在Interlaken的优势基础上进一步发展

集成式Interlaken IP只是让赛灵思UltraScale FPGA具有巨大吸引力的其中一个因素。赛灵思UltraScale FPGA拥有可支持不同线路速度的大量特性丰富的收发器、高级高速可编程逻辑以及用于MAC解决方案的集成IP软核,并能实现新兴标准,任何其它FPGA或ASSP都无法达到类似的水平。

UltraScale FPGA中的GTH和GTY收发器具备许多特性,能使其在各种不同条件下工作。GTH的线路速度从500 Mbps到16.3 Gbps不等,GTY的运行速度可达32.75 Gbps,可确保FPGA能够支持链路合作伙伴所需的任何线路速度(敬请参看YouTube演示和图2)。这些收发器的均衡功能(包括连续时间线性均衡和决策反馈均衡),能帮助用户将板上其它器件的任何元素与光学器件或背板远端的器件相连接。

为了更方便地启动这些高速互联,无论是100G以太网、OTU 4.4还是Interlaken宽接口,所有收发器均衡特性均为自适应性。这就意味着在GTY中CTLE的三个抽头和DFE的15个抽头之间,收发器自身就能处理由此形成的数百万种组合。设计人员无需手动调节每条链路并保持工艺、电压和温度变化条件下的链路容限。Interlaken可支持无限宽的接口,因此自适应性能够确保启动工作简单而稳健。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:三栅极技术给FPGA带来突破性优势

下一篇:广大市场受益于采用低成本FPGA的MIPI

DSI显示屏和应用处理器