- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

三栅极技术给FPGA带来突破性优势

本文考察了半导体制造业中晶体管设计从传统平面向3D结构转化的影响,以及其对可编程逻辑器件性能的显著提升。

引言

2013年2月,Altera公司与Intel公司共同宣布了Altera下一代最高性能FPGA产品的生产将独家采用Intel的14nm 3D Tri-Gate(三栅极)晶体管技术。这使得Altera成为当前采用最先进、最高性能半导体技术的独家专业FPGA供应商。本文介绍了三栅极及相关技术的历史与现状,以便了解三栅极技术对高性能FPGA性能的影响,以及其在数字电路速度、功率以及生产方面有何种程度的优势。

晶体管设计的背景

1947年,贝尔实验室展示了第一支晶体管,采用的是锗“点接触”结构。1954年,硅被首次用于制造双极型晶体管,但直到1960年才出现了第一支硅金属氧化物半导体场效应晶体管(MOSFET)。最早的MOSFET为2D平面器件,其电流是从栅极下的硅表面上流过。在大约50年的时间里,MOSFET器件的基本结构实际上维持不变。

自从1965年摩尔定律提出以来,MOSFET工艺有了许多的改进与提高,这反过来也使摩尔定律越来越深入人心,并应用于半导体产品规划中。过去10年来,由于在应变硅和高K金属栅方面的技术突破,MOSFET的性能与功耗一直在持续得到改善。

直到1991年,日立中央研究实验室的Digh Hisamoto和另一研究小组发表了一篇论文,人们才认识到了3D(或“环绕”)栅极晶体管技术的潜能,它能增强MOSFET性能,并消除短沟道效应。该论文将所述3D结构称为“耗尽型l沟道晶体管”,或DELTA。

1997年,美国国防部高级研究计划局将一个合约授予伯克利加州大学的一个研究团队,要求开发一种基于DELTA概念的深亚微米晶体管。该项研究结果最早发布在1999年,该器件被叫做“FinFET”,因为晶体管几何结构的中心呈鳍状。

晶体管技术的重要转折点

各家领先半导体公司的研发部门都在不断地研究3D晶体管结构的优化与可制造性。有些工艺与专利进展已经发表和共享,而有些仍保留在企业实验室中。

半导体业研发投入的推动力是国际半导体技术发展路线图(ITRS),它由一些制造商、供应商和研究机构组成的一个联盟负责协调和发布。ITRS提出可实现性能、功耗与密度不断改善的晶体管技术需求以及实现这些目标的相应的研究项目。ITRS及其公开出版物通过有关应变硅、高K金属栅以及现在的3D晶体管技术等的制造能力的结论与建议,来确保从摩尔定律获益。按照ITRS提供的文件,以及对学术论文与专利资料文档的分析,最近十年来3D晶体管技术的研究已经获得了长足的进步。

接受与研究

近两年来,有两项重要的发布,使3D晶体管结构成为行业焦点并载入MOSFET晶体管技术史。

第一项出现在2011年5月4日,Intel公司宣布在其22nm半导体产品的设计与制造中采用了三栅极晶体管技术,在此之前,利用Hisamoto等在FinFET上的开发与优化成果所做的研发已持续了十来年。它表明三栅极晶体管结构在半导体生产中的实用性和成本效益都得到了确证,同时也表明了Intel在半导体技术方面继续处于领先地位。

第二项是ITRS技术路线图的发布,很多其他半导体制造公司也对此有贡献,它们认定3D晶体管技术是20nm或22nm的更小设计结点上所有递增半导体进展的主要推动力。

三栅极设计的主要优点

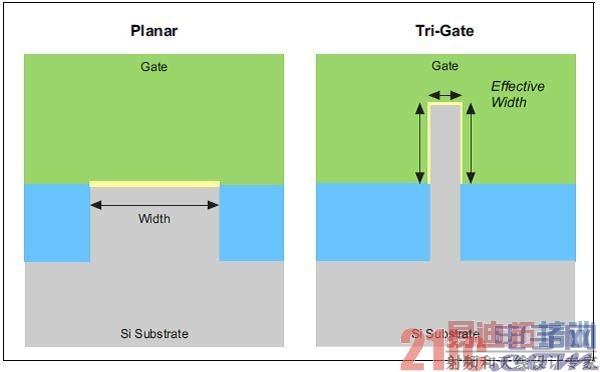

三栅极晶体管的3D几何形状与结构提供了一系列优于平面晶体管结构的重要改进,所有这些均与围绕源漏“沟道”的MOSFET“栅极”的“环绕”效应有关。这些优点表现在更高的性能、降低的动态功耗和泄漏功耗以及晶体管设计密度,还有减少了晶体管对带电粒子单事件翻转(SEU)的敏感度,见图1。

图1:平面与三栅极晶体管结构的有效沟道宽度

三栅极晶体管几何结构较传统平面结构的主要优点体现在导电沟道的有效宽度上。一支晶体管的电流驱动能力和性能与其有效沟道宽度成正比。相较平面晶体管来说,3D晶体管结构的有效沟道宽度得到了显著的提高,因为它能在第三维度上扩展宽度,而不会给设计面积带来任何影响,见图1。这就为晶体管的设计者提供了更好的设计灵活性和更高的性能,而不必像平面晶体管中那样,增加沟道宽度就会对2D面积带来不利影响。

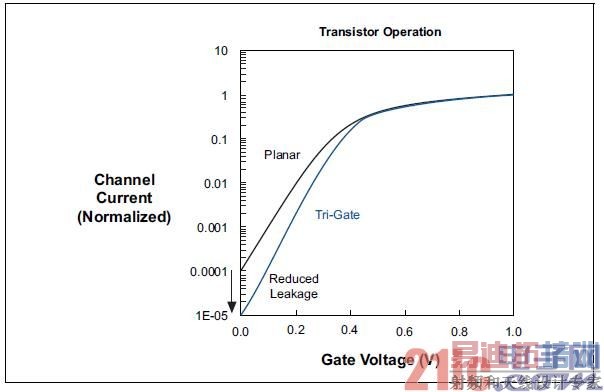

功耗方面的优点来自于三个鳍侧的栅极电场对沟道的改进控制。与平面晶体管相比,这减少了“关断”状态下从源极到漏极的亚阈值漏电流。另外,三栅极晶体管的电源电压可以大幅减小,而且由于与平面晶体管相比,增加了有效宽度,因此能保持优异的速度。低电源电压与降低的漏电流相结合,获得了显著的节能效果。

Intel公司在其Intel开发者论坛(2011、2012)中解释说,这种功耗优点源于三栅极晶体管的一种较陡峭的晶体管电压曲线,见图2。晶体管设计可以充分利用这种较陡峭曲线,显著减小漏电流(相对同等性能的平面晶体管),或大大提高性能(晶体管工作速度),或同时获得两种好处。

图2:三栅极晶体管结构提供了更陡峭的电压曲线

每一代新的硅制造技术通常都会缩减几何尺寸,或减小总体的栅极与晶体管结构,从而获得更高密度和更高能力的硅片。3D三栅极结构本身也适应于更高密度的晶体管设计,因为它在第三维度上扩展了晶体管的宽度特性。这样,设计者就能够根据性能、功耗以及晶体管密度封装等目标,在晶体管“鳍片”的尺寸与宽度两方面做出权衡取舍。以Altera转向14nm三栅极设计为例,Altera将获得两方面的好处,一方面是晶体管几何尺寸缩小到14nm,另外,通过3D三栅极晶体管设计可得到更高的密度。

SEU优势来自于三栅极结构中连接鳍片与衬底的小截面积。这样,可能收集到离子化粒子所产生电荷的面积就小于平面晶体管结构。根据Intel对其产品采用三栅极晶体管的22nm实现的早期测试,这降低了带电粒子造成晶体管电路中位翻转的概率。

量产中的三栅极器件

尽管对三栅极晶体管优点的研究和了解已经持续了一段时间,但其接受与实现的最终动力将是技术与可制造性,以及性价比。

极小几何尺寸下(40nm、28nm、22nm或20nm乃至更低)的先进半导体制造需要相当的研发开支,从而将该技术限制在少数有数十亿美元资本开支能力的公司。于是,只有少数公司能够从已知的3D晶体管技术优势中获利。Intel公司是唯一一家已在22nm下完成这种设计与制造技术转换的企业,可以在量产水平上,提供有关三栅极晶体管的全部成熟及可制造性的数据。到2013年第一季度时,该数据已经包括了1亿单位的基于三栅极晶体管的产品。

为了获得该技术在制造与设计方面的成熟度,针对3D栅极结构的多个问题与特性已经被认可并予以解决。这些包括对传统平面设计中未予模型化的新的寄生电容值的建模,布局的依赖效应,以及用现有光刻设备来生成近距离翘片的双模技术。

电子设计自动化(EDA)社区也是半导体设计者了解FinFET与三栅极设计技术的重要场合。2013年,Cadence与Synopsys等很多公司都做了大量的宣传及用户教育工作,中心内容是三栅极的影响,以及未来半导体产品设计中的灵活性。

对FPGA及其他半导体器件性能的影响

对FPGA电子产品的设计者而言,三栅极技术的主要优势是:摩尔定律持续适用于晶体管密度、性能、功耗以及单位晶体管成本的稳步改进。它支撑着消费电子行业、计算平台开发、软件复杂性的提高、存储器与存储容量的增长、移动设备创意与发展,以及商务自动化与生产效率。

此外,该技术极大改善了对半导体静态与动态功耗的控制。对于FPGA用户,在当前的竞争性设计结点上,可编程逻辑推进到14nm技术甚至更低,就能具备较ASIC与ASSP设计方案更强大的竞争力,而在可编程性、性能、灵活性、开放计算语言(OpenCL)软件设计输入,以及DSP、收发器、硬化处理器和可配置I/O的集成方面,甚至有着更明显的优势。

Intel公司根据三栅极技术在微处理器产品中量产的情况,向自己的普通投资者社区说明了他们能获得的明确利益。该数据包括:从32nm平面转到22nm三栅极设计时,单管动态功耗减少了50%以上;与32nm平面设计相比,22nm三栅极的缺陷密度曲线得到了改善;而从32nm平面转到22nm三栅极设计时,SEU发生率降低至1/4至1/10。

Intel在晶体管技术方面的领先地位

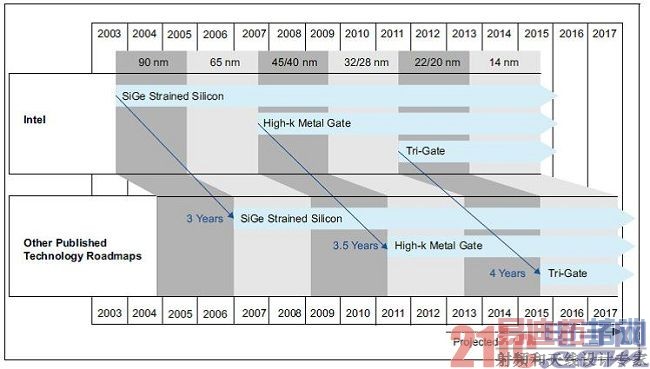

在包括Intel的开发者论坛以及投资者的研讨会在内的多个公开论坛上,Intel都以一系列与摩尔定律同步的进展表明了自己已有的技术领导地位。如图3所示,Intel在应变硅与高K金属栅极技术的量产实现方面,拥有多年制造领先地位。对于3D三栅极晶体管技术,Intel于2011年将22nm的三栅极技术投入生产,预计领先时间多达四年。

图3:Intel在晶体管技术方面的领先地位

Intel公司CEO Paul Otellini在2013年4月16日的业绩发布会上表示:“在(2013年)一季度,我们交付了第1亿片采用我们革命性3D晶体管技术的22nm(三栅极)处理器,而业内其他人还在努力交付自己的第一片产品。”

Intel公司14nm技术的推出将获得另一个领先优势,这可以回溯到它对工艺与微架构的极著名的“Tick-Tock(工艺年-构架年)”战略。产品推出的“Tick”周期要依赖于CPU产品中微架构变动的实现,其后是半导体工艺制造几何尺寸缩减“Tock”周期。Intel在从22nm转到14nm时坚定地致力于全工艺尺度微缩;而其他制造商开发的半导体技术工艺则尚不明确,他们的工艺路线图不知是否包括了工艺微缩的优势。

从Altera的FPGA获得三栅极技术的好处

只有Altera 14nm工艺高密度高性能FPGA的用户,才可能充分利用Intel三栅极技术的显著优势。这是本文所述两家公司专有制造合作关系的结果。

三栅极硅技术的巨大优势将使Altera能够提供难以想象的高性能FPGA与SoC产品。这包括与其他高端FPGA相比,其核心性能实现了历史性的翻番,将FPGA带入GHz的性能水平。通过工艺、架构与软件的共同进步,整体的静态与动态功耗值都将减少70%。

虽然Intel公司尚未公开14nm制造工艺的详情以及日程表,但Altera用户现在就可以着手将三栅极技术的高性能与低功耗优势用于FPGA设计中。可以开始设计的是Arria 10的20nm FPGA器件组合。然后,用户可以使用管脚对管脚(pin-for-pin)式设计迁移路径,从Arria 10 FPGA与SoC产品迁移到Stratix 10 FPGA与SoC产品(一旦可用)。

这样,无论您是FPGA用户还是系统架构师,都可以着手设计出能够同时兼容Arria 10和Stratix 10系列的产品,而尽量减少变更、修改和再工程化的工作量。于是,您就能用20nm工艺技术和降功耗技术,将最高性能和最低功耗的FPGA推向市场;然后,再利用Intel公司14nm三栅极制造工艺,就可以将这些相同产品推进到以往不可想象的性能与功率效率。

总结

过去,最高性能FPGA产品的判定是一个经验性的参数性能评判过程。但从14nm三栅极技术开始,最高性能的FPGA一定是使用了具备明显优势的晶体管技术的产品。只有Intel公司的14nm三栅极工艺才能提供第二代经验证的生产技术。只有Intel公司的14nm工艺可同时提供三栅极技术的优势,以及全晶体管工艺微缩的好处。同时,Altera是获准采用Intel这种技术的唯一一家主要FPGA公司。您的系统设计采用了三栅极技术后,将确保能够充分利用到这种领先地位。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...