- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

UltraScale架构DDR4 SDRAM接口的秘密

Adrian Cosoroaba和Terry Magee在本月MemCon上给出了关于DDR4 SDRAM接口的详细展示,该演示应用于赛灵思UltraScale All Programmable FPGA上。接口设计将DDR SDRAM提升至2400Mbps甚至以上,同时降低接口功耗。为了达到这个目标,赛灵思的工程师们必须将DDR4接口问题放在首位。除了设计将DDR4兼容UltraScale I/O PHY,他们从头设计了DDR4 I/O PHY,然后扩展它的性能并支持其他I/O的需求。结果:基本的13位可编程字节通道,这首先是一个DDR4 PHY。

如果你来自SoC的世界,也许不太明白为什么赛灵思需要选择这样做。因为当有成千上万甚至百万个逻辑单元和触发器、几兆的块RAM和数千个DSP片时,由于物理封装的限制只有数百个I/O管脚,所以,I/O管脚是稀缺资源。所以,I/O管脚必须可编程且足够灵活,可覆盖任何可能的I/O使用范围,从DDR4-2400 SDRAM驱动库到使LED闪烁以及其他更多的事情。这就是赛灵思为何如此做的原因。对于UltraScale架构的FPGA来说,我们首先实现了I/O设计的难点——DDR4 PHY,然后再添加一些简单的。

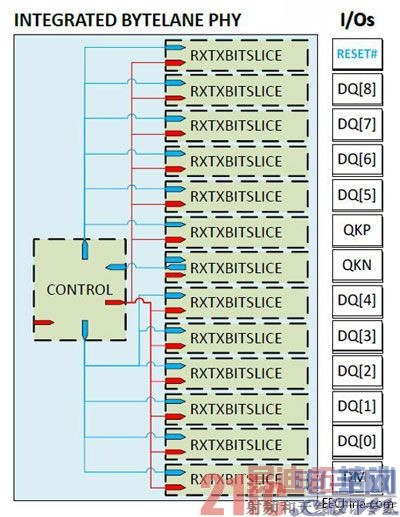

结果非常明显,I/O字节通道架构看来如此:

UltraScale FPGA I/O字节通道架构

逻辑上下一个问题也许是:“为什么13位 ”简单的答案是,两个这样的库涵盖26位,这是DDR4 命令和地址行要求的。数据行、频闪和预选要求每个字节各另外添加11位,这符合新的13位UltraScale I/O库。. QDR和RL3 DRAM要求12个I/O行(9个数据行和2个时钟),这也符合13位块结构。任何余下的关键都可编程另作他用。

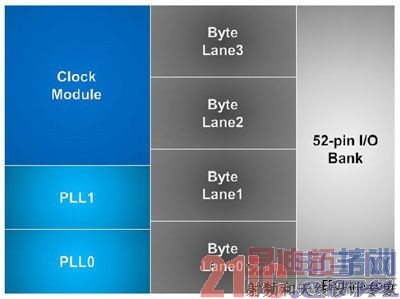

UltraScale FPGA的52管脚I/O库封装4个13位字节通道以及两个PLL和一个时钟模块,看似如此:

一个UltraScale 52管脚IO库

两个PLL允许你将个库分开,这样就能在你的设计里为两个完全不同的目标服务。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:一款突破性的布线工具

下一篇:基于FPGA的非线性调频信号脉冲压缩的实现