- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的异步USB数据传输系统设计

摘要:设计实现了以FPGA为主控制单元,采用EZ-USB FX2微处理器为接口芯片的快速数据传输系统。文章给出了FPGA和CY7C68013之间数据传输的软硬件设计方案,着重介绍了FPGA内部建构的FIFO原理及程序实现方法,并以FLASH存储模块为例,通过FX2与FLASH握手过程的设计,实现了数据存储器与计算机之间的数据高速传输。应用结果表明,此数据传输系统可靠有效,具有一定的通用性,可用于其他使用USB进行数据传输的系统中。

0 引言

现代电子技术的进步使得外设的种类日益繁多,接入数量急剧增加,传统的安装数据采集卡的方式,由于存在安装不便、扩展困难、传输质量不高等诸多缺点,渐渐满足不了数据采集过程中对复杂外设和数据传输速率的要求。此外,在需要移动数据采集的场合,普通笔记本电脑以及绝大部分便携式数据采集设备都不再提供PCI插槽。因此采用统一、便捷的数据传输接口来替代原有方式,其紧迫性日益凸显。通用串行总线(USB)作为一个接口规范把不同类型的接口统一起来,且其外接设备具有热插拔、易扩展、传输速度快等优点,已经成为各类笔记本和便携设备数据传输的主流接口。

本设计使用支持USB2.0协议的CY7C68013芯片,作为上位机与FPGA之间的传输接口,以FPGA为主控制单元,实现了数据的高速传输。文章给出了此数据传输系统的硬件设计方案,着重介绍了FPGA控制模块中内部集成FIFO的结构原理和关键程序模块的实现方式。本系统设计方案结构简单、传输速度快、具有一定的可扩展性。

1 系统硬件设计

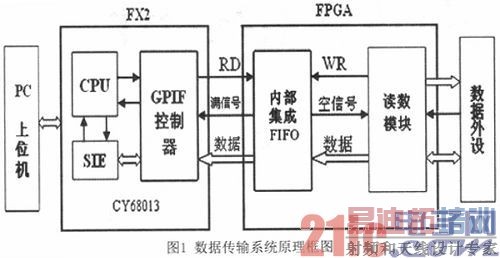

数据传输系统硬件原理框图如图1所示,主要由USB传输控制器EZ-USB FX2、FPGA主控制单元、外设模块构成。数据采集模块在中心控制单元的控制下对信号、数据等进行采集,并把数据最终转入数据外设中进行存储。上位机经传输控制模块(FX2)发送控制指令到主控制单元(FPGA)内部后,经过串并转换进行指令解码,解码后按照相应的指令要求从数据外设(FLASH)中进行数据读取。从而实现将外设存储系统中的数据快速上传到上位机中保存处理。

1.1 USB传输控制器

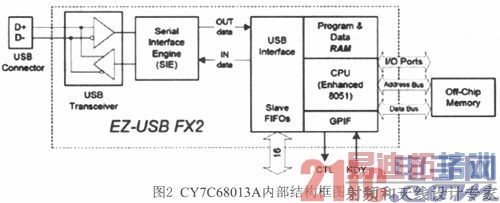

本系统USB传输接口芯片选择Cypress公司的CY7C68013,它是Cypress公司推出的EZ-USB FX2系列产品之一,集成USB2.0的微处理器,具有增强型8051内核性能,智能串行引擎(SIE),通用可编程接口(GPIF),8.5KB的RAM和FIFO存储器,支持12Mb/s的全速速率和1480 Mb/s的高速传输速率,最大限度地满足了USB 2.0的总线带宽。其内部结

构如图2所示。

CY7C68013由于其内部集成有独立于微处理器的USB核,其可被配置成GPIF(可编程接口)和SlaveFIFO(主从)等多种接口模式,使数据传输通过执行USB本身的协议来完成。在此过程中CPU可不参与数据传输,从而使数据的传输速率大大提高,同时也简化了固件代码的编写。本设计采用FX2的GPIF数据传输方式,时序简单、编程灵活,可以很容易地从RAM中读取数据。

1.2 FPGA主控制单元

本设计采用Altera公司的EP1K30QC208作为主控芯片,实现对数据传输过程的控制。它包括1728个逻辑单元,成本较低,适用于小系统编程。在此硬件系统中FPGA的作用主要有二个:一是实现对所传输数据的控制。上位机经USB传输控制模块(FX2)发送控制指令到FPGA主控制单元后,经过其内部串并转换,实现指令解码。解码后按照要求从数据外设(FLASH)中进行数据读取,并根据FIFO状态进行数据传输控制;二是内部建构一个FIFO存储器。由于本设计是对FLASH存储器进行读数操作,其数据传输是以页为单位,读数时页与页之间有一小段时间间隔,数据输出不是连续的。为实现FX2读取FLASH中的数据,需要在FPGA建构FIFO作为数据过渡,先将FLASH中的数据读到FIFO中,CY7C68013传输控制器再从FIFO中读取数据。

2 主控单元软件设计

根据本系统主控制单元的作用,FPGA要实现上文所述的主要功能,其关键在于FX2与FLASH的握手过程的设计,满足此过程的内部FIFO的建构和相关标志信号的产生。

2.1 FX2与FLASH的握手过程

FPGA主控单元先将数据存储到内部的FIFO中,然后CY7C68013再从FIFO中读取数据。由于读取和写入的速度是不同的,可能读比写快,也可能写比读快。为防止传输时数据丢失,设计如下的握手过程:FPGA内部的“读数控制”模块不断进行判断,只要FIFO不满它就一直向FIFO中写入数据。对于外部FX2,只要判断FIFO不空它就从FIFO中读取数据。这样FIFO的读写就组成了一个闭环,保证了读数的完整准确。在数据传输握手方式确定以后可能出现两种情况:1)FIFO的写入速度大于读取速度,这样写地址慢慢就追上读地址,此时总的传输速度就取决于读取速度。2)FIFO的读取速度大于写入速度,这样读地址慢慢就追上写地址,此时总的传输速度就由写入速度决定。在FPGA中编写“标志位

产生”程序模块,产生满、空信号作为FX2与FLASH传输过程中的握手信号,是保证数据传输稳定可靠的关键。

2.2 内部建构的FIFO原理及关键程序的流程

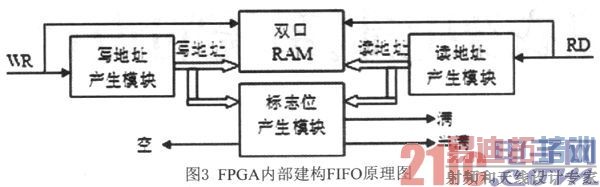

FIFO的本质是一种特殊的双口RAM,大部分FPGA内部就有双口RAM资源。FIFO结构的特点是先进先出,对外它是一种没有地址控制的特殊缓存。在程序编写过程中,内部FIFO要求只要接收RD、WR使能信号,就能进行读写工作。在此过程中,整个FIFO模块对外不显示地址,只需要给出表现内部状态的满、半满和空信号即可。FX2和FPGA内部的“读数控制”模块根据这些信号对FIFO进行数据传输控制。FPGA内部建构的FIFO原理图如图3所示。

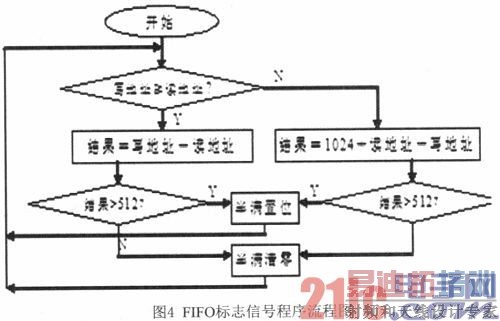

FIFO产生满、空状态标志信号由“标志位产生”程序模块产生,满、空状态信号均采用写地址和读地址相减(或读地址和写地址相减)的结果来判断双口RAM此时的状态。此外,还可以据此得到FIFO的半满状态信号,以此可容易地标示FIFO满空深度。FIFO满、空、半满标志信号的程序流程基本一致,只不过判断比较的差值存在不同。FIFO满时地址差值为1023,空时为1,半满是差值大于512。以半满信号产生为例,标志位产生程序流程如图4所示。

为了避免时序错误,还可以任意设定一定的满空深度。例如可以设定当地址差大于1000时即认为FIFO己满,不再向FIFO中写入数据,以避免错误的出现。

3 结语

随着便携式数据存储系统的普及,基于USB的数据传输系统受到了普遍关注。本文设计的基于EZ-USB FX2微处理器的数据传输系统,实现了上位机通过USB端口对FLASH存储器的快速读取操作,并成功地应用在某一车载数据盒工程项目中。测试结果表明,系统传输过程稳定,速度较高,与上位机接口方式严格遵守USB 2.0协议,具有很强的通用性,适合即插即用的工作场合。本系统基于FPGA的主控单元配置方案便于软件系统的升级与调试,如果搭配合适的传感器和相应的信号调理电路,就可以实现对多种信号的采集处理,再配以合适的存储模块完全可以构成完备的数据采集存储系统。本设计对于一般的数据传输系统的设计及传统接口改造具有一定的借鉴意义。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:可编程技术释放了闪存在企业级应用的潜能

下一篇:FPGA与CPLD的辨别和分类