- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于OpenCL标准的FPGA设计

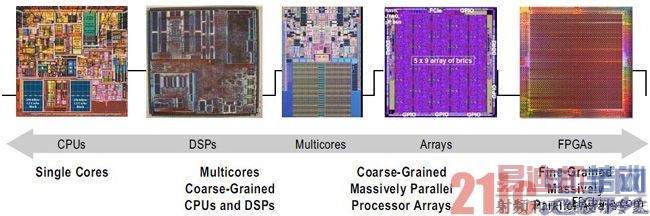

在可编程技术发展的最初阶段,可编程能力出现了两个极端。一个极端的代表是单核CPU和DSP单元。这些器件使用含有一系列可执行指令的软件来进行编程。对于编程人员,在概念上以连续的方式来开发这些指令,而高级处理器能够对指令重新排序,在运行时从这些连续程序中提取出指令级并行处理操作。作为对比,可编程技术另一极端的代表是FPGA。通过开发可配置硬件电路对这些器件编程,完全并行执行。使用FPGA的设计人员实际上是大规模开发粒度非常精细的并行应用。多年以来,这两个极端同时存在,每一类型的可编程功能适用于不同的应用领域。但是,最近的技术发展趋势表明,有更好的技术同时实现了可编程和并行处理操作。

软件可编程器件的第二种趋势是复杂硬件的出现,从顺序程序中提取出指令级并行处理操作。单核体系结构输入指令流,在器件中执行它们,这些器件会有很多并行功能单元。处理器硬件的很大一部分必须专门用于从顺序代码中动态提取出并行处理操作。此外,硬件还会尝试去补偿存储器延时。一般而言,编程人员开发程序时没有考虑处理器的底层存储器结构,好像只有大规模的统一快速存储器。相比较而言,处理器必须处理实际延时,以及与外部存储器的有限带宽链接。为保持功能单元能够传送数据,处理器必须从外部存储器中预先获取数据,放入片内高速缓存中,这样,数据更接近要进行计算的地方。使用这些技术,性能经过多年的提高后,这类体系结构的改动已经不大了。

图1.可编程和并行技术最近的发展趋势

在传统处理器体系结构上,这两种趋势的优势日益减小,我们开始寻找各种软件可编程器件,这些器件的发展非常快,如图1所示。重点是从运行时自动提取指令级并行处理操作,发展到在编码时明确的找到线程级并行处理操作。开始出现高度并行的多核器件,一般趋势是含有多个简单处理器,很多晶体管专门用于计算,而不是采用高速缓存,提取并行处理操作。这些器件一般包括含有2、4或者8个内核的多核CPU,以及含有数百个适用于数据并行计算的简单内核的GPU等。为能够在这些多核器件上实现高性能,编程人员必须以并行方式清晰的对实际应用进行编程。每一内核都必须分配一定的工作,这样,所有内核能够协同工作,执行某一计算。这也是FPGA设计人员在开发其高级系统体系结构时所做的工作。

考虑到多核新时代开发并行程序的需求,开发了OpenCL (开放计算语言),以便开发跨平台并行编程标准。OpenCL标准还能够自然的描述在FPGA中实现的并行算法,其抽象级要比VHDL或者Verilog等硬件描述语言(HDL)高得多。虽然有很多高级综合工具能够实现高等级的抽象功能,但是都存在同样的基本问题。这些工具会采用连续C程序,产生并行HDL实现。在开发HDL时,困难还不是很明显,但是,提取出线程级并行处理操作在FPGA中实现以提高性能时,困难却非常大。而FPGA的并行功能非常强大,与其他器件相比,在尽可能提取并行功能时出现任何失败的后果都非常严重。OpenCL标准能够解决很多这类问题,它支持编程人员明确的设定并控制并行处理操作。与纯C语言描述的连续程序相比,OpenCL标准能够更自然的匹配FPGA的高度并行特性。

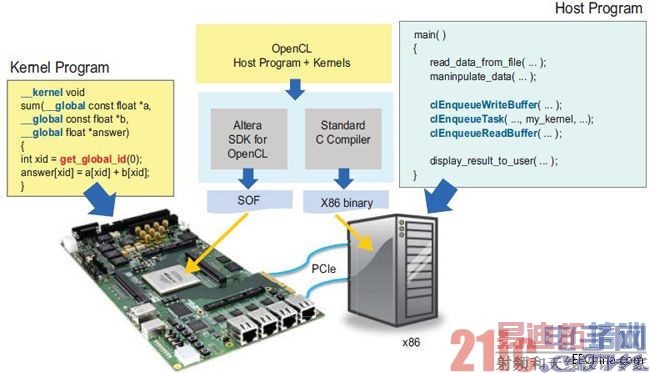

OpenCL应用程序含有两部分。OpenCL主程序是纯软件例程,以标准C/C++编写,可以运行在任何类型的微处理器上。例如,这类处理器可以是FPGA中的嵌入式软核处理器、硬核ARM处理器或者外置x86处理器。

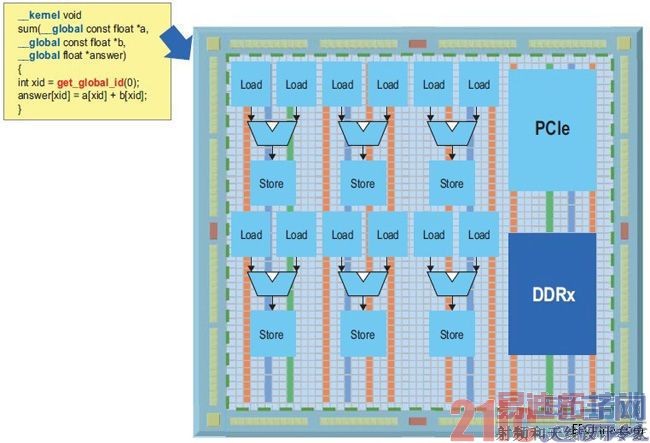

在这一主软件例程执行期间的某一点,某一功能有可能需要进行大量的计算,这就可以受益于并行器件的高度并行加速功能,例如CPU、GPU、FPGA等器件。要加速的功能被称为OpenCL内核。采用标准C编写这些内核;但是,采用结构对其进行注释,以设定并行处理操作和存储器等级。图2中的例子对两个数组a和b进行矢量加法,将结果写回输出数组应答中。矢量的每一元素都采用了并行线程,当采用像FPGA这类具有大量精细粒度并行单元的器件进行加速时,能够很快的计算出结果。主程序使用标准OpenCL API,支持将数据传送至FPGA,调用FPGA内核,传回得到的数据。

图2.在FPGA上实现的OpenCL例子

在FPGA中,可以把内核功能传送到专用深度流水线硬件电路中,它使用了流水线并行处理概念,在本质上就是多线程的。这些流水线的每一条都可以复制多次,与一条流水线相比,提供更强的并行处理功能。

在FPGA上实现OpenCL标准的优势

使用OpenCL描述来开发FPGA设计,与基于HDL设计的传统方法相比,具有很多优势。开发软件可编程器件的流程一般包括进行构思、在C等高级语言中对算法编程,然后使用自动编译器来建立指令流。面向OpenCL的Altera SDK提供了设计环境,很容易在FPGA上实现OpenCL应用。如图3所示。

图3.面向OpenCL的Altera SDK简介

可以把这一方法与传统的FPGA设计方法相比较,在传统方法中,设计人员的主要工作是对硬件按照每个周期进行描述,用于实现其算法。传统流程涉及到建立数据通路,通过状态机来控制这些数据通路,使用系统级工具连接至底层IP内核,由于必须要满足外部接口带来的约束,因此,需要处理时序收敛问题。面向OpenCL的Altera SDK帮助设计人员自动完成所有这些步骤,使他们能够集中精力定义算法,而不是重点关注乏味的硬件设计。以这种方式进行设计,设计人员很容易移植到新FPGA,性能更好,功能更强,这是因为OpenCL编译器将相同的高级描述转换为流水线,从而发挥了FPGA新器件的优势。

在FPGA上使用OpenCL标准,与目前的硬件体系结构(CPU、GPU,等)相比,能够大幅度提高性能,同时降低了功耗。此外,与使用Verilog或者VHDL等底层硬件描述语言(HDL)的传统FPGA开发方法相比,使用OpenCL标准、基于FPGA的混合系统(CPU + FPGA)具有明显的产品及时面市优势。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:高效非反向降压-升压转换器设计标准

下一篇:详解远距离测温器数控系统设计