- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的跳频系统快速同步算法设计与实现

摘要:同步技术是跳频系统的核心。本文针对FPGA的跳频系统,设计了一种基于独立信道法,同步字头法和精准时钟相结合的快速同步方法,同时设计了基于双图案的改进型独立信道法,同步算法协议,协议帧格式等。该设计使用VHDL硬件语言实现,采用Altera公司的EP3C16 E144C8作为核心芯片,并在此硬件平台上进行了功能验证。实际测试表明,该快速同步算法建立时间短、同步稳定可靠。

关键词:跳频;快速同步;FPGA;独立信道法;同步头法

跳频通信技术具有抗干扰、抗截获和高频谱利用率,应用广泛。同步是跳频系统的关键技术,收发双方只有在相同跳频图案相同跳变规律的同步状态下,才可稳定建立通信。传统同步方法主要有自同步法、独立信道法、同步头法、精准时钟法。自同步法通过频率搜索同步,难度大建立时间长;而独立信道法通过固定信道同步,抗截获能力弱;同步头法的同步头一旦受干扰,整个系统将无法工作;精准时钟法对时钟依赖太大,时钟不精准将增大失步的可能。文中设计了一种基于独立信道法,同步字头法和精准时钟相结合的快速同步算法,以克服上述单一同步方法使用的缺点。该同步方法能快速建立同步,且建立时间短,同步稳定可靠。

1 系统整体结构

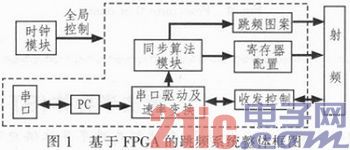

该跳频系统基于FPGA平台,由QuartusII软件展开设计。系统整体设计如图1所示。

上位机:产生数据流,时钟模块:控制系统各模块时钟,串口模块:实现串口驱动,上位机和FPGA硬件平台电平匹配,数率转换,收发控制:在同步算法控制下执行帧同步检测,根据算法协议与射频模块进行帧转换。跳频图案:在同步算法信令控制下生成不同的跳频序列,控制NCO频率合成器合成相应的载波频率。同步算法:帧同步检测,载波同步,传输协议控制。同步算法通过建立同步,保持同步,同步校

验,失步重建等,控制整个跳频系统,实现跳频电台之间的同步传输。

2 同步算法设计

独立信道法、同步头法和精准时钟法相结合构成的系统同步算法,可有效克服单一同步法的抗干扰性弱,建立时间长,不稳定等缺点。该快速同步算法的同步过程如下:

初始同步:在独立信道法下固定分配一个专门的信道传递同步信息,用于双方建立初始同步,一旦系统失去同步,则回到初始状态重新建立同步。由于专门信道,可再次快速地建立初始同步,克服了单一自同步头法的同步搜索复杂度高,同步建立时间长的缺点。

同步保持:初始同步建立后,发端发送同步协议帧(包括同步所需全部信息),收端根据该帧信息,进行同步校验,控制跳频图案在何时进入下一跳,以保持同步。

数据通信:跳频通信过程中,收发系统由精准的参考时钟控制各个模块,由协议帧控制跳频图案的跳变,以同步通信,有效减弱系统对全局时钟的依赖性且同步稳定。

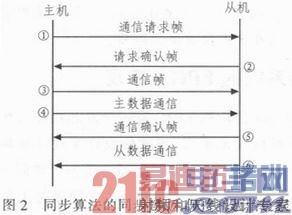

用上述的同步方法实现系统同步建立、保持,及数据通信的过程如图2所示。

图2中①②过程采用独立信道法,在专门信道建立同步实现了初始同步建立过程;③⑤过程采用同步头法,发送同步的协议帧,以保持同步;④⑥过程采用精准时钟法,在相同跳变规律下的相同频率实现数据的跳频通信。

2.1 同步帧头设计

系统利用同步帧头进行同步校验,由发端在不同状态发送4种协议帧,收端依据协议帧信息保持和发端相同的进程进入相应状态保持同步。该算法中设计的协议帧分别是;通信请求帧、请求确认帧、通信帧、通信确认帧,帧结构设计如图3所示。

帧头由国际标准定义的巴克码构成,具备漏同步和假同步概率小的特点。前导序列和帧尾间隔保护一帧数据。其中通信请求帧和请求确认帧,用于建立初始同步,通信帧和通信确认帧在通信中,传送协议帧进行同步校验保证同步的稳定性。

2.2 基于双图案的改进型独立信道法

传统的独立信道法在专门信道传送同步信息,快速建立同步,通信失步后也跳到初始的固定信道以重建同步,降低了系统的抗干扰能力。该算法结合精准时钟和双图案跳频思想设计的改进型独立信道法可有效克服传统独立信道法在失步重建信道时的低抗干扰性。

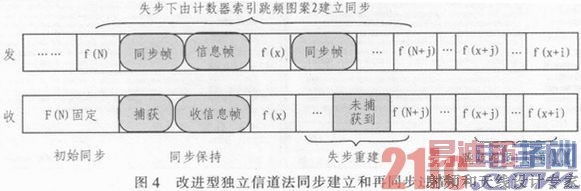

改进型独立信道法采用双图案的设计思想进行初始同步的建立,该设计中的双图案和自同步头法中的双图案有别。开机时在固定信道建立初始同步,跳频中由跳频图案1传输每帧数据,且每次跳频作为计数因子触发counter_suc。通信中一旦失去同步,系统回到初始状态,控制counter_suc产生中断,指向短周期跳频图案2,由图案2控制频率合成器生成频率,作为同步信道而非初始固定信道。系统中基于精准时钟,失步时刻收发端时间信息一致,则counter_suc的中断值一致,指向图案2的跳频序列也一致,则收发端频点一致,亦可在该信道下快速建立同步。改进型的同步算法如图4所示。

图4中系统开机时系统在信道f(N)建立初始同步,系统失步之后,收发双方由counter_suc指向跳频图案2的信道f(N+j),在该信道下再次重建同步。该系统中图案2用于初始同步的建立,周期短搜索时间短;图案1用于通信中传递信息,周期长搜索周期长。

3 快速同步算法的FPGA设计

上述快速同步算法在FPGA平台,采用Altera公司的Quartus2作为工具,用VHDL硬件描述语言进行逻辑功能设计。

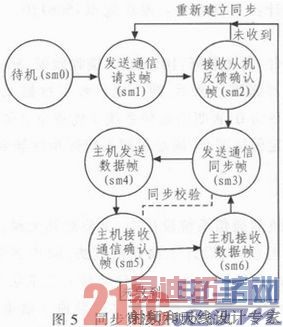

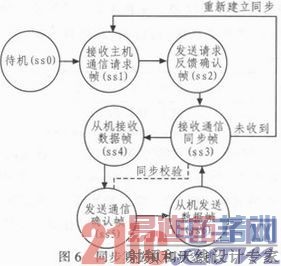

同步算法的状态机是同步实现的核心。跳频电台的主机和从机状态机如图5和图6所示。

图中所示,系统上电时主机和从机处于初始状态sm0,ss0,依照状态机流程依次执行状态转移。系统的第一次握手由主机的sm1状态发送通信请求帧实现,第二次握手则由从机的ss2状态反馈主机通信请求确认帧实现,两次握手在改进型独立信道法下快速实现系统初始同步。初始同步之后,主机sm3状态发送通信同步帧实现系统第三次握手,从机ss5状态发送通信确认帧实现系统第四次握手,两次握手保持通信中的同步状态,执行图中虚线所示的同步校验功能。

数据通信过程由主机sm4,sm6,从机ss4,ss6状态同步进行数据帧的收发。系统在同步保持状态下由图中所示环形执行状态转移循环进行数据通信,一旦系统中接收协议帧状态没接收到协议帧则系统失去同步,系统回到初始状态重新建立同步。

4 同步性能

同步时间是指建立初始同步的时间,在该算法中主要由系统跳速Rb,跳频间隔周期N和第一次第二次握手协议帧交换周期M决定。同步时钟为Tsyn,则同步建立时间Ts=M×Tsyn=(M/N)xRh。本系统跳速为900跳/s时,间隔N=386个周期,协议帧周期M=665,Ts≤0.01 s,一般系统要求同步时间Ts≤0.6s,故该算法可快速建立同步。

5 跳频系统的FPGA实现

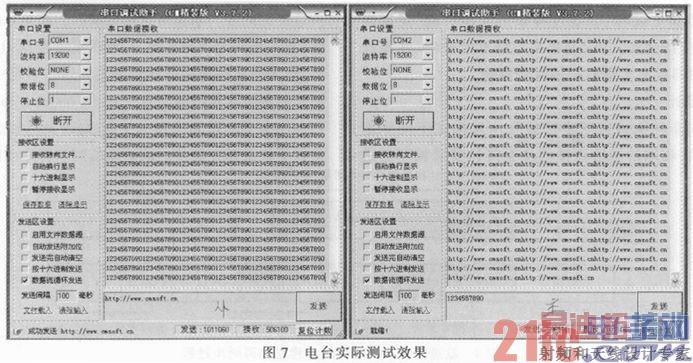

采用Altera公司的EP3C系列开发芯片作为快速同步算法的FPGA硬件实现平台,将软件设计实现的跳频系统下载到开发芯片中进行性能测试。如图7是基于该同步算法的跳频系统测试中,两个电台主机和从机之间通过上位机的串口调试工具传输数据的统计结果,其中com1是从机通过串口连接的上位机软件,com2是主机对应的上位机软件。

测试统计:主机电台:发送数据:506110,接收数据:1011060。

从机电台:发送数据:1011060,接收数据:506110。

由串口界面统计所示,两个电台收发数据无误,传输稳定。即误码率为0,表明该跳频系统工作稳定性能良好,该同步算法可稳定保持同步,满足跳频系统同步性能要求。

6 结论

文中在跳频通信系统设计中,主要对其关键技术同步算法展开研究与设计,设计了独立信道法,同步字头法和精准时钟相结合的快速同步算法。并针对独立信道法的抗截获能力弱,设计了基于双图案跳频的改进型独立信道法,即短周期图案用于同步建立,长周期图案用于跳频通信的实现过程,并分析了同步算法过程中的实现步骤,算法协议,设计过程等。由性能分析可知本文设计的同步算法可快速地建立同步,由FPGA硬件平台的实际测试可知该算法可快速地建立通信,且通信过程稳定,误码率低,具有工程实践意义。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...