- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

GPS C/A码发生器的仿真研究与FPGA设计

摘要:全球定位系统(Global Positioning System,GPS)能够向全球范围内的用户提供全天候的高精度导航、定位和授时服务,在军用和民用领域得到了广泛的应用。以GPS系统的测距码粗码C/A码为研究对象,在深入研究C/A码信号生成原理的基础上,利用Matlab中的Simulink对C/A码信号的生成进行了建模、仿真和分析,并利用FPGA设计并实现了C/A码发生器,详细说明了C/A码生成的设计原理,对其中的关键模块进行了设计和分析,给出了具体实现方案,同时阐述整个应用程序的流程,设计采用抽头选择控制端设置产生不同GPS卫星号的C/A码,最终仿真进一步验证了其结果的正确性,它可以产生任意GPS卫星号的C/A码,设计中采用VHDL语言实现的C/A码程序,可应用于基于FPGA的GPS接收机设计中,对研究我国的北斗导航系统接收机有一定的借鉴意义。

全球卫星定位系统(GPS)可在全球范围内,全天候为用户连续地提供高精度的位置、速度和时间信息。目前,GPS已被应用于军事、航海、航空、测量、交通、勘测等几乎一切与位置、速度、时间有关的人类活动中。自从GPS系统建立以来,世界上对于GPS及其应用技术的研究越来越普及。而关于与用户联系最为紧密的GPS接收机的研究是其中的研究热点。在GPS接收机的设计和研究中,为了捕获和跟踪GPS信号,首先就要对C/A码信号进行码剥离,为此,需要在本地复现与接收机接收的同相位的C/A码信号。因此,关于GPS信号C/A码生成的仿真研究就具有一定的意义。GPS卫星信号包括载波信号、测距码和数据码。其中的测距码粗码即C/A码(Coarse Acquisition Code)除了作为粗测码外,还由于其具有码长短,易于捕获的特点而作为GPS卫星信号的捕获码,因此C/A码是GPS信号捕获以及接收机实现的基础。文献利用Matl ab对C/A码进行了仿真研究,文献对C/A码生成进行了硬件仿真。

文中针对GPS全球卫星导航系统ICD接口文件中C/A码的编码方式,在Matlab仿真的基础上。设计出一种基于FPGA的C/A码发生器,通过VHDL语言编程实现了测距码的仿真,其结果表明设计的正确性。

1 基本原理

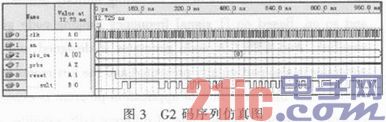

GPS卫星导航定位系统是一种无线电导航定位(Radio Navigational Satellite Service,RNSS)系统,利用高空中的GPS卫星,向地面发射L波段的载频无线电测距信号,由地面上用户接收机实时地连续接收,并计算出接收机天线所在的位置。GPS卫星发射L1和L2两种波段的载波,系统采用码分多址(CDMA)技术来区分各颗卫星,每颗卫星都有自己特定的伪随机噪声码(PRN码)结构。C/A码时钟速率为1.023 MHz,码长为1 023 chip,周期为1 ms。用于快速捕获导航信号和实时粗略定位。GPS系统的L1信号调制有两种伪码,粗捕获码(C/A码)和精密码(P码)。L1频率上的GPS信号表达式如下:

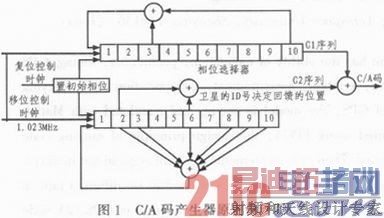

C/A是Gold码序列,由两个10位移位寄存器G1和G2产生长度为210-1=1 023位的最大长度伪码(PN码)。C/A码是由G1的直接输出和G2的延时输出异或的结果,是长度为1 023的±1序列。其发生器如图1所示。G2的时间延时取决于选取的两个点的位置,这两个点的选取和卫星的ID是一一对应的。

如图1所示C/A码发生器是由两个10级反馈移位寄存器组成的,上面的移位寄存器产生m序列G1,下面移位寄存器产生m序列G2。G1和G2码的特征多项式是:

G1(x)=1+x3+x10

G2(x)=1+x1+x2+x3+x6+x8+x9+x10 C/A码是G1码与G2码的模2和的结果,通过在G2寄存器不同位置反馈抽头,可产生不同的延迟偏置。选择不同的等价序列G2和G1相异或,可以得到不同结构的C/A码,C/A码可表示为:

G(t)=G1(t)·G2(t+iTc)

i是大于等于0的整数。G1和G2的周期为1 023,码速率均为1.023 MHz,因此,周期都是1 ms。采用不同的可以产生1023种不同结构的乘积码,再加上G1和G2本身,共有1 025种结构不同的C/A码。

2 C/A码发生器的实现方法

C/A码的产生需要G1和G2码序列,G1和G2的一个周期总数为1 024,而C/A码截断一位,因此,在第1 023个码元之后的下一个脉冲要进行复位操作。采用VHDL编写各个m码产生器,编写的依据是m码产生原理及其仿真。

2.1 G1码发生器设计

G1码序列是一个10级反馈移位寄存器所产生m序列,根据C/A码发生器整体需要,还需要在设计G1码发生器本身上再加上控制信号端。将编写好的VHDL语言程序在Quartus II环境中进行编译,并生成相应元件符号。用QuartusII模拟器对该模块进行时序仿真。

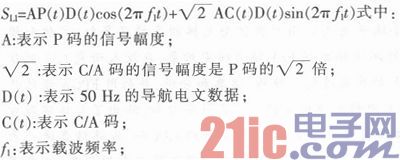

图2中,clk端为同步时钟脉冲:1.023 MHz,en端为使能端,高电平“1”有效;reset端为复位端,高电平“1”有效,在reset下降沿以后开始输出G1码序列,每个时钟上升沿输出一个码字,依次为:“1,1,1,1,1,1,1,1,1,1,0,0,0,1,1,1,0,0,0,……”

2.2 G2码发生器的设计

G2码发生器的设计方法与G1相同,只是多了一个平移选择器,平移选择器的不同组合可以产生多种结构不同的m码,所以,G2的设计要比G1多一个平移选择器的控制项。本设计通过选择不同的抽头得到不同的m序列码结构。用Quartus II对该模块进行时序仿真。

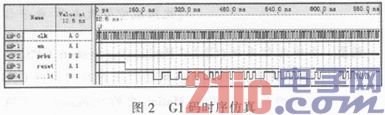

如图3所示,clk端为同步时钟脉冲1.023 MHz;en端为使能端,高电平“1”有效;reset端为复位端,高电平“1”有效;pio_ca为相位选择段。仿真以0号平移选择器为例的,即选择的抽头为该10级反馈寄存器的2和6。系统在reset同步下降沿以后开始输出G2码序列,每个时钟上升沿输出一个码字,依次为:

“0,0,1,1,0,1,1,1,1,1,0,0,1,0,1,1,0,1,0,……”

2.3 C/A码发生器的FPGA设计

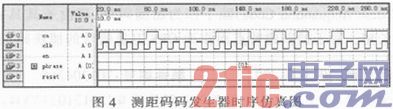

在Quartus II环境中,将生成的G1码和G2码的发生器生成元件符号,以Schematic File的设计方式将G1和G2码发生器组合起来,考虑到系统的稳定性,还设计了一个带时钟异或运算模块,用于接收全局时钟同步。本次仿真以第一颗卫星为例,相位输入为“0000”。在Quartus II环境下,将总体设计电路图进行编译,并进行时序仿真,平移选择器控制字仍设置为0,仿真图如图4所示。

图4中,在系统reset同步以后,开始输出C/A码序列,每个时钟上升沿输出一个比特,依次为:“1,1,0,0,1,0,0,0,0,0,1,1,1,0,0,1,0,1,0,0……”。其中,clk端为同步时钟脉冲:1.046 MHz,en端为使能端:高电平“1”有效,reset端为复位端:高电平“1”有效,pharse为相位选择输入,ca端:产生的周期为1 023 bit的C/A码序列。

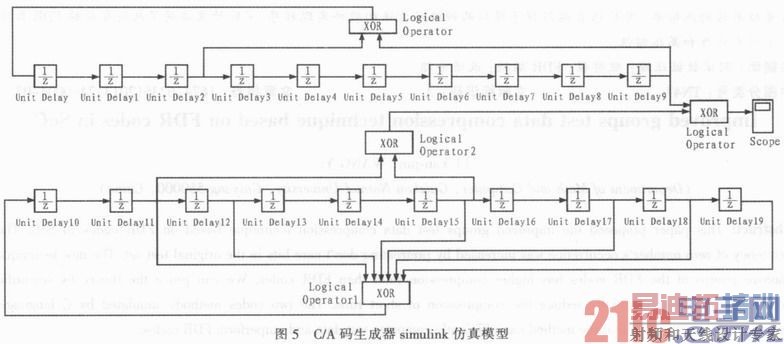

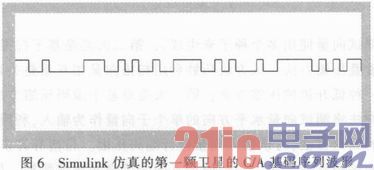

为了验证FPGA仿真的正确性,利用matlab simulink软件进行建模和仿真。利用延时单元构成两个10位的移位寄存器,并从移位寄存器输出端选择抽头连接到异或门电路,将其输出反馈,抽头和反馈的连接按照GPS卫星PRN编码规则进行选择,并把最终输出结果连接到示波器单元观察其仿真波形。建立的simulink仿真模型如图5所示,运行的结果如图6所示。从仿真的波形图上可以看出,输出的GPS第一颗卫星PRN码的C/A基码也依次为:“1,1,0,0,1,0,0,0,0,0,1,1,1,0,0,1,0,1,0,0……”,前10个C/A基码对应的8进制为1 440,与GPS系统第一颗卫星的C/A码完全相同。

3 结 论

结合GPS卫星导航系统f1频点C/A码发生器的设计,在研究GPS卫星导航系统ICD接口控制文件中C/A码生成器原理的基础上,给出了基于FPCA的码生成器的设计方案。利用VHDL语言实现了G1码和G2码的产生,并设计实现了C/A码,利用Matlab simulink建模仿真验证了FPGA设计结果的正确性,该设计可以产生GPS系统卫星号所对应的伪随机码,可以根据相位选择的不同实现不同卫星号的测距码的产生。采用模块化的设计方案,其研究结果对研究我国北斗导航接收机的设计具有一定的参考意义。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:FPGA自动加载系统设计实现

下一篇:基于FPGA的RS码译码器的设计