- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

10GHz介质振荡器的设计

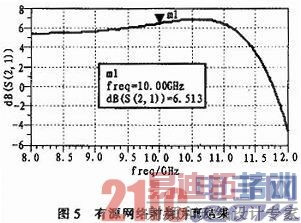

反馈网络的仿真完成后,下面进行有源网络的仿真。有源网络由场效应管和偏置电路组成,文中选用的晶体管是安捷伦公司的场效应晶体管GaAs FET 26884,该晶体管的工作频率为2~16 GHz,当工作点为漏源电压3 V,漏源电流10 mA时,增益在6 GHz约为12 dB,在12 GHz约为6 dB。本文采用正负双电源供电,以保证有源网络的S12模值尽可能小。偏置电路采用扇形微带接地,防止振荡信号功率从偏置电路泄露,并防止高频信号影响电源的稳定性。通过调节电路参数,使得有源网络增益S21尽可能大,仿真结果如图5所示,在所需频点10 GHz,增益达到6.5 dB。

下面将反馈网络的模型加入,对整个反馈回路进行开环仿真,首先调整输出匹配支节的位置和长度,使振荡频点的开环增益尽可能大,即满足环路增益大于1的条件;然后调整与反馈网络相连的微带线长度,使得反馈回路的传输系数S21相位为零,即满足环路相移为0的条件。

将环路闭合,插入ADS中的Osctest控件,由奈奎斯特判据可知,若仿真结果曲线随频率增大沿顺时针方向环绕1+j0点,则电路满足反馈式振荡器的振荡条件。在仿真过程中发现,电路起振的频率和满足奈奎斯特起振条件的频率比较接近,但前者往往略低于后者。这是因为奈奎斯特定律是对小信号条件下起振条件的判定,而电路起振后,随着振荡幅度的增大,晶体管S21模值会减小,相位会滞后。为了抵消这一变化,振荡频率会降低,用反馈回路减小的相位滞后抵消晶体管增加的相位滞后,这时反馈回路的传输系数会变小,最后达到平衡。反馈回路品质因数越高,相位变化就越陡峭,所引起的频率变化就越低。所以在仿真时,可以使初始的起振频率略高于所需要的输出频率,这样常常可以得到较大的输出功率。

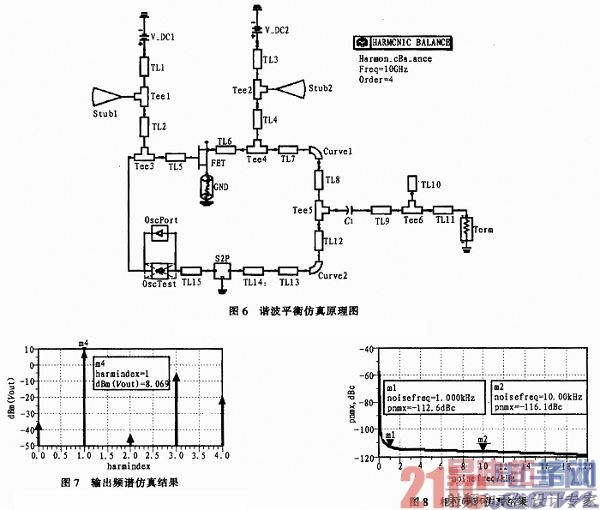

最后用振荡仿真控件Oscport代替Osctest控件,用谐波平衡法仿真输出频率分量和相位噪声情况。整个电路的原理图如图6所示,通过调节输出端匹配支节的位置和长度,使输出功率尽可能大。由于使用的开路匹配支节长度接近于振荡频率的八分之一波长,所以对二次谐波的抑制效果较好。仿真结果如图7和图8所示,可以看到,输出功率达到8 dBm,相位噪声为-112dBc/Hz@1kHz和-116dBc/Hz@10kHz。

为了增大输出功率,同时降低相位噪声,文中在以上传统电路结构的基础上进行了改进,采用两个晶体管串联的方式,如图9所示。这种方法提高了环路增益,从而提高了输出功率。由式(2)稳定振荡条件可知,此时反馈网络的传输系数可以适当降低而不影响起振。所以介质与微带线的耦合度可以减小,从而提高谐振器的有载品质因数,从而达到降低相噪的效果。

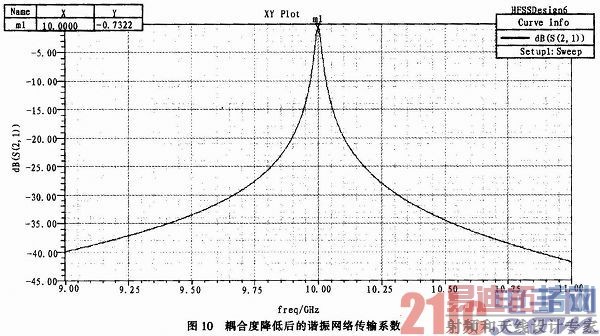

首先进行的仍然是反馈网络的仿真。为了便于进行调试,这里采用了增加垫块厚度的方式来降低介质与微带线的耦合度,垫块厚度由1 mm增大至1.6 mm。仿真结果如图10所示,可以看到,此时的谐振峰与图4相比更为陡峭,其3 dB带宽仅为33 MHz,说明该谐振网络的品质因数更高,从而可以降低输出相噪。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:采用FPGA设计智能能源系统

下一篇:FPGA自动加载系统设计实现