- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于UART的智能卡接口IP核设计

摘要:分析了UART核的结构和智能卡的传输协议,提出一种基于UART核的智能卡接口IP核的设计。该设计以成熟的UART核为基础,无需编写异步串口的时序与接口逻辑,仅在串口核中增加收发缓冲器和协议处理等模块,减少了工作量并缩短了开发周期。最后对所设计的IP核进行仿真和实际测试,结果表明该IP核设计正确,运行稳定,适合在多卡系统中应用。

关键词:UART;智能卡;IC卡;IP核;FPGA

引言

智能卡以其安全、灵活、通用等特点,被广泛应用在金融、交通以及其他安全终端设备上。目前许多读卡器都采用单片机来实现,而在一些特殊应用中,同时需要多张甚至10张以上的智能卡。由于卡片严格的时序要求,仅用单片机已经很难实现多卡的并行操作。FPGA具有硬件并行性和可编程等优点,很容易实现并行且对时序逻辑要求较高的操作,同时IP核的应用又给基于FPGA的开发带来了极大的便利,能减少大量开发时间。

本文首先介绍了智能卡的基本规范,着重分析字符传输协议(T=0)的操作流程。然后分析了Altera公司提供的UART IP核的结构,在此基础上给出了智能卡接口IP核的设计,并结合智能卡的操作流程,给出了传输协议的状态转换图以及实现方法。最后对IP核进行仿真分析和实际测试。

1 智能卡操作流程简介

智能卡是IC卡的一种,带有微处理器、存储单元以及芯片操作系统,不仅具有数据存储功能,同时还具有命令处理和数据安全保护等功能。智能卡采用异步半双工通信方式,其传输协议分为字符传输协议(T=0)和块传输协议(T=1),本文重点讨论字符传输协议(T=0),它是目前使用较广泛的通信协议。

智能卡主要有复位操作和指令操作。复位操作是将智能卡的复位引脚拉低若干周期,拉高后智能卡回复1个数据帧,提供了协议选择、时钟转换因子、波特率调整因子等参数,可供后续操作使用。该帧的长度在第2个字节中体现,因此先接收2个字节,再接收固定长度的数据,操作流程图如图1所示。

T=0时,指令操作主要有4种情况,如表1所列。

根据中国金融集成电路(IC)卡规范的规定,可在情况1后面补0,组成5字节指令。这时,4种情况都可归纳为:发送前5字节,等待接收1字节回复,由回复决定后续的操作。

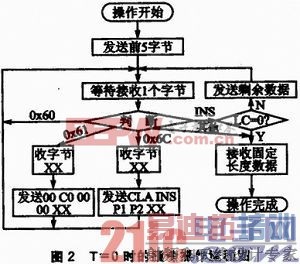

1字节的回复分为过程字节和状态字节两类,过程字节主要有INS(或INS补码)、60、61、6C;除过程字节以外的其他回复都属于状态字节。收到过程字节后须执行对应操作。接收到状态字节后须再等待接收1字节状态回复,将两个状态字节上传给控制器,终止本次操作。T=0

时的指令操作流程图如图2所示。

2 智能卡接口IP核的设计与实现

2.1 UART核分析

UART接口已经很成熟,已有许多现成的IP核可使用,利用UART进行智能卡接口IP核的设计可减少大量的开发时间。本文以Altera公司的Avalon总线接口的UART核(下文中所有UART核均指该核)为基础进行设计。[p]

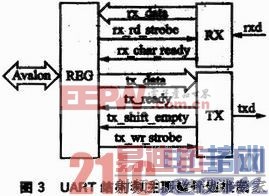

UART核主要有三大模块;发送模块(TX)、接收模块(RX)、寄存器模块(REG)。与CPU连接端为Avalon总线接口,与外部连接端为txd和rxd其主要结构和信号连接如图3所示。

REG模块通过tx_wr_strobe把数据tx_data写到TX模块中,TX模块按照设定的波特率往txd串行发送数据,同时把发送寄存器和发送移位寄存器的状态通过tx_ready和tx_shift_empty传回REG模块。

RX模块根据设定的波特率对rxd进行采样接收,当接收到1字节有效数据时置rx_char_ready有效,REG模块通过rx_rd_strobe读取接收的数据。

REG模块中包含控制寄存器、状态寄存器、波特率寄存器、数据寄存器,还包含Avalon总线接口逻辑以及各种寄存器的操作逻辑。

2.2 智能卡接口IP核结构设计,

智能卡的引脚有电源、地、复位、时钟、数据,其中只有复位和数据线与操作有关,因此在IP核中只需要复位线和数据线。

智能卡操作过程中,接收的数据和发送的指令都需要哲存在IP核内,因此要在UART核上增加发送和接收缓冲。除此之外,还需要增加协议处理模块用于操作过程中的判断和交互,增加收发切换模块实现异步半双工的切换,增加发送控制模块用于发送不同的数据。基于UART核的智能卡接口IP核结构如图4所示。

图4中,保留UART的RX和TX模块不变,在REG模块中增加了RX_BUF、TX_BUF、缓冲区长度寄存器,还增加了清缓冲区等功能。

在UART核的基础上增加协议处理模块,它是操作智能卡的核心。协议处理模块从RX模块直接截取数据并处理,根据流程进行各种操作。协议处理模块可以清除接收缓冲区中的过程数据、清除无效的发送指令,协议处理模块还控制收发的切换、控制发送指令、控制IC卡复位。

发送控制根据协议处理中的状态和命令,发送不同的指令到智能卡中。

2.3 协议处理的实现

在图4中,协议处理模块是实现CPU与智能卡交互的关键,本文采用状态转换的方法来实现。根据复位操作(图1)和指令操作(图2)的流程,可将智能卡的操作总结为7种状态:空闲状态、复位状态、接收1字节状态、接收定长数据状态、收到0x61状态、收到0x6c状态、其他状态。状态转换的主要条件是接收到特定的数据或接收到特定个数的数据,辅助条件是当前的状态和其他参数。状态转换图如图5所示。

空闲状态:刚上电或无操作时处于空闲状态,IP核等待CPU的命令。

复位状态:在空闲状态下收到复位命令后,复位智能卡并进入复位状态,等待接收数据。根据前2字节的回复设置接收数据长度,然后进入接收定长数据状态。

接收定长数据状态:根据前一状态的设置,等待接收固定个数的数据,当接收到设定个数的数据时,向CPU发送中断请求并跳转到空闲状态。

接收1字节状态:在空闲状态下当有效指令操作下发时,发送5字节命令头,进入接收1字节状态。在该状态下,收到0x60则不进行任何处理;收到INS时需判断LC,若LC不为0则发送剩余指令,若LC为0则设置接收长度进入到接收定长数据状态;接收到0x61或0x6c则分别进入到相应状态;接收到其他回复则设置固定接收长度为2,并进入接收定长数据状态。

收到0x61状态;接收1字节数据为0x61时进入该状态,在该状态下等待接收1字节数据并将该数据加到00 C0 00 00后一起发送,同时回到接收1字节状态。

收到0x6c状态:与收到0x61过程基本一样,将接收到的数据加到CLA INS P1 P2后面发送。

设计时,在非空闲状态下设定超时计数器,计数器溢出后无条件返回到空闲状态,同时清除接收和发送缓冲,表示本次操作失败。另外,所有的过程字节在状态处理时都被清除。[p]

2.4 智能卡接口IP核的实现

由于篇幅有限,本文只介绍状态转换和指令的实现方法。

用变量state表示当前的状态,有效值为0~5,其他值均为无效状态,在无效状态下将直接跳转到空闲状态。状态与state的对应关系如表2所列。

本文所使用的收发缓冲模块为SCFIFO,所有下发指令都先写入到发送FIFO,所有接收的数据都进入到接收FIFO。

表1中,4种指令长度都大于4,为实现复位操作,定义复位指令长度为1。实现时,为便于判断指令,在指令之前先将指令长度写到发送FIFO中。定义复位操作指令为01 01,其他操作指令为LEN(指令长度)+CMD(指令本身)。IP核先取出指令长度,当FIFO数据达到该长度时表示一个完整的指令已经下发,这时才可对智能卡进行操作。

3 仿真与实际测试

3.1 Modelsim仿真分析

为验证智能卡接口IP核的正确性,在Modelsim ASE6.6d上进行了仿真分析。仿真时,测试程序模拟CPU向IP核发送指令,同时模拟智能卡给IP核回复数据。

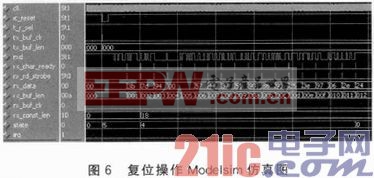

3.1.1 复位操作仿真

测试程序模块CPU向发送缓冲区写复位指令01 01,再模拟智能卡回复3b 7d 94 00 00 57 44 37 51 90 86 93 85 3e 97 06 2e 24(数据来源于实际PSAM卡)。图6是复位操作的Modelsim仿真图。

图6中,收到01 01指令后,IP核清空发送缓冲(tx_bur_clr=1),使IC卡复位(ic_reset=0),并跳转到复位状态(state=5)。由图中可以看出,IP核接收到2字节后计算出回复的总长度为18,状态变为接收定长数据状态(state=4)。当接收到的数据个数达到设定长度时(rx_buf_len =18),向CPU申请中断(irq=1),同时回到空闲状态(state=0)。

由仿真看出,复位操作时序正确。

3.1.2 取随机数操作仿真

测试程序模拟CPU向发送缓冲区写取随机数指令05 00 84 00 OO 08,再模拟智能卡回复84 11 22 33 44 5566 77 88 90 00(8字节随机数任意填写)。图7是取随机数操作的Modelsim仿真图。

图7中,取随机数指令下发后,IP核将数据线切换为发送(t_r_sel=0),发送指令并跳转到接收1字节状态(state=1)。当第1个字节等于INS(84)且LC=0时,清空接收缓冲区中的过程响应(rx_bur_elr=1),设置接收长度为10(rx_const_len=0a),跳转到接收定长数据状态(state= 4)。当接收到10个数据(rx_bur_len=00a)后跳转到空闲状态,同时向CPU申请中断(irq=1)。

由仿真看出,取随机数据操作时序正确。

3.2 实际测试

对本文设计的IP核进行了实际测试。采用Ahera公司的Nios Il CPU作为控制器,EP3C40F48417N为FPGA芯片,用10张PSAM卡作为测试的IC卡,CPU时钟为88.473 6 MHz,PSAM时钟为5.529 6 MHz。

测试操作过程为:

①返回根目录3f00;

②取PSAM卡序列号;

③进入文件目录df01;

④初始化加密认证;

⑤取认证码;

⑥取随机数。

6个操作为1轮,每秒对10张PSAM卡进行一轮测试。共测了201 803轮,耗时20 908 s,平均每秒9.65轮,所有操作全部成功。

由此验证,该IP核设计正确,运行稳定。

结语

本文分析了UART核与智能卡接口的结构,对T=0时的操作进行归纳,设计出基于UART的智能卡接口IP核。由于不需要重新设计UART的接收、发送以及相关寄存器等功能,使开发周期缩短了至少一半。将该IP核用在多卡系统中,能大量减轻CPU的负担,提高CPU的效率。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...