- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

TS流的CRC译码器设计

摘要:TS流是数字电视信号传输的主要方式,由于其采用的是广播方式且信道中存在着许多干扰,因此是不可靠传输。为了保证数据的正确性,一般需要进行信道编码。在发送端,TS流中通常采用的信道编码方式是CRC校验;在接收端进行译码。由于TS流数据量非常大,通常的软件译码方法不能满足要求。设计了一个基于FPGA的CRC译码器,速度快,并且具有很强的实时性。

关键词:FPGA;TS流;CRC校验;译码器

0 引言

随着我国数字电视发展的越来越快,集成度越来越高,数据传输的正确性也变得越来越重要。而TS流作为数字电视传输的主要方式,其信号的正确性将直接影响到电视画面的质量以及各种数字电视业务的发展,如互联网等。为了保证传输的可靠性,就要对数据加上CRC校验码,接收的时候对其进行译码。当前的译码大多是在微处理器上用软件来实现的,这样的软件译码方式速度比较慢,无法满足高速大容量的的数字电视信道的要求。本文设计了一个基于FPGA的CRC译码器,通过查找表法进行译码,能够达到很高的速度,具有很强的实时性。

1 TS流的结构

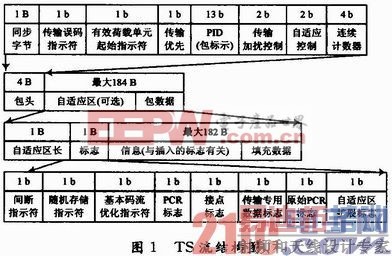

传送流(Transport Stream,TS流),它是根据ITU-T Rec.H.222.0 | ISO/IEC 13818-2和ISO/IEC13818-3协议而定义的一种数据流,其目的是为了在有可能发生严重错误的情况下进行一道或多道程序编码数据的传送和存储。传送流由一道或多道节目组成,每道节目由一个或多个原始流和一些其他流复合在一起,包括视频流、音频流、节目特殊信息流(PSI)和其他数据包。TS流是数字电视信号的主要传输形式,TS流由许多的TS包组成,每个TS包的长度为188 B,它由包头、自适应区、数据区三个部分组成,其中,每个TS包的有效信息占184 B,字节后面是4 B的CRC校验码。其结构如图1所示。

2 系统总体设计

本系统采用了Altera公司的低成本低功耗的CycloneⅣ系列的EP4CE6E22C8N芯片,此芯片具有6 272个LE,还有270 KB的内部存储器,非常适合用来做CRC校验。本系统采用了Verilog语言在FPGA上实现了UART的收发和CRC校验的功能。

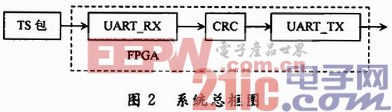

TS包的数据由串口发送至FPGA,在FPGA内进行CRC校验,当一个section的数据校验完之后,又由UART发送出去。总体框图如图2所示。

[p]

3 UART设计

UART的程序采用了自顶向下的分模块设计方法,其功能模块主要分为波特率产生模块、起始位检测模块、发送模块和接收模块四部分。各个模块分别编写好并且仿真通过之后,再在顶层对其进行例化,使各个模块能够连接起来。

3.1 波特率产生模块

设计采用的波特率为9 600 b/s,帧格式为1 b起始位,8 b数据位,无奇偶校验位,1 b停止位。波特率的产生主要是使用累加的方法,当累加到一定值的时候,就给clk_bps一个时钟的高电平,从而产生波特率。产生波特率的部分代码如下:

波特率产生的RTL视图如图3所示。

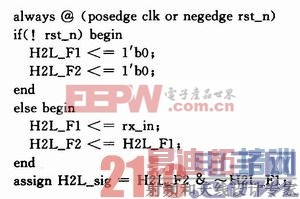

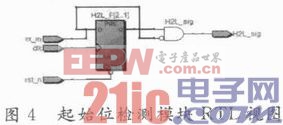

3.2 起始位检测模块

起始位是UART传输数据的开始,因此起始位检测的好坏至关重要,本设计采用了边沿检测技术来检测起始位,当起始位的那个下降沿到来的时候,H2L_sig端口就会产生一个时钟周期的高电平,为下面的接收做好准备,起始位检测的部分代码如下:

起始位的RTL视图如图4所示。

3.3 发送模块

发送模块主要功能就是将FIFO里8 b的数据按9 600 b/s波特率一位一位地发送出去,最后再加上停止位,其RTL视图如图5所示。

[p]

3.4 接收模块

接收模块的主要功能就是检测到起始位后再在每个数据的中央位置进行采样,接收完一帧数据后就放到接收FIFO里供CRC校验模块使用,其RTL视图如图6所示。

4 CRC校验

CRC校验有两种方法:一种是按位来计算的,一种是按字节来计算的。按位来计算的占用FPGA逻辑资源比较少,但是相对来说速度会比较慢,不能适应高速的TS流的要求。按字节来运算的速度快,但是占用FPGA的逻辑资源多。综合考虑后,这里使用按字节的算法。

本设计的CRC算法采用直驱动表法,由于一个字节只有8 b,与生成项进行异或后最多有256个结果,先将256个待查表的值生成MIF文件,放入由FPGA的IP核生成的ROM里,然后用查表法可以达到很快的运算速度,具有很强的实时性。其具体算法如下:

crc_reg=crctab[crc_reg[31:24]^buffer[7:0]8'hff]^{crc_reg[23:0],8'h0};

图7是用model sire对CRC进行仿真的结果使用的是PSI表里的一个section的数据,可以看到,校验到最后的时候,crc_reg的值变为了0,说明数据是正确的。

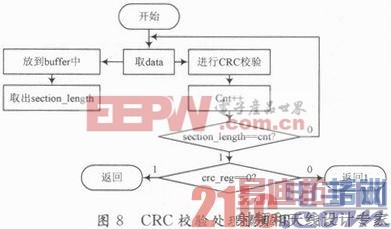

只要在接收FIFO里有数据,CRC模块就会将读取数据进行CRC校验。而每个PSI表里都有一个section_length是记录在这个表里面从该字节之后有多个字节是有效数据的。所以,要将这个数据提取出来再加上3就得到了整个表的长度。在CRC校验的时候,也要设置一个计数器,用于记录处理多少个数据,并与section_length比较。若这两个数相同,则判断CRC寄存器里的值;若为0,则说明这个数据段是正确的,通过串口发0x00给上位机;若CRC寄存器不为0,则说明这个数据断是错误的,FPGA发送0x01给上位机。

CRC校验处理的流程图如图8所示。

5 结论

本系统经过实际验证具有很高的准确性和实时性,并且在上位机和FPGA上都进行了校验,可以验证是否数据在串口传输的过程发生了错误,其FPGA部分可以当作一个独立的模块加入到其他系统中,具有很强的实时性。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...