- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于双核Nios II系统的数字预失真器设计

在现代无线通信系统中,功率放大器(PA)是整个发射机中最为关键的部件之一。然而,PA固有的非线性特性会对通信质量造成严重影响。数字预失真技术作为一种高效的功放线性化方法,近年来得到了广泛重视和研究[1-4].传统的数字预失真器一般采用FPGA+DSP的方案,结构较为复杂,成本较高。本文在FPGA芯片中构建了SoPC系统,设计了一个自适应数字预失真器(DPD),它具有集成度高、成本低等优点。同时,采用并行RLS算法提取DPD模型参数,降低了传统RLS预失真算法的复杂度。采用双核Nios II并行操作,提升了硬件处理速度,保证了预失真处理的实时性和敏捷性。

1 DPD多查找结构

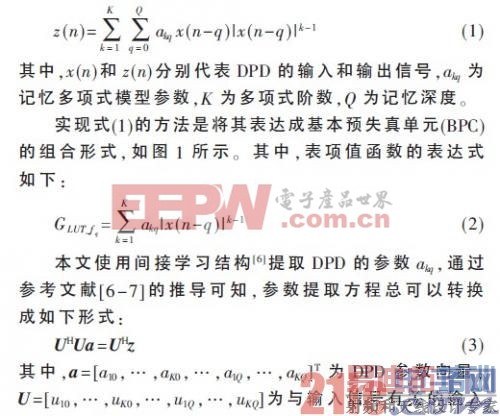

本文采用记忆多项式模型[5]作为DPD的行为模型,表示为:

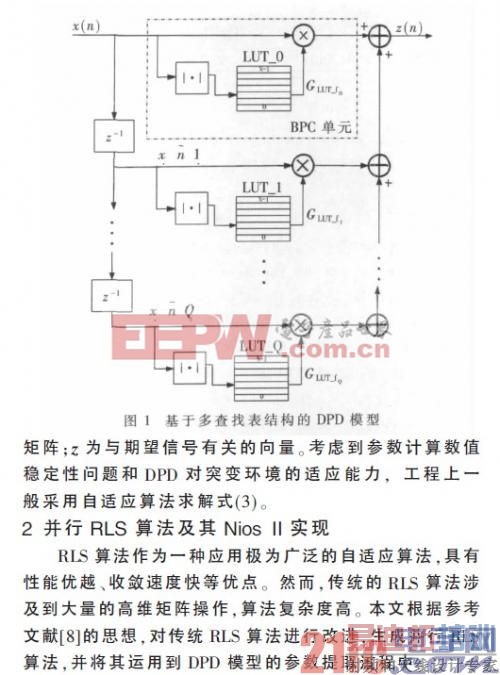

[p]

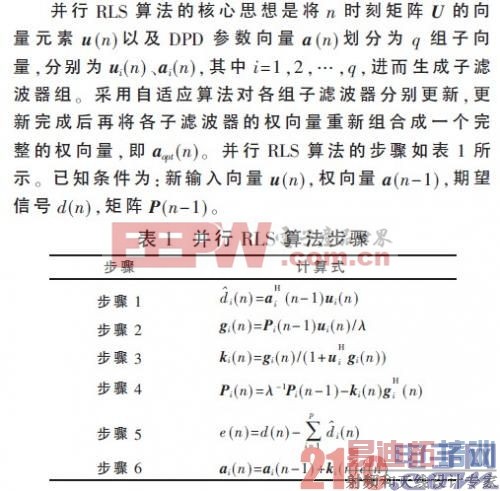

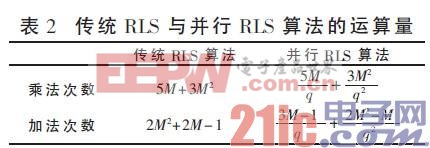

表2对比了传统RLS算法与并行RLS算法在加法和乘法运算量上的差异。相对于传统RLS算法,并行RLS算法的最大优势在于降低了矩阵维数,故减小了运算复杂度。

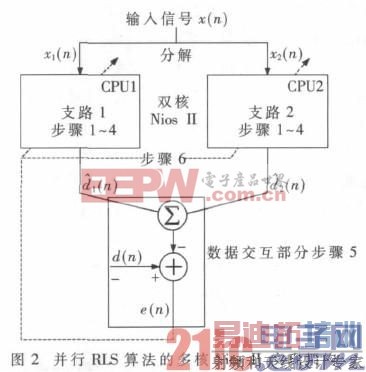

从表2可知,并行RLS算法的q值越大,算法复杂度的优化程度越高。然而,多次仿真实验证明随着q值的增加,并行RLS算法的收敛速度会变慢,性能也会受到影响。经过综合权衡后,本文使用q=2时的并行RLS算法,并采用双核Nios II进行实现,其架构如图2所示。

在并行RLS算法中,主要的滤波过程和算法更新过程都是完全独立的,可以在CPU1和CPU2中并发执行。并行RLS算法涉及到的交互数据放在共享存储区内,双核可以通过互斥机制访问。

图3为基于查找表的DPD在双核Nios II系统中的实现结构。该系统的工作状态可以经历如下阶段:

(1)DPD学习过程:DPD不加入传输链路,基带信号直接上变频后输送至PA,双核Nios II收集基带信号和PA反馈信号。

(2)并行RLS算法处理过程:双核Nios II按照图2的步骤求解出DPD模型参数向量a.(3)查找表更新过程:将a的元素值代入方程式,通过双核Nios II计算出查找表的表项值,并将表项值写入查找表RAM中,完成更新。

(4)DPD工作过程:DPD加入传输链路,构成DPD+PA的完整预失真系统。基带信号通过查表完成预失真操作。

[p]

3系统功能验证

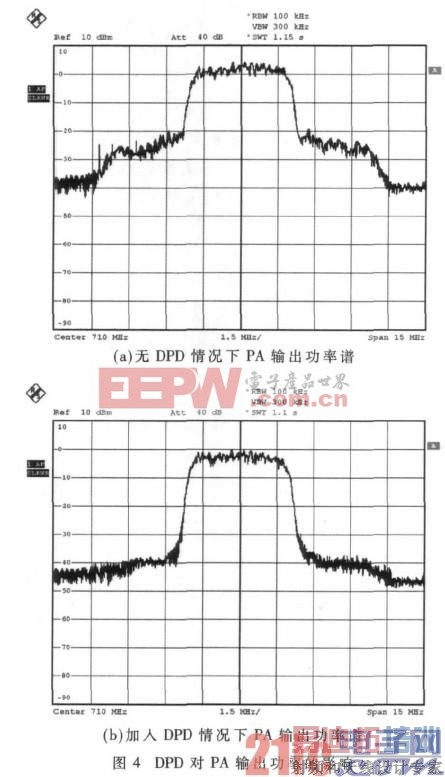

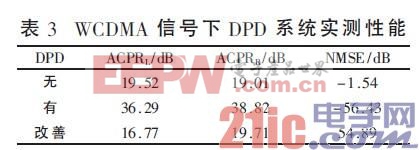

本实验中采用的功放的中心频率为710 MHz,线性增益为43 dB,1 dB压缩点为-8.5 dBm;DPD模型的多项式阶数为3,记忆深度为2,输入到PA的测试信号是具有5 MHz带宽的WCDMA信号。

通过图4和表3可见,WCDMA信号在未加入DPD前,其邻道频谱干扰严重,ACPR只有19 dB.但加入DPD后,信号的带外杂散信号得到抑制,且ACPR改善量在15 dB~20 dB之间。同时,加入DPD后系统的NMSE得到明显改善,WCDMA信号带内失真得到了控制。实验测试表明,DPD的预失真效果理想,达到了预期设计目的。

本设计在FPGA芯片中实现了一个基于双核Nios II的自适应数字预失真器(DPD)。该系统稳定可靠,能够对功放的非线性进行较好的补偿,且能够抑制信号经过功放后的带外频谱滋生,同时提高了信号在带内频谱的平坦度。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...