- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的SRAM自测试研究

引言

SRAM有高速和不用刷新等优点,被广泛用于高性能的计算机系统。由于半导体工艺技术的提高以及存储系统多方面的需要,存储器件日益向高速、高集成方向发展,在使系统功能强大的同时,也增加了系统的复杂性,给电路的故障诊断带来了不小的困难[12]。由于存储器功能和结构的复杂性,设计者为了正确地处理数据和正常地运行用户的程序,必须保证SRAM单元的寻址、取指令以及计算正确,对程序或数据存储单元的正确操作是很重要的方面,因此保证存储器的正常、稳定工作是系统稳定工作的前提。本文主要是通过对常见的SRAM故障问题的分析,运用March C算法,以FPGA构建成的SRAM自检测试电路对SRAM系统进行故障检测与修复。

1 故障模型

所谓故障模型,是指为了研究故障对电路或系统的影响,诊断(定位)故障的位置,对故障作一些分类并选择最典型故障的过程。SRAM系统可抽象为一组互联的功能模块,故障在各个模块均可发生。Van de Goor等人[3]将其简化为地址译码器、读写逻辑、存储器单元阵列3部分,并证明前两者与后者的故障在功能上是等价的,所以只需要检测存储单元阵列故障。常见的SRAM故障模型主要分为以下几个类型[4]:

① 固定故障(StuckAt Faults, SAF)。阵列中的一个或多个单元的一位或多位固定为0或固定为1。

② 开路故障(Open Faults, OF)。阵列中的一个或多个单元开路到0或开路到1。

③ 耦合故障(Coupling Faults, CF)。存储单元中某些位的跳变导致其他位的逻辑值发生非预期的变化,既可以发生在不同单元之间。也可以发生在同一单元的不同位之间。将发生在两个不同单元之间的耦合故障记为第一类耦合故障,将发生在同一单元不同位之间的耦合故障记为第二类耦合故障。

第一类耦合故障又可分为翻转耦合故障、幂等耦合故障以及状态耦合故障等。翻转耦合故障是存储器Ci单元(称耦合单元)中的跳变引起被耦合单元Cj中的逻辑值发生翻转的故障。若用“”表示逻辑值(0→1)的跳变,用“ ”表示逻辑值(1→0)的跳变,而用“ ”表示逻辑值的翻转,则这类故障可描述为眩华>或裕华>;幂等耦合故障是指在Ci中的值跳变时将Cj中的值固定为0或1,可描述为;0>、眩1>或裕0>、裕1>[5];而状态耦合故障则是在耦合单元处于一特定状态时,被耦合单元被迫处于0或1,即0;0>、0;1>或1;0>、1;1>状态。

第二类耦合故障即同一单元不同位间的耦合也有类似的情况,但当写信号很强时,同一单元不同位间的耦合就可能被淹没,只呈现出写入的信息。

④ 跳变故障(Transition Faults,TF)。阵列中的一个或多个单元的一位或多位无法在预期的时间内完成数据从0到1或从1到0的跳变,记为;0>或;1>。这种故障看似可归为固定故障,实质则有所不同。它的状态并非任何时刻都不跳变,当有翻转耦合故障影响它时就会完成原本不能完成的跳变。

⑤ 由地址译码错误引起的单元阵列故障(Address Decoder Fault,AF)。它包括某地址不能访问任何单元、某单元不能被任何地址访问、某个地址可以访问多个单元、某个单元可被多个地址访问。

2 SRAM测试方法

SRAM的测试方法主要有以下3种。

(1) 直接存取测试

直接存取测试是产生一种测试结构来允许对SRAM阵列的直接访问。它通常利用自动测试设备进行测试,可以从封装引脚直接对嵌入式存储器进行访问,或者可以从封装引脚对测试状态逻辑以及对一些为存储器提供数据的流水线结构中的串行状态进行访问,能够轻易实现多种高质量测试算法。其缺点是:在ATE机上实现的算法越复杂,对ATE机存储器的容量要求越高;在ATE机上不易实现对嵌入式存储器的“全速”测试,测试时钟的工作频率越高,测试成本越高;由于芯片外围引脚的限制,对芯片内大容量SRAM进行直接测试往往不大现实。

(2) 利用嵌入微处理器来间接测试存储器

在这种测试方法中,通过嵌入式微处理器对存储器进行读/写操作,测试向量是一系列微处理器的程序代码。这些代码可以放在程序存储器中,在嵌入式芯片接口处施加代码,测试存储器的过程就是微处理器执行测试程序的过程。其优点是不需要对硬件设计做任何修改,而且测试算法的修改与实现可以通过灵活修改微处理器代码予以完成。

(3) 存储器内建自测试(MBIST)

存储器内建自测试技术(Memory BuildIn Self Test, MBIST)的工作原理是在存储器外围产生一整套控制电路,包括数据发生、地址发生、控制产生以及结果比较等电路,实现芯片内置存储器测试模式的自动产生以及测试结果的自动判别。芯片外部的控制可以让芯片自动进入内部存储器测试模式,MBIST不仅可以自动产生内部测试模式,而且也可以实现并行测试。由于需要增加额外的逻辑电路,所以MBIST技术的缺点在于增加了芯片面积,并有可能影响芯片的时序特性。对于不同容量的存储器,MBIST电路的规模基本相同。因此,随着存储器容量的增加,这种方法所增加的芯片面积所占的比例相对较小,而且这种测试技术还有很多其他技术优势。

本文研究的是计算机内的SRAM测试方法,由于待测SRAM位于计算机系统内部,是该系统的关键部分,因此本文采用FPGA作为计算机系统与SRAM之间通信的桥梁,通过接收计算机发出的控制信号,自动产生一套SRAM自测试电路。

3 March C算法

针对存储器中的各种故障模型开发了多种存储器测试算法,如March算法、Walking算法、Galloping算法等。其中March算法是较简单的测试算法之一,具有较高的故障覆盖率和较小的时间复杂度,所以March算法是最常用的存储器测试算法。该算法经过多次改进,出现了很多变种,如MATS、MATS+、March X、March C、March C等算法[6]。

March C算法是由March元素构成的序列,其基本原理是利用有限状态机,反复对每一个地址进行读/写0或1操作,保证每两个字节之间的测试码出现00、01、10、11四种情况,至少各一次;并且为了检查高低地址读/写顺序故障,分别进行地址递增和地址递减两种操作。通过对存储器不断地读写,能够检测几乎所有的存储器故障。

在诸多的March C算法中,综合考虑算法的故障覆盖率及测试成本等因素,本文选用能够有效检测大多数存储器简化故障的March C算法。March C算法的具体描述如下[7]:

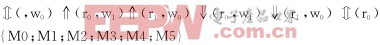

其中,“”表示地址的升序,“”表示地址的降序,“ ”表示两种顺序都可以;r0、w0、r1和w1分别表示读0、写0、读1和写1。M0~M5分别表示一个March单元,March C算法能够有效检测出 SAF、TF、CF、AF等故障。其中,SAF故障可由 M0、M1单元和 M1、M2单元检测出;TF故障中0→1故障可由M3、M4单元检测出,1→0故障可由M2、M3单元检测出;在CF故障中,1→0故障可由M2、M3单元和M4、M5单元检测出,0→1故障可由M1、M2单元和M3、M4单元检测出,置1故障可由M2、M3单元和M4、M5单元检测出,置0故障可由M1、M2单元和M2、M3单元检测出;AF故障可以在March单元的连续升序/降序中得到检测。[p]

4 SRAM自测试电路的实现

SRAM自测试电路是为了检测存储器的好坏和修复错误存储单元而对其进行自检的。文中自测试电路是由FPGA构成,通过响应计算机系统的控制信号,由其产生一套完整的自检测试电路。

4.1 硬件描述语言

测试电路的产生可以通过硬件描述语言Verilog编程实现。用Verilog来进行电路设计,设计者可以进行各种级别的逻辑设计,以及数字逻辑系统的仿真验证、时序分析、逻辑综合。它是目前应用最广泛的一种硬件描述语言。

采用硬件描述语言进行设计时,由于硬件描述语言的标准化,可以很容易地把完成的设计移植到不同厂家的不同芯片中去,并在不同规模应用时较容易地作修改。它的信号位数是很容易改变的,可以很容易地对它进行修改,来适应不同规模的应用。在仿真验证时,仿真测试矢量还可以用同一种描述语言来完成,因为采用硬件描述语言综合器生成的数字逻辑是一种标准的电子设计互换格式(EDIF)文件,独立于所采用的实现工艺。有关工艺参数的描述可以通过硬件描述语言提供的属性表达,然后利用不同厂家的布局布线工具,在不同工艺的芯片上实现。

4.2 系统硬件

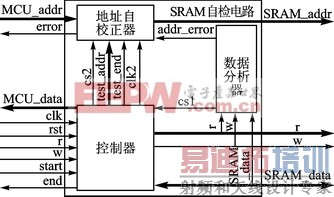

计算机系统包含有多个外围设备,在本系统中计算机与SRAM之间的通信通过FPGA来传递,计算机对FPGA的操作也就是对SRAM的操作。系统硬件电路结构框图如图1所示。

图1 系统硬件电路结构框图

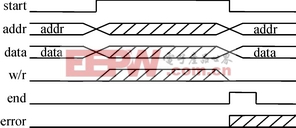

图中的start信号线是测试启动信号,上升沿有效;end信号线是测试结束信号线,上升沿有效;error是SRAM故障信号,高电平有效;addr为地址总线;data为数据总线;r/w为读/写信号线。系统时序图如图2所示,其中阴影部分为未知区域。

图2 系统时序图

在系统正常工作时,计算机系统首先将地址信号、数据信号和读写控制信号传至FPGA,通过FPGA内部电路进行处理后将信号传递到SRAM端;当start信号线有效时,FPGA启动自检电路对SRAM进行故障检测,并进行故障自校正;测试结束后输出end有效信号,对于无法修复的故障则使error信号线有效。

4.3自检电路硬件设计

由FPGA构成的自检电路主要包括检测控制电路、数据分析器和地址自校正器等部分[8],是对SRAM进行检测的关键。SRAM自检电路系统结构框图如图3所示[910]。

图3 SRAM自检电路系统结构框图

测试电路工作机制为在start信号有效时,自检电路进入自检状态[11],自检模块的控制器部分首先通过使能信号cs1启动地址校正器内的自检电路,屏蔽MCU_addr信号使test_addr、test_end和clk2工作;同时通过cs2启动数据分析器,控制器具有产生地址和测试向量的电路,测试地址通过地址校正器输出,测试向量通过SRAM_data数据线输出,通过控制线r/w进行SRAM的读写,并通过数据分析器将读到的数据进行分析;若有故障,则通过addr_error信号线通知地址校正器进行校正。在控制器按照March C算法进行测试完毕后,通过test_end信号线通知地址校正器,并使使能信号cs1和cs2无效。地址校正器接收到结束信号后,将故障单元映射到备用的SRAM存储单元,若出现故障单元超出备用部分个数或其他无法完成映射的情况,则地址校正器输出error信号。自检模块故障检测完毕后进入正常工作状态。

5 结论

本文简要地介绍了在SRAM中常见的若干故障模型,以及常用的测试方法, 最后提出了一种运用由FPGA构成的存储器自测试电路对SRAM进行检测的方法。该检测模块不仅具有对存储器故障检测的功能,而且还能将产生故障的单元进行自校正,保证系统的稳定运行。当系统有无法修复的故障时,该模块会发出故障信号。通过SRAM自检测电路的设计既提高了系统的稳定性,又大大地降低了系统的故障率。该系统测试电路由硬件描述语言编程而来,所以测试电路具有很强的灵活性,便于以后的进一步设计。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:利用CPLD实现FPGA的快速加载

下一篇:柔性电路(FPC)的特性解析