- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

利用CPLD实现FPGA的快速加载

摘要:基于SRAM的FPGA由于其可编程、可升级的特性,被广泛应用于现代通信系统中。由于其易失性,每次上电后都需要重新对FPGA进行加载。随着通信系统复杂度的提高,FPGA配置文件越来越大,加载时间越来越长,严重影响系统的启动时同。为了提高FPGA的加载效率,在此提出一种通过CPLD进行FPGA串行加载的方案。通过验证,该方法既能能提高FPGA加载效率,又能节省CPU和FPGA的GIPO管脚,降低系统启动时间,非常适用于现代复杂通信系统。

关键词:CPLD;CPU;FPGA加载;PS加载

0 引言

现代通信技术发展日新月异,通信系统必须具备良好的可升级能力以适应时代的发展。现场可编程门阵列(Field Programmable Gate Array,FPGA)由于同时具备硬件电路高速运行和软件可编程的双重优点,被广泛应用于通信领域中。FPGA在上电后,需要加载配置文件对内部各功能模块进行初始化,而配置文件加载的效率直接影响系统的初始化时间。因此如何设计一种高效的FPGA加载方案,是通信系统设计中的一个重要环节。

文献的加载方案采用外部专用的E2PROM器件存储配置文件,并在上电后由FPGA控制整个加载过程。这种主动加载的配置方式需要专门的外部存储芯片,使用面窄,无法实现灵活的在线升级,并且由于EEPROM的容量有限,只能用于加载一些小的FPGA逻辑文件。文献提出采用CPU外挂FLASH存储配置文件,采用通用输入/输出(General Purpose Input/Output,CPU GPIO)管脾模拟被动串行(Passive Serial,PS)加载时序进行配置文件加载的方案,然而这种方案需要占用CPU宝贵的GPIO资源,虽然采用PS方式加载可以节省一定的管脚,但是由于CPU没有专门的PS加载控制器,必须通过软件控制GPIO来模拟PS加载的时序,对于软件最普遍使用的C语言,每一步操作都需要数条指令,耗费时间。对于有多个FPGA,要求远程升级,且对配置速度要求高的大型系统来说,这样的加载时间是无法忍受的。

本文介绍了一种基于CPLD加载FPGA的方案:FPGA配置文件被存放在CPU外挂的FLASH存储器中,加载时由CPU将配置文件读出,再通过连接CPLD的Local Bus总线将数据以并行方式送给CPLD,CPLD利用速度较高的时钟将数据串行送入FPGA。该方案既可以节省CPU和FPGA的管脚,又可以实现FPGA在线快速加载。

1 FPGA及其加载方式介绍

FPGA是一种可编程器件,用户可通过软件手段配置FPGA器件内部的连接结构和逻辑单元,完成所需的数字电路功能。目前市场上有三种基本的FPGA编程技术:SRAM,反熔丝和FLASH。其中基于SRAM的FPGA由于其速度快且具有可重编程能力,是目前应用最广泛的一种。但是这种FPGA是易失性的,每次掉电后,FPGA恢复白片,内部逻辑消失,上电时需要重新为FPGA加载配置数据。

大部分FPGA的加载方式都可以分为主动加载和被动加载。主动加载和被动加载最大的区别在于加载过程是由谁来控制,主动加载的加载过程是由FPGA自身控制,FPGA主动从外部存储器中读取逻辑信息来为自己进行配置,FPGA内部的振荡器产生加载时钟。

被动加载的整个加载过程都是由外部控制器控制,FPGA接收配置时钟,配置命令和配置数据,给出配置状态信号以及配置完成指示信号等。

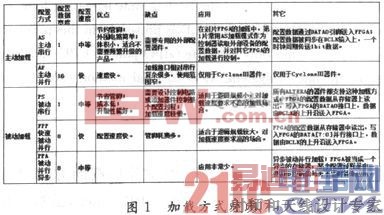

为了选择一种合适的加载方式,这里将Altera公司FPGA产品的各种加载方式的对比于如图1所示。需要注意的是,配置速度的快慢只是相对的,其他一些因素如闪存的读取时间,驱动时钟频率等也会影响配置的时间。

从图中可以看到,并行加载方式虽然速度较快但是耗费较多的管脚;而串行加载则可以节省管脚、降低成本。在几种串行加载方式中,PS加载方式是大部分器件都支持的方式,因此本文后续的设计方案选择PS加载方式进行实现。

2 加载方案的设计

整个加载方案主要由硬件电路,CPLD逻辑,软件代码几部分组成。

2.1 硬件设计

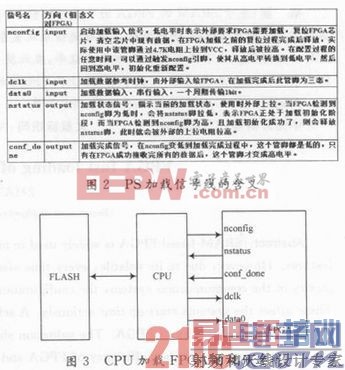

在第1节的讨论中选择了PS加载方式。PS加载一般要用到5根信号线,分别是nconfig,dclk,data,nstatus和conf_done,它们的含义如图2所示。

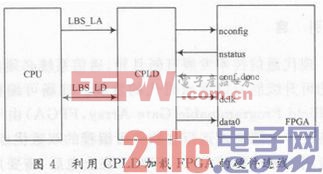

在传统的PS加载方式中,CPU与FPGA的连线如图3所示。[p]

这种加载方式的原理是:先将FPGA的配置数据放在CPU外挂非易失性存储器中,CPU启动后,CPU通过GPIO模拟时序的方式将配置数据加载到FPGA中。CPU以这种方式产生的加载时钟只有kHz,加载一个10 MB大小的配置文件大概需要100 s。通过优化代码可以减小加载时间,但是软件不能模拟高频时钟是其固有的缺陷。CPLD可以利用外部高速时钟作为加载参考时钟,且由于它控制简单,扩展方便的特性,可以作为加载的桥梁,在CPU和FPGA之间建立快速加载的通道。

利用CPLD进行PS加载的电路连接设计如见图4。

CPU要从外挂存储器中读取配置文件,然后发起加载任务,通知CPLD开始加载并通过Local Bus向CPLD发送加载数据。常用的CPU Local Bus参考时钟约为66 MHz,加载1 B的数据需要约15璐。CPLD对外部参考时钟(可选择,本文选用66 MHz晶振)进行4分频后作为加载时钟,此时钟约为16.5 MHz,其加载效率比CPU GPIO加载方式提高10倍以上。

2.2 CPLD加裁模块的设计

CPLD加载模块主要是利用CPLD逻辑代码实现PS加载时序,达到快速加载的目的。FPGA的PS加载时序如图5所示。

PS加载的过程如图6所示。

根据PS加载的时序和流程图,设计通过CPU和CPLD对FPGA进行加载的过程如下:CPLD在收到CPU发出的加载开始命令后,将nconfig信号拉低(器件时序对nconfig的低电平脉宽有要求),当FPGA收到nconfig的低脉冲有效信号后,会马上清除现有的程序进入加载状态,拉低nstatus和conf_done信号,在nconfig信号变高500 μs(器件要求)后CPLD可以开始向FPGA送时钟和数据进行加载,加载完成后,FPGA将conf_done信号拉高,递知CPLD,CPLD再通知CPU加载已完成,PPGA进入初始化阶段。

要实现成功的加载,必须保证加载过程正确,加载时序满足器件要求。还要注意与CPU软件程序的配合。

(1)nconfig信号时序的控制。nconfig信号时序控制由CPU软件实现,在硬件连接上,将nconfig信号使用外部电阻上拉,软件对CPLD寄存器中的configbit先写0,再写1,中间延迟10μs,保证nconfig信号的脉宽达到芯片要求。

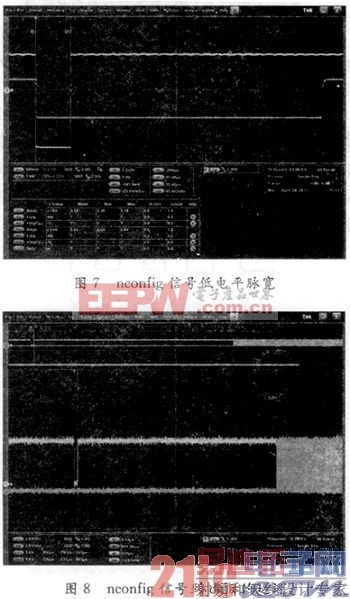

实际测试波形如图7所示,横轴表示时间,靠上的信号线为nconfig信号,靠下的为nstatus信号,nconfig脉宽约为11μs,满足要求。

(2)dclk时序的控制。dclk由CPLD的参考时钟elk_ref四分频产生。器件要求dclk在nconfig信号变高后至少500 μs后才输出,这个时序是由CPU软件来控制,软件先将nconfig信号拉低10 μs,等待FPGA回应的nstatus,当nstatus高电平到来后,延迟600μs开始通过Local Bus向CPLD发送数据,同时置位时钟使能标志位,CPLD以此时钟标志位来触发dclk,以此保证dclk的时序。实际测试波形如图8所示。横轴表示时间,靠上的信号线为nconfig,靠下的为dclk,从nconfig变高到dclk输出的延迟约为605μs,满足要求。

(3)CPLD与CPU标志位的控制实现。必须控制CPLD加载口在CPU送数据完成之后再工作,否则会引起数据阻塞。为了实现这一控制,CPU会送出一个标志位,即CPU在第一个Local Bus的访问周期发送8 b加载数据,在下一个周期CPU会对标志寄存器进行取反操作,CPLD会去检测标志位的沿(上升沿下降沿都可),当CPLD检测到这个沿,说明CPU的数据已经发送完成,CPLD会产生加载时钟,并利用此时钟将加载数据送入FPGA。CPLD只对边沿进行检测可以减少Local Bus的访问周期,如果用0,1电平或者只用上升沿(只用下降沿),CPU传送完数据后,需要先读标志寄存器的值,再对标志位进行操作,而用上升沿和下降沿,CPU只需要在第一次传送数据完成后读标志寄存器,随后的数据传送完成后只需要对其进行取反即可。实现程序如图9所示。

[p]

(4)加载模块。当检测到CPU的标志时CPLD开始发送数据对FPGA进行加载,加载完成后对自身的发送完成标志取反,关闭输出使能。要注意不同芯片厂家的加载高低位顺序不同。FPGA是靠dclk的上升沿来采样数据的,所以在dclk的下降沿将数据从CPLD送出,这样在FPGA端采样时dclk的上升沿正好对着数据的中间,能获得最大的时序窗口,如图10所示。

实现程序如图11所示。

(5)加载结束后,FPGA将conf_done信号拉高,CPLD通知FPGA加载已经完成。

3 功能、性能测试

为了验证方案的有效性,选用Altera的FPGA(EP4SGX530),CPLD(EPM570F256CS),MPC8548搭建了一个加载系统,测试结果如图12所示,横轴表示时间,有固定周期的信号为dclk。由图可知加载成功,加载时钟频率约为17 MHz。总体加载时间可由conf_done信号指示,如图所示横轴表示时间,从图上可以看出,加载一个10 MB大小的FPGA配置文件大约需要10 s。

4 结论

CPU直接对FPGA进行加载的传统方式,加载一个10 MB的FPGA配置文件大概需要100 s,利用CPLD对FPGA进行加载,只需要约10 s(Local Bus的访问周期约为200 ns,相对于CPLD对FPGA的加载时间可以忽略不计,两者可以并行进行),加载速度提高了10倍左右。在有两个甚至多个FPGA需要加载的系统,其优势更为明显。该方法对只要有CPU,CPLD和FPGA的系统即可移植,并且可以支持Altera,XILINX和LATTICE三大厂家的逻辑器件。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:印制电路板的设计技巧

下一篇:基于FPGA的SRAM自测试研究