- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于CPLD的智能拨号报警系统设计

随着经济的发展和生活水平的提高,个人安全和财产安全越来越被人们重视。为了不受到伤害和损失,就需要有安全的报警系统。现在的报警系统多数是以单片机作为主控制器,连线复杂,可靠性和稳定性不高[1-2].针对以上不足,本文利用EDA技术对报警系统进行设计,系统以CPLD芯片作为控制核心,采用VHDL语言硬件描述来实现远程的智能报警,结构和接口简单,工作可靠性高。

1系统原理和组成

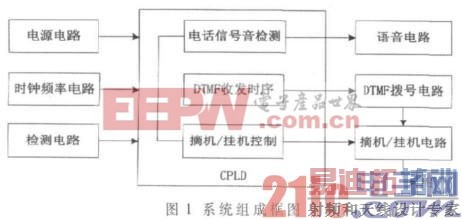

系统组成框图如图1所示。系统由两部分组成:外围电路和CPLD控制电路。外围电路包括检测电路、语音电路、DTMF拨号电路、摘机/挂机电路、时钟频率电路、电源电路。CPLD控制电路包括电话信号音检测模块、双音多频信号DTMF收发时序模块和摘机/挂机控制模块。外围电路和CPLD控制电路相协同来实现系统的报警。

系统工作原理:当有人非法进入室内时,检测电路中的传感器便采集到入侵信号,入侵信号会启动摘机/挂机控制模块控制摘挂机电路实现电话摘机。摘机后,电话信号音检测模块识别电话系统的状态是否处于可拨号状态。如果是,则DTMF收发时序模块控制DTMF拨号电路以双音频DTMF方式拨预定的电话号,语音电路播放所要报警的报警信息;否则,通过摘机/挂机控制模块控制挂机电路实现电话挂机,延时后再拨。

系统中检测、DTMF拨号、摘机/挂机等功能使用硬件电路来实现,电话语音识别、DTMF收发时序、摘机/挂机控制等功能使用软件编程来实现。

2系统外围电路

2.1检测电路

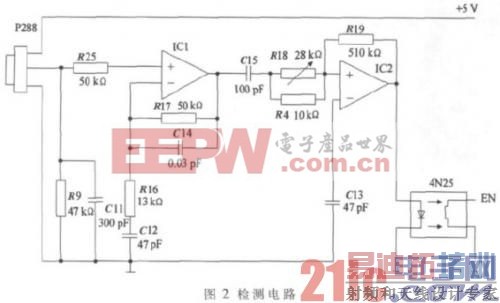

本系统采用热释电红外传感器P228进行探测[3],检测电路如图2所示。当有人进入时,P288检测到的信号经C11高频滤波直接输入到放大器IC1进行低噪声、高稳定放大。当IC1输出电压高于IC2的基准电压时, IC2也输出高电平,驱动光电隔离器4N25导通,输出入侵信号EN,作为报警系统的启动信号提供给主控电路。

2.2语音电路

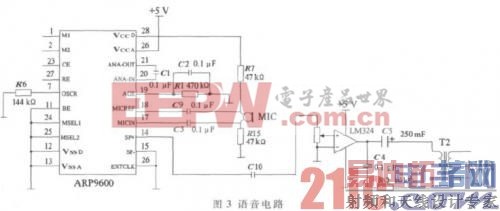

语音电路用于录制和播放所要报警的语音信号或其他报警信息,相应信息可由用户预先设定并可随时修改。本系统中的语音电路选用语音录放芯片APR9600.录音时外部音频信号经芯片APR9600内部具有自动增益调节的话筒放大器放大,由内部滤波器和采样电路处理后存入专用快闪存储器Flash RAM中。放音时芯片内部逻辑电路从Flash RAM中取出信号,经过一个低通滤波器送到功率放大器,然后经音频功率放大器放大后输送到电话线路上,电路如图3所示。

[p]

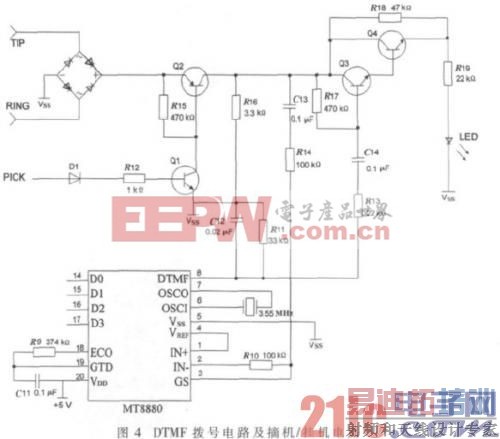

2.3 DTMF拨号电路和摘机/挂机电路

DTMF拨号电路是整个系统的关键部分,它的运行状态决定了系统的可靠性。本系统采用专用双音频解码集成芯片MT8880,MT8880是专门用于处理DTMF信号的专用集成电路,具有接收和发送该信号的双重功能,其电路如图4所示。MT8880以1、2脚IN+、IN-作为DTMF的输入端,对应内部一个差分放大器,可以双端输入,又可单端输入,本电路采用单端输入。8脚是DTMF信号的输出端,主控电路将预先存储的电话号码通过数据线D0~D3送入MT8880内部的数据缓冲器,此时RS和R_W都是低电平,数据写入TDR,再通过内部线路处理,利用D/A变换,在电路选通CS=0时,从8脚输出标准的DTMF信号。MT8880输出的DTMF信号不能直接与电话线连接,因为36 V左右的电话线空载电压极易烧毁MT8880,故在它们之间通过一个放大器与电话线路相接,此放大器可以用运放也可以用分立电路,图4为分立电路。

摘机/挂机电路主要由Q1、Q2、D1、R12构成,利用Q1和Q2的截止和饱和起到开关作用,从而实现摘机和挂机。

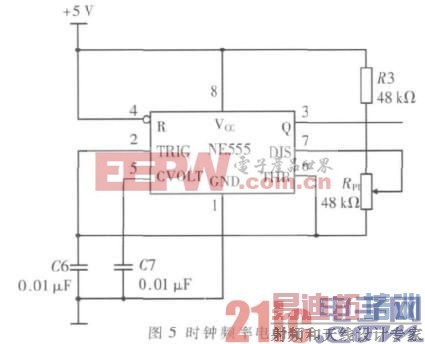

DTMF拨号电路和摘机/挂机电路的工作过程:当需要向电话网发送预先存储的电话号码时,PICK=1,通过D1和R12使Q1和Q2处于饱和状态。从电话线TIP和RING两端来的电压使Q3和Q4得到正常偏置处于放大状态,此时R_W=0.使MT8880的CS=0,芯片被选中,DTMF信号从MT8880的8脚输出,经过R14、C18送到Q3的基极,经Q3、Q4的放大后从电话线路输出,此时发光管LED点亮显示发送状态,平时非发送状态时,PICK=0,Q1、Q2、Q3、Q4处于截至状态,CS=1,MT8880不能被选中,它的8脚内部电路处于高阻抗状态,电路与电话线隔离,不影响正常电话机的使用。接口电路由电话线电压供电,平时36 V左右,工作时为9 V. 2.4时钟频率电路时钟频率电路由555定时器和外接元件R3、RP1、C6构成多谐振荡器,脚2与脚6直接相连,如图5所示。电路没有稳态,仅存在两个暂稳态,且不需要外接触发信号,利用电源通过R3、RP1向C6充电,以及C6通过RP1向放电端放电,使电路产生振荡,从而在输出端为主控电路提供1.1 kHz的时钟频率。

[p]

3 CPLD的系统设计和逻辑仿真

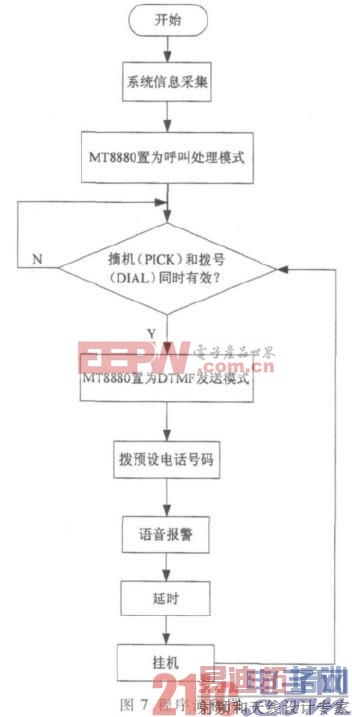

系统控制核心CPLD的三个控制模块都是采用VHDL语言编程来实现的[4-5],其中电话信号音检测模块DJF1用来检测公用电话网络传递的语音信号,摘机/挂机控制模块DJF2用来控制摘机/挂机电路,实现电话的接通和关断,DTMF收发时序模块DJF3控制DTMF拨号电路自动拨打预先设定好的电话号码。系统的主程序流程图如图7所示。

系统的工作过程:当红外传感器检测到人体入侵信号EN后,摘机/挂机控制模块启动并产生摘机信号PICK,使摘机/挂机电路进行摘机。摘机后,DTMF收发时序模块将MT8880设置为呼叫处理模式。然后电话信号音检测模块通过对IRQ的计数判别电话音是否为拨号音。如果不是拨号音,则电话挂机,然后再摘机重拨。如果是拨号音,则MT8880设置为DTMF发送模式,同时MT8880拨打预置电话和发送语音报警信号。发出报警信息后延时,电话信号音检测模块检测电话音是否为回铃音。如果是,则延时挂机;如果不是,则挂机重拨。

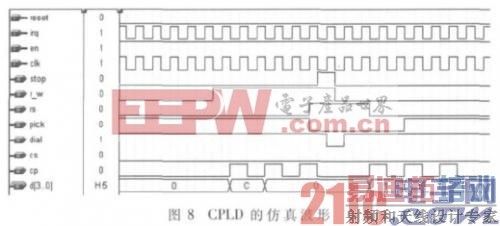

CPLD芯片采用的是Altera公司的EPM240芯片,该芯片具有片内存储器,系统掉电和复位后不用重新向芯片下载程序就能正常工作。系统设计完成后,对三个功能模块进行逻辑编译、逻辑综合及优化、逻辑布局布线、逻辑仿真,然后将生成的配置文件下载到CPLD芯片。将功能模块进行时序仿真验证,仿真波形如图8所示,可以看到功能模块达到所期望的逻辑功能。

本文采用CPLD控制核心实现了智能报警系统。由于利用EDA技术进行系统设计,外围器件少、体积小、功耗低、可靠性高。通过修改VHDL源程序就可以增加一些新的功能,提高了设计的灵活性,具有较好的应用前景。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:基于FPGA的视频监控时代

下一篇:解析FPGA设计流程及其布线资源