- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的彩屏控制器设计

触摸屏技术方便了人们对计算机的操作使用,是一种极具发展前途的交互式输入技术,受到各国的普遍重视,并投入大量的人力、物力对其进行研发,使得新型触摸屏不断涌现[1]。特别是四线电阻式触摸屏具有制造工艺简单、成本低廉、使用方便等特点,已经被广泛应用于不同的电子设备[2]。

随着嵌入式技术的高速发展,尤其是CPLD/FPGA的出现,其基于SoPC技术的IP核的使用给开发人员带来了诸多方便。但在SoPC中并没有彩色触摸屏的IP核,因此需要自己编写硬件的时序控制[3]。本文提出一种基于FPGA的彩色触摸屏控制器的设计方案,通过单片FPGA芯片可以实现彩色触摸屏的驱动逻辑,从而实现硬件上时序控制,在此控制器的基础上可以进一步开发彩色触摸屏的IP核。

1 彩色触摸屏控制器的设计

1.1 总体结构及其工作原理

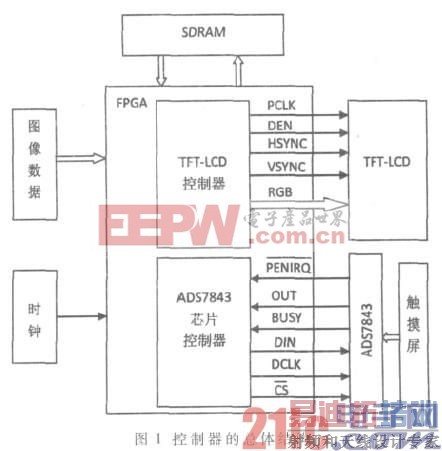

彩色触摸屏控制器的总体结构如图1所示。

该彩色触摸屏的控制器主要由TFT-LCD控制器和ADS7843芯片控制器两部分组成。由图1可以看出,TFT-LCD控制器的作用是将图像数据采集后,通过SDRAM进行缓冲,然后将图像数据输出给TFT-LCD。它的主要功能是完成图像数据的采集和缓冲、TFT-LCD的时序控制及最终数据在TFT-LCD上的显示。

1.2 TFT-LCD控制器的设计

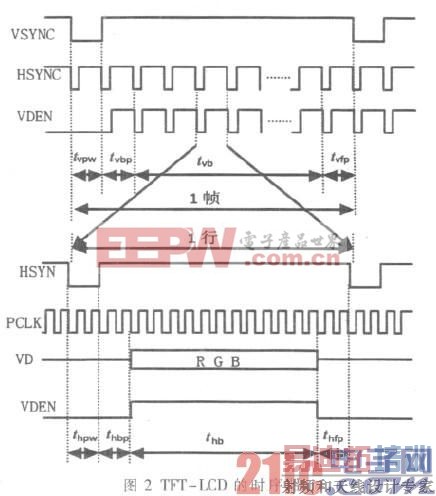

图像数据经采集和缓冲之后,通过TFT-LCD的时序控制可以将数据按如图2所示时序图进行输出。本设计中采用的TFT-LCD的分辨率为480×272,其RGB数据位均为8 bit,可以显示16 777 216种颜色。其中,PCLK为LCD像素时钟信号,HSYNC为行同步信号,VSYNC为帧同步信号,VDEN为数据使能信号,VD[23:0]为LCD像素数据输出端口,tvpw、tvp、tvbp、tvfp分别为垂直同步脉冲、垂直扫描时间、垂直后回归、垂直前回归,thpw、thp、thbp、thfp分别为水平同步脉冲、水平扫描时间、水平后回归、水平前回归[4]。

从图2所示的时序图可以看出,当HSYNC电平由低变高,再经过水平回归时间之后,开始进行水平扫描。在水平扫描中,像素的显示受PCLK控制,一个PCLK周期决定了一个像素点的显示。在HSYNC的高电平的驱动下,PCLK将产生480个时钟周期,使图像的像素点在屏幕上从左向右依次逐点输出,完成一行共480个像素点的显示。用Verilog HDL编写的水平同步扫描的时序程序如下:

[p]

always@(posedge CLK or negedge RST_n) begin

if (RST_n) begin

x_cnt = 11'd0;

hd = 1'd0;

end

else if (x_cnt ==479) begin

x_cnt = 11'd0;

hd = 1'd0;

end

else begin

x_cnt = x_cnt + 11'd1;

hd = 1'd1;

end

end

同理,当VSYNC电平由低变高,再经过垂直回归时间之后,进入垂直扫描。在VSYNC的高电平驱动下,HSYNC将产生272个时钟周期,像素点在屏幕上从上到下依次逐行输出,完成整个图像数据在彩色显示器上的显示。用Verilog HDL编写的同步扫描的时序程序如下:

always@(posedge CLK or negedge RST_n) begin

if (iRST_n)

y_cnt = 10'd0;

else if (x_cnt == 479) begin

if (y_cnt == 271)

y_cnt = 10'd0;

else

y_cnt = y_cnt + 10'd1;

end

end

1.3 ADS7843 芯片控制器的设计

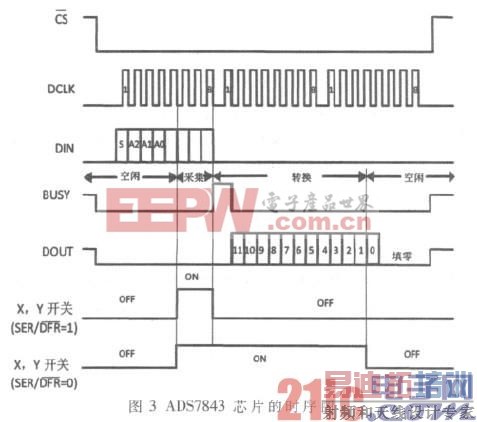

ADS7843 芯片控制器用于将触摸的位置进行数据转换。ADS7843 的时序图如图3 所示。其中,CS 为片选信号, 低电平有效;BUSY 为忙指示信号, 同样低电平有效。

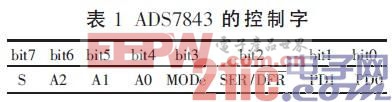

由图3 可看出,ADS7843 标准的一次数据转换需要24 个时钟周期, 每次的数据转换以8 个时钟周期为一次通信, 需要与控制器进行3 次通信。第一次通信是触摸控制模块的DIN 端口通过串口向ADS7843 发送控制字, 同时对X、Y 的电压值进行采集。控制字如表1 所示, 其中,S 为数据传输起始标志位;A2~A0 为通道选择;MODE 为A/D 转换精度控制位;SER/DFR 为参考电压的输入模式[5]。

[p]

将控制字以串行的方式写入到内部寄存器的Verilog HDL代码如下所示:

if (dclk)

data_in = {data_in[6:0],1'b0};

第二、三次通信则是ADS7843 将触摸后的X、Y的电压值转换为16 bit数据赋值给DOUT端口,然后芯片采集其高12 bit数据,低4 bit自动补零。本设计将采集到的串行的12 bit数据转化为并行的12 bit数据,其Verilog HDL代码如下:

if (!dclk)

begin

if(rd_cd_strob)

begin

if(y_cde_config)

y_cde={y_cde[10:0],adc_out};

else

x_cde={x_cde[10:0],adc_out};

end

end

2 实验结果

2.1 仿真验证

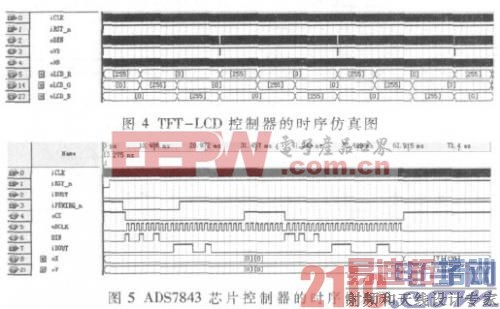

整个控制器是在Quartus II 8.0中设计并仿真的。仿真分为两个部分,包括TFT-LCD控制器的时序波形和ADS7843芯片控制器的时序波形。仿真结果分别如图4、图5所示。

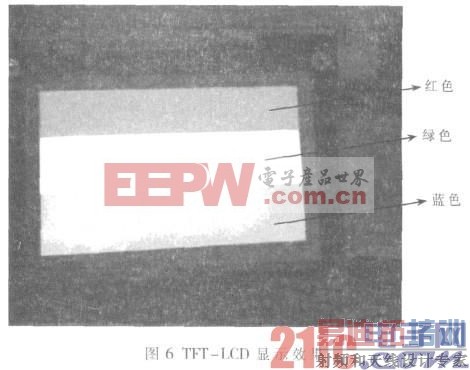

由图4可以得出,在一帧的数据(oVD的一个时钟周期内的数据)中,前1/3帧显示红色(oLCD_R对应255),中间1/3帧显示绿色(oLCD_G对应255),后1/3帧显示蓝色(oLCD_B对应255);则相应的屏幕上1~90行显示为红色、91~180行为绿色,180~272行为蓝色,如图6所示。

下面分析X坐标值。由图5可以看到,当产生触摸时笔中断信号PENIRQ变为低电平,此时片选信号CS变为低电平,其低电平维持时间为24个DCLK时钟周期,在前8个时钟周期DIN端口写入控制字为10010010,在第10个时钟DOUT端口开始接收转化的12 bit数据,其值为011110001000。同理可分析Y坐标值。在DOUT端口接收X、Y坐标值之后,通过串并转换最终得到并行输出的X、Y的坐标值,如图5中的oX和oY端口所示。

2.2 最终显示效果

FPGA采用Altera公司的EP2C70F896C6;彩色液晶触摸屏采用台湾东华公司的WXCAT43-TG3#001R。最终的显示效果如图6所示。

使用Verilog HDL编写触摸界面过于复杂,通过软件设计触摸屏操作界面则需要编写彩色触摸屏的IP核,本设计基于FPGA的彩色触摸屏控制器能够实现颜色深度为24 bit,分辨率为480×272的TFT-LCD控制和ADS7843芯片的时序控制,为后续IP核的编写工作打下了基础。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:多惯组脉冲输出同步计数系统设计

下一篇:基于FPGA的高频率ADC的实现