- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的可逆数制转码器设计

摘要:针对二-十进制(BCD)数据相互转换的FPGA实现目标,基于模块层次化的设计思想,提出了一种高效、易于重构的可逆转码器设计方案。并在FPGA(Altera DE2)开发板上成功进行了12 b可逆转码器的设计验证,实验结果表明该转码器通过端口参数配置就可以完全实现不同位数的二-十进制(BCD)数据间的相互转换。

关键词:二-十进制(BCD);可逆转码器;FPGA;逻辑单元;TPD

0 引言

在数字系统的数据输入、运算、输出过程中,输入和输出常用十进制形式表达;而在系统内部采用二进制表示和处理数据则更为方便,因此在二进制和十进制数据间的转换就是非常必要的。此外,数控机床、智能仪表、电子秤和数码管等显示设备也会频繁地用到十进制(BCD)码与二进制(BIN)码的相互转换。目前,数字系统中BCD码和BIN码的相互转换有3类实现方法,首先是采用软件算法的实现方式,传统的是用DAA调节指令实现,但效率较低,不能满足一些实时应用的要求。其次是纯硬件运算实现方式,这种实现方式是数据转换运算到硬件的直接映射,常采用逻辑运算和数据移位来实现数据转换,转换效率较高,可以根据输入数据位宽进行转换器的位数扩展和重构。但是在转换数据位数较多时,运算量会显著增加、硬件实现代价也较大、路径延迟也会增大、整个转换器的时序控制也会变的比较复杂,也很难做到可逆转码运算。最后是基于数据查找表(Look Up Tabie,LUT)的实现方式,也就是先把全部或部分转换数据列表存储在存储器中,然后再根据转码器的输入数据(地址码)直接或间接地从存储器中取出所需的输出数据,这种以查找表为核心的转换器运算速度快、算法直接简单;但是会需要大量的存储器;并且这种实现方法往往是针对具体的转换数据位宽和单一转换方向来定制存储器(ROM)容量和存储器初始化数据;一旦需要转换的数据位数和方向发生变化,就根本无法实现转换器的数据位数扩展和结构重构,所有的设计就必须重新开始。

基于FPGA的可逆数制转码器设计,充分利用FPGA的结构特点和硬件描述语言(Veilog HDL)的抽象和灵活性;二-十进制(BCD)转码器不但具有可配置双向转换数据的功能,而且还要求转码器简单、高效和易于位数扩展(模块化重构)。因此,文中就提出了一个高效、易于重构的二-十进制(BCD)可逆转码器设计方案,通过端口参数配置和模块重构就能实现不同位数的数据在二进制和十进制(BCD)之间相互转换,最后

在FPGA(DE2)开发板上成功地进行了设计验证。

1 数制的转换算法

假设X=(xn-1,xn-2,…,x0)p表示n位p进制数据,Y=(ym-1,ym-2,…,y0)q表示m位q进制数据,二者之间等值变换的条件为:

![]()

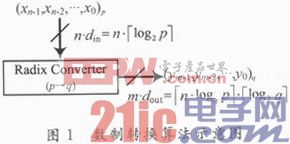

这里,X,Y所表示的数值范围分别是[0,pn-1]和[0,qm-1]。而在二进制编码体系下,要把一个n位p进制数据转换为m位的q进制数据就要求输入输出的数据位宽必须满足m=Ceil[n·logqp]=[n·logqp],这里用“∏”表示整数上确界Ceil运算,输入输出数据位宽关系如图1所示。

图1中的din=Ceil[log2 p]=[log2 p];dout=Ceil[log2 q]=[log2 q]分别表示1位输入输出数据的二进制位宽,例如1位的八进制数据需要3 b二进制数表示;而1位的十进制数据需要4 b二进制数表示,所以X→Y转化的输入、输出数据位宽(单位:b)分别为:

n·din=n·[log2 p] (2)

m·dout=[n·logq p]·[log2 q] (3)

8421BCD码是使用4 b二进制数表示1位10进制数(0~9)。如果把n位二进制数据转换成m位BCD码(4m位)就要求m位BCD码所能表示的最大数不小于n位二进制码所表示最大数,即10m-1≥2n-1,m≥Ceil[lg 2n]=『n·lg 2]。如果12位的二进制数转换成十进制(BCD),根据式(3)算出输出m位的十进制数据m=[n·logq p]=[12·lg2]=4;输出数据位宽m·dout=m·[log2 q]=16 b。

2 二-十进制可逆转码器设计

2.1 可逆转码器的层次化设计

在片上数字系统(SOPC)中实现二-十进制(BCD)码转换器,就要求设计者充分利用硬件(FPGA)的结构特点和硬件描述语言(HDL)所提供的设计灵活性;更好地实现转码器的简单、高效和结构易于扩展。为此,针对FPGA的结构特点提出了以下设计思路:以4 b数据转换作为基本的可逆转换单元来适应FPGA结构特点,而提高逻辑单元利用率、达到降低硬件代价的目的;利用Verilog HDL进行层次化设计描述,以4 b数据转换单元为最底层模块,构造出更大的5 b和6 b可逆转换单元(模块),这样会在不增加实现代价的前提下,实现使用大的转码单元模块来简化转码器的结构、方便转码器的位数扩展;这种设计方法就为二-十进制(BCD)可逆转码器的构建提供了4 b,5 b和6 b三种不同大小的单元模块,这会让每一个转换单元模块都使用到恰到好处(需要小模块的地方就不会使用大模块);有效避免了单元模块利用率不高的问题。[p]

2.2 可逆转码器的功能模块设计

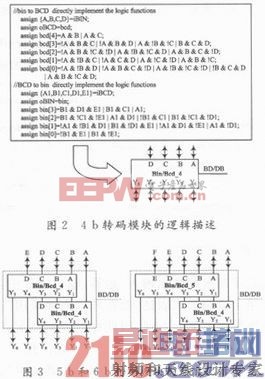

上述基于FPGA的二-十进制(BCD)可逆转码器设计方案,关键就在于要做好最底层模块(4 b转码模块)的优化设计,对4 b转码模块的不同Verilog HDL描述方式也会带来不同的实现代价;通过不同描述方式比较最终确定使用结构描述来实现4 b可逆转码模块(Bin/Bcd_4),根据参考文献[4-5,10],采用卡诺图和Multisim软件化简得到最简逻辑函数式如图2所示。再通过4 b转码模块层次实例化分别构造5 b转码模块(Bin/Bcd_5)和6 b转码模块(Bin/Bcd_6),如图3所示。

[p]

2.3 12 b可逆转码器的结构设计

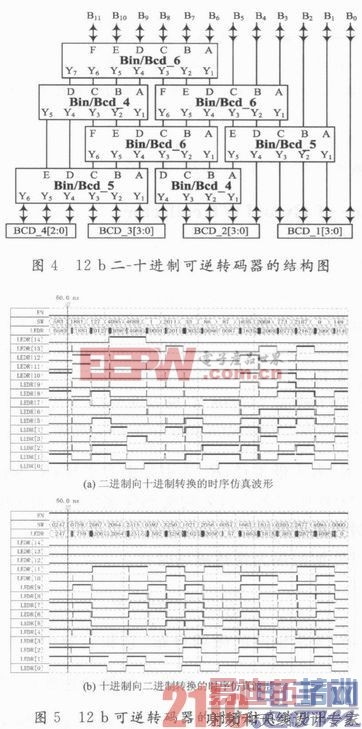

根据二-十进制可逆转码算法,使用上节中得到的4 b,5 b和6 b三种二-十进制可逆转码单元模块,构造出12 b二-十进制(BCD)可逆转码器结构如图4所示,转码单元模块的多余输入端要接地,多余输出端悬利于转码器的位数扩展,也可以通过转码器的使能端BD/DB的取值分别实现从二进制到十进制和从十进制到二进制的数制转换。

3 二-十进制可逆转码器的设计验证

3.1 可逆转码器的时序仿真

使用QuartusⅡ9.1(Full Version)开发工具;对于图4中二-十进制(BCD)可逆转码器,在Altera公司的FPGA(EP2C35F672C6)芯片上进行了设计验证,验证结果完全达到了既定的设计目标;时序仿真结果如图5所示。在图5(a)中,使能信号EN=0,转码器实现12 b二进制数向4位十进制(BCD)数据的转换,SW是输入12 b二进制数,LEDR是输出的4位十进制(BCD)数(15 b,最大值是4 095);在图5(b)中,使能信号EN=1,转码器实现15 b十进制数(最大4 095)向12 b二进制数据的转换,SW是输入15 b十进制数(BCD),LEDR是输出的12 b的二进制数。

3.2 可逆转码器的性能分析

使用QuartusⅡ9.1开发工具和DE2开发板;对于所设计可逆数制转码器通过模块的参数配置,分别测试了转码器在完成8 b、10 b和12 b转码情况下的硬件实现代价(占用逻辑单元数LEs)和最大路径延迟(TPD),测试结果见表1。

表1表明,可逆转码器的数据位宽愈大转码器就越复杂,使用的单元模块就越多,实现代价增大,路径延迟也会增大,12 b可逆转码器的最高时钟频率只有50 MHz,而8 b的可逆转码器最高时钟频率可以达到75 MHz。

4 结语

文中提出以3种功能模块来构造二-十进制(BCD)可逆转码器的设计方法,通过端口参数配置和模块重构就能实现不同位数的数据在二进制和十进制(BCD)之间相互转换。从而使基于FPGA的二-十进制(BCD)转码器的构建变得简单、灵活。可逆转码器在EP2C35F672C6芯片上的验证结果也充分证明了这种设计思路的可行性;如果进一步在转码器中插入寄存器而形成流水线结构,那么转码器的运算速度就会有更大提升。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:FPGA与CPLD的区别有哪些?

下一篇:CPLD可编程方案的优点简介