- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的视频采集显示系统

摘要 设计实现一种基于FPGA的视频采集显示系统,包括视频图像的采集、处理与显示3个部分。视频图像部分采用CCD摄像头OV7670作为视频数据的采集,利用在FPGA中构建FIFO并配合SDRAM高速读写实现视频图像数据的高速缓存处理,使用FPGA中构建的Nios Il嵌入式内核,实现对SDRAM的控制以及视频数据的TFT液晶实时显示。整个系统获得了较好图像采集、显示效果。

关键词 FPGA;视频处理;TFT LCD;Nios II

随着高品质实时视频显示技术低,民用领域如天气预报、资源探测、机器人视觉以及各种医学图像的实时分析;军用领域如导弹精确制导、战场动态分析等,均需要高质量实时视频显示系统的支持。近年来低成本的FPGA(Filed Programmable Gate Array)不断推陈出新,利用EDA工具对FPGA芯片进行多样性设计,已经成为电子设计的通用平台,并逐步向支持系统级设计的方向发展。与专用集成电路相比,FPGA芯片

具有快速的定制性和高灵活性,扩展性强的特点。作为一个平台,FPGA已适用于高性能低成本的视频和图像处理,尤其在图像分辨率和帧率要求较高的场合。

设计采用CMOS图像传感器OV7670对外界图像进行实时采集,通过FPGA内部设计的初始化模块对图像传感器输出信号的格式进行配置。根据其输出信号的时序,在FPGA内部设计采集单元。采集到的数据经过格式转换送到内部配置的Nios II嵌入式内核,Nios II嵌入式内核将实现LCD显示屏控制与视频数据的实时显示。

1 系统总体设计

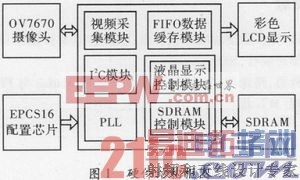

基于FPGA实现的视频显示系统的整体结构框图如图1所示。系统主要分为:视频采集模块、PLL锁相环时钟管理模块、I2C总线模块、FI FO视频数据处理模块、Nios II显示控制模块。系统中PLL负责为NiosII嵌入式内核、外部SDRAM和OV7670摄像头提供时钟,系统通电后,FPGA首先从EPCS中读取配置数据,完成自身程序加载,随后对系统时钟分频为摄像头提供系统时钟,然后通过I2C总线完成对OV7670摄像头的配置。

配置完成后,OV7670将采集到的视频数据输出格式转换成RGB565标准的视频数据及图像时钟送入FPGA进行处理,并将处理后的图像数据通过FIFO模块暂时存储在SDRAM中进行缓冲,同时Nios II模块读取存放在SDRAM中的视频图像数据,按照TFT液晶显示的时序、数据要求将视频图像数据送到TFT彩色液晶显示屏上显示。

1.1 FPGA选型

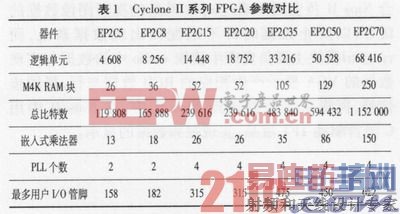

FPGA是该系统的核心,由于系统目前只是完成简单的图像处理,故FPGA选用Altera公司的低成本FPGA Cyclone II系列器件。Cyclone II系列器件简介如表1所示。

Cyclone II器件采用90 nm工艺制造,它延续Cyclone的低成本定位,在逻辑容量、PLL、乘法器和I/O数量上都比Cyclone有了较大提高,应用Cyclone II进行图像处理开发有如下优点:(1)低成本高性能,适应图像处理要求较高的需要。(2)丰富的内嵌存储器资源,适应大量图像数据存取的需要。(3)丰富的硬件乘法器,适应图像处理算法的需要。系统的FPGA选用开发板自带的EP2C5Q208C8芯片。[p]

1.2 视频采集模块选择

视频图像采集采用OmniVision公司的OV7670图像传感器,OV7670图像传感器体积小、工作电压低。OV7670摄像头的VGA图像最高达到30帧/秒。通过SCCB总线控制内部寄存器,可以使OV7670输出整帧、子采样、取窗口等方式的各种分辨率的图像数据。用户还可以完全控制图像质量、数据格式和传输方式。OV7670与FPGA硬件连接如图3所示。

OV7670不具有内部时钟,视频图像采集前需要为OV7670提供系统时钟,频率为25 MHz,是对FPGA系统时钟二分频得到。

1.3 视频采集与视频图像处理

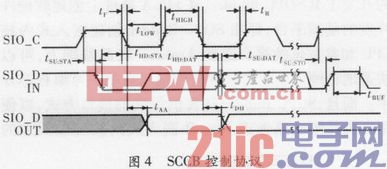

SCCB是OmniVision公司定制的串行摄像头控制总线(Serial Camera Control Bus),它用于对摄像头的寄存器进行读写,以达到对摄像头输出图像的控制。两线制SCCB与I2C总线兼容,是一种双向二线制同步串行总线。它的最大频率为400 kHz。根据协议把数据写入寄存器和读取寄存器的数值。SCCB的时序图,如图4所示。

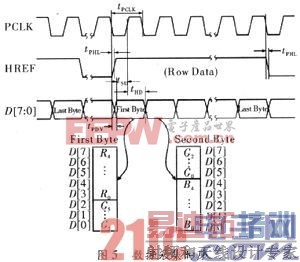

在初始化程序中,已经把OV7670配置为输出QVGA格式,16位图像数据格式为RGB565。其中VSYNC为帧同步信号,HREF为行同步信号,只有按照上图中严格的时序,即OV7670输出的时序,才能采集到正确的图像数据。采集到的RGB565格式数据符合如图5所示的标准。

在每一个行同步信号上升沿输出视频图像数据,在输出RGB565格式情况下,一帧数据可分为两次发送,第一次前一帧发送RGB的R数据的5位与G数据的高3位,后一帧发送G数据的第3位与B数据的5位,在数据处理时要对这两帧数据进行拼接,然后送入数据处理部分。[p]

为防止视频图像数据在采集与显示存在不同步的情况,在两极之间构建了FIFO并配合SDRAM以实现对采集数据的暂存,FIFO的写使能与摄像头的行同步信号相连,当行同步信号有效时开始写FIFO,当FIFO空标志位为低时电平表示FIFO中已存入数据,则NiosII开始控制SDRAM从FIFO中读取视频数据,这样操作的特点就是将经过缓存的数据流无停顿地传送到输出端,因此适合对时序不连续的像素进行无缝缓冲处理。

1.4 视频图像显示模块

视频图像显示通过在FPGA中构建的Nios II嵌入式内核实现,Nios II系统可以在设计阶段根据实际的需求来增减外设的数量和种类。可以使用Altera提供的开发工具SOPC Builder,在FPGA器件上创建软硬件开发的基础平台,即用SOPC Builder创建嵌入式内核CPU和参数化的接口总线Avalon。在此基础上,可以快速地将硬件系统与常规软件集成在单一可编程芯片中。而且,SOPC Builder还提供标准的接口方式,以便用户将外围电路做成Nios II嵌入式内核可以添加的外设模块。这种设计方式,方便了各类系统的调试。

2 系统软件设计

2.1 软件模块介绍

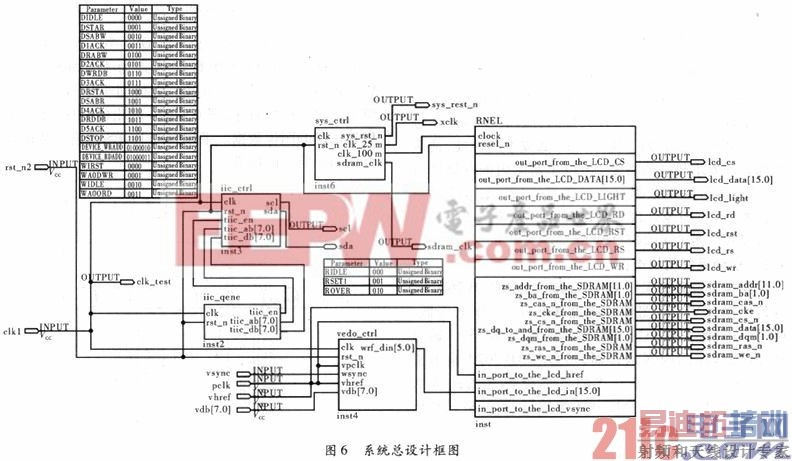

系统软件总设计模块如图6所示,在sys_ctrl中建立PLL锁相环对时钟倍频、分频产生系统各模块所需时钟与系统复位信号,vedio_in put模块负责OV7670摄像头的初始化与视频图像数据的采集,wrfifo模块配合Nios II负责对vedio_input采集的视频图像数据的缓存,以防止数据时钟不匹配而出现数据紊乱,而vga_ctrl模块主要负责产生读取wrfifo中的数据与实现数据的VGA显示产生相应的RGB数据与行、场同步信号,再将采集数据送到Nios II中,在Nios II中用C语言驱动TFT液晶,实现视频数据的显示。

2.2 Nios II嵌入式内核程序设计

Nios II嵌入式内核主要任务是将rag_ctrl采集数据送入SDRAM暂存,然后再根据显示需要将暂存的数据读取出来送到LCD显示,为了确保显示图像与采集图像的一致,在送LCD显示数据时要注意以下几点;

(1)根据实际情况去除行、场消隐数据,再根据显示内容的多少对数据进行裁剪,裁剪到适合LCD显示的大小,从而避免显示时图像的错位以及乱码等情况。

(2)由于嵌入式内核时钟频率相对于摄像头的大量数据来说速度还是难以做到摄像头采集的每幅图像都能完全显示,所以在设计中采用隔场采集处理的方式,这样避免SDRAM中数据过多以至于被填满的情况,也解决了嵌入式内核采集的出现的卡屏的情况。

3 结束语

采用FPGA设计并实现了一种视频显示系统,大幅减少了电路板的尺寸,节约了成本,同时增加了设计的灵活性和系统的可靠性,充分应用FPGA快速并行处理数据的特性,在产生同步信号的同时送出像素数据。嵌入式内核Nios II的使用,解决了其他系统实时图像显示的体积与速度问题,扩展了应用范围。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...