- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的实验室可重构信号源的设计

摘要 介绍了以直接频率合成技术DDS为基础的信号发生器基本工作原理及设计过程,并以单片机和FPGA为核心实现了波形、频率、幅值均可调节的信号发生器设计。经测试验证,该信号发生器取得了理想的结果,达到了设计要求。

关键词 单片机;FPGA;DDS;信号发生器

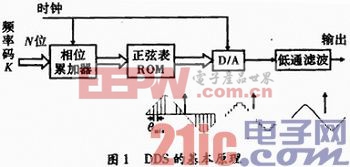

1 直接数字频率合成技术

直接数字频率合成技术(DDS)是近年来迅速发展的一种新型频率合成方法,它将先进的数字处理理论与方法引入信号合成领域,通过控制相位变化的速度来直接产生各种不同频率的信号。DDS的基本原理如图1所示,把一个单位振幅的正弦函数的相位在2π弧度内分成2N个点,求出相应各点的正弦函数值,并用D位二进制数表示,写入ROM中构成一个所谓的正弦表。在高速稳定的参考时钟控制下依次读出每个相位对应的正弦函数值,即得到采样的正弦离散信号,经D/A转换得到需要的模拟信号,改变输入时钟频率即可控制输出信号的频率。

根据DDS的原理分析可知,DDS输出波形频率为fo=Kfc/2N。最低输出频率(K=1)fmin=fc/2N,最高输出频率为fmax=fc/4,其中,fc为累加时钟频率;K为频率控制字;N为累加器位数。

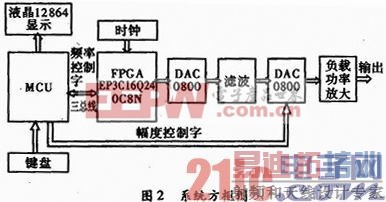

2 系统整体方案设计

系统设计主要由主控制器模块、FPGA模块、D/A转换模块、滤波模块、调幅模块、按键输入模块、功率放大模块及液晶显示模块构成。系统框图如图2所示。采用STC89C51单片机作为系统的主控制器;FPGA模块实现波形数据的存储与输出;D/A转换模块将波形数据转换为模拟量。液晶显示器用于显示波形、幅度、频率等。

3 系统主要硬件电路设计

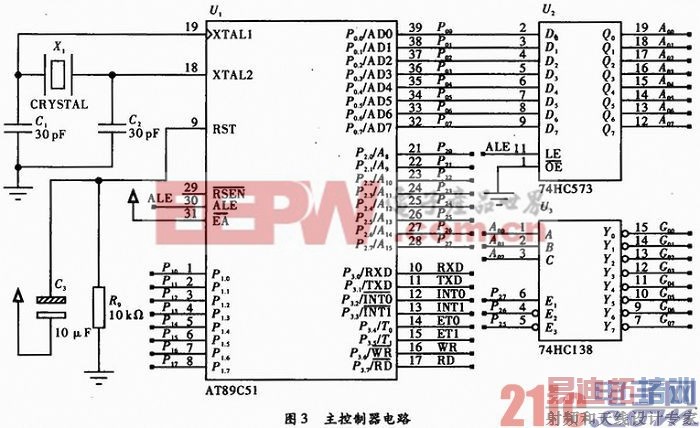

3.1 主控制器电路设计

主控制器采用AT89C51单片机,系统采用总线技术,这样仅占用了单片机的少量接口和IO资源就可以组建起整个系统,使得硬件和软件设计更方便,也利于扩展,具体电路如图3所示。

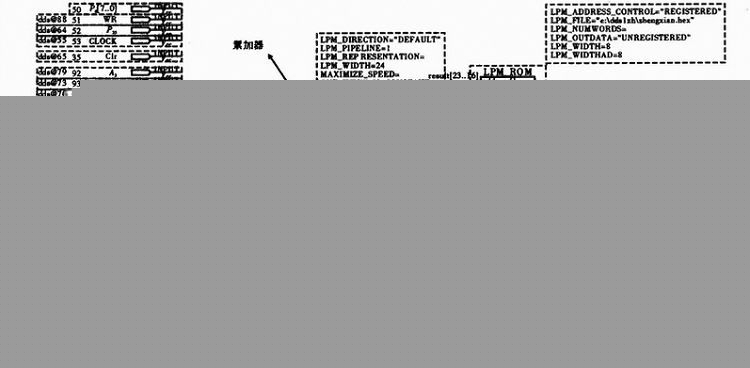

3.2 DDS的FPGA实现电路设计

DDS系统包括相位增量寄存器、相位累加器、地址寄存器、波形存储器、时钟倍频器及地址发生部分等模块,内部所有模块用Verilog语言编写或调用QuartusⅡ中的已有lpm库文件。系统顶层设计用原理图的方式进行模块间的连接,具体电路如图4所示。当改变波形存储器中波形数据时,也就改变了输出波形,可以通过波形选择按钮分别输出正弦波、方波、三角波3种波形。

[p]

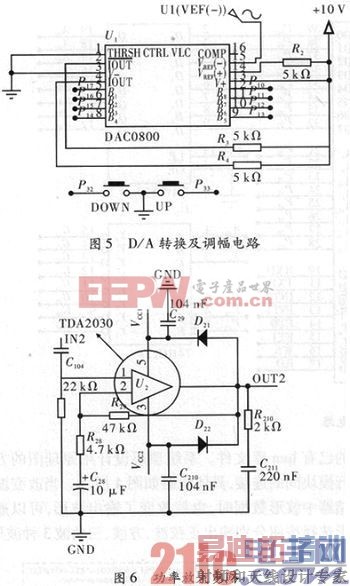

3.3 D/A转换及调幅电路

如图5所示,将波形存储ROM的输出通过D/A转换电路转换为模拟信号,通过算法实现幅度控制并设置独立按键执行微调,再通过滤波电路滤波,即可得到所需的波形。

3.4 功率放大模块

由于输出信号的功率较小,输出有负载时,会有较大失真,带负载能力差,要考虑到功率放大,对输出的信号进行放大。设计中功率放大采用功率放大芯片TDA2030A实现,TDA2030A是意法半导体公司生产的单声道功放IC,该IC体积小巧、输出功率大、静态电流小、动态电流大、负载能力强,既可带动4~16 Ω的负载,某些场合又可带动2 Ω甚至1.6 Ω的低阻负载,且性价比高,具体电路如图6所示。

3.2 DDS的FPGA实现电路设计

DDS系统包括相位增量寄存器、相位累加器、地址寄存器、波形存储器、时钟倍频器及地址发生部分等模块,内部所有模块用Verilog语言编写或调用QuartusⅡ中的已有lpm库文件。系统顶层设计用原理图的方式进行模块间的连接,具体电路如图4所示。当改变波形存储器中波形数据时,也就改变了输出波形,可以通过波形选择按钮分别输出正弦波、方波、三角波3种波形。

3.3 D/A转换及调幅电路

如图5所示,将波形存储ROM的输出通过D/A转换电路转换为模拟信号,通过算法实现幅度控制并设置独立按键执行微调,再通过滤波电路滤波,即可得到所需的波形。

3.4 功率放大模块

由于输出信号的功率较小,输出有负载时,会有较大失真,带负载能力差,要考虑到功率放大,对输出的信号进行放大。设计中功率放大采用功率放大芯片TDA2030A实现,TDA2030A是意法半导体公司生产的单声道功放IC,该IC体积小巧、输出功率大、静态电流小、动态电流大、负载能力强,既可带动4~16 Ω的负载,某些场合又可带动2 Ω甚至1.6 Ω的低阻负载,且性价比高,具体电路如图6所示。

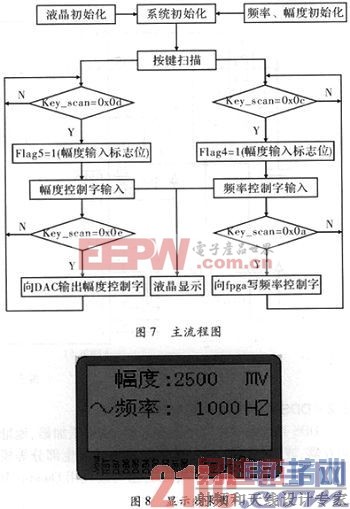

4 软件设计

软件设计采用C语言编写。软件主要由主程序、液晶子程序和按键子程序等组成。软件主流程如图7所示。系统加电后,主程序的功能主要是完成系统初始化,包括液晶、频率幅度等参数的初始化,更新显示数字,循环扫描按键,根据按键输入分别进行频率幅度的设定,通过幅度控制字的设定向DAC输出幅度控制字,通过频率控制字的输入向FPGA写频率控制字,从而达到改变输出波形频率和幅值的目的,并在液晶显示器上显示出来。显示效果如图8所示。

5 结束语

系统采用FPGA实现DDS电路,以AT89C51为主控制器,实现了输出频率范围为1 Hz~10 MHz的正弦波、方波、三角波的信号发生器,并且幅值和频率均可调节,其最小步进频率可达1 Hz。测试结果表明,该设计具有频带宽、精度高、性能稳定、成本低和操作界面友好等特点。用这种方法设计的波形发生器只要改变FPGA中ROM的数据,DDS就可以产生任意波形,提高了设计的灵活性,降低了电路的复杂度,减少了电路设计时间和可能发生的错误,具有较高的性价比。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...