- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于NIOSⅡ的GPS信息接收系统设计与实现

摘要:全球卫星定位系统(CPS)可以时海陆空进行全方位的实时定位与导航,其应用日益广泛,通过GPS定位系统及其信息接收装置可以实现对当前所在位置的确定 系统使用天线接收GPS卫星信号,并在μC/OS操作系统下用NIOS处理器进行分析处理,以保证其实时性,最终输出位置、速度等信息进行定位。本系统通过实验测试验证,定位具有较高的准确性和实时性。

关键词:GPS;卫星定位;NIOS处理器;μC/OS操作系统

0 引言

GPS全球卫星定位系统在天空中是由24颗卫星组成的GPS星座构成,它们特定的排列方式可以使地球上任何地方任何时刻都可以观测到四颗及以上卫星,定位精度高,是现有的卫星定位系统中最常用的技术比较成熟和稳定的定位系统,因此在当今社会GPS的应用十分广泛,涵盖陆地、海洋以及航空航天方面的应用,尤其是车辆导航、航程航线测定、船只实时调度与导航等都可以看成是一个个GPS显示系统。可见,GPS显示系统能为人们的生活和工作带来许多方便,所以GPS信息接收和显示装置的设计开发具有广阔的发展前景。

GPS信息的接收模块技术如今比较成熟,主要可以分为军事和民用的两类。民用的GPS芯片对于精度的要求并不是很高,但基本都能满足人们的实用要求。由于GPS模块接收到的数据无法直接读取,因此需要设计一个合理的信息接收转换及显示系统,将GPS模块接收的定位数据转化为能够直接读取的格式并显示出来。

本文设计的基于NIOS处理器的GPS定位信息显示系统的主要目的是接收GPS定位卫星的定位信息并实现时间、经度、纬度以及速度等信息的实时显示,为人们的日常生活带来便利。

1 系统的原理及整体设计

1.1 系统原理

GPS模块接收GPS定位卫星发射的信号,并在其内部经过一系列的信息处理解析出具有一定格式的、可读性较强的导航电文,其中包含了经纬度和速度等定位信息。系统设计的GPS信息接收系统,主要是基于FPGA完成的,通过Verilog硬件描述语言在FPGA上嵌入NIOSⅡ处理器,并引入μC/OS实时操作系统来优化整个系统的工作,通过C语言编程从GPS模块输出的定位信息中提取经纬度和速度等信息,并利用液晶显示器显示出来。

GPS的输出数据遵循NMEA-0183协议标准,即美国海军的电子设备标准。该协议定义了GPS接收模块输出的标准信息,最常用、兼容性最广的语句格式包括:$GPRMC,$GPGGA,$GPGSV,$GPGSA,$GPGLL等。本设计选用$GPRMC,其数据格式为:

$GPRMC,1>,2>,3>,4>,5>,6>,7>,8>,9>,10>,11>,12>*hh

其中:1>为格林尼治时间;2>为定位状态,A=有效定位;3>为纬度;4>为纬度半球;5>为经度;6>为经度半球;7>为地面速率;8>为地面航向;9>为格林尼治日期。

1.2 系统整体设计

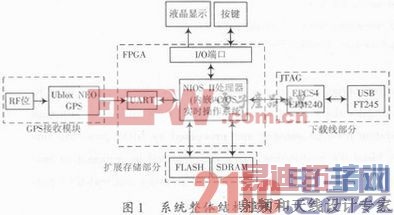

系统总体分为五大部分:GPS接收模块、FPGA及其内部NIOSⅡ处理器部分、扩展存储部分、液晶显示部分及下载线部分。其整体结构框图如图1所示。

(1)GPS接收模块。能够捕获到按一定卫星高度截止角所选择的待测卫星的信号,并跟踪这些卫星的运行,对所接收到的GPS信号进行变换、放大等处理,测出GPS信号从卫星到接收机天线的传输时间,从而解译出GPS所发送的导航电文。此过程完全在现有的GPS模块中完成,本设计只需要了解其输出数据的格式并完成对它的解析即可。

(2)FPGA及其内部NIOSⅡ处理器部分。通过使用Verilog硬件描述语言在FPGA上搭建一个MOSⅡ处理器,并描述出FPGA内部逻辑电路的连接方式,然后在NIOSⅡ处理器中移植入一个μC/OS操作系统,采用C语言编程控制整个系统的工作,对GPS导航电文进行解析并控制液晶显示等。

(3)扩展存储部分。片外的FLASH和SDRAM扩展了系统的容量,可以实现大规模的编程,完成复杂的任务,本设计由于需要操作系统的植入,需要更大的存储空间,因此在FPGA的外围设置了FLASH和SDRAM。

(4)液晶显示部分。FPGA将从GPS模块解析出来的位置、速度等信息送给液晶,由液晶显示器显示出来,并且要保证其能够实时更新。

(5)下载线部分。通过Altera USB Blaster把电脑里编译好的程序下载到FPGA中的NIOSⅡ处理器上,并进行在线调试。

2 系统硬件设计

系统硬件设计根据各部分的功能需求主要包括2个部分:FPGA及其外围电路、GPS模块及液晶显示电路。GPS模块负责接收卫星的定位信息并输出导航电文,FPGA及其嵌入的NIOS处理器是分析和处理导航电文的核心,液晶显示屏则显示可直接读取的定位信息。

2.1 FPCA及其外围电路

FPGA芯片选用Altera公司的CyeloneⅢ系列芯片,该芯片有相应的完善的设计开发平台,方便系统的设计与调试。

FPGA配置采用AS+JTAG方式,这样在调试阶段可以使用JTAG方式,最后当程序调试无误后在使用AS模式把程序烧到配置芯片里去。这样做的一个明显的优点是:在AS模式不能下载的时候,可以利用Quartus自带的工具将配置程序生成.jic文件,用JTAG模式来验证配置芯片是否损坏。通过JTAG将FPGA的配置程序写入到片外配置芯片中,掉电不丢失,每次上电时再将其中的程序读入到FPGA中。另外在FPGA的I/O引脚接入一些LED灯,方便观察测试结果,也可用来检验设计的正确与否。

2.2 GPS接收模块及液晶显示电路

GPS接收模块采用Ublox NEO-6M模块,它是一个现有的GPS接收模块,输出的导航电文格式清晰,便于处理。它将接收到的卫星定位信息在其内部经过简单的处理输出给FPGA的I/O端口,在FPGA内部解析之后又通过另外的I/O端口发送给液晶显示器。液晶显示选用12864液晶显示器,并采用串行数据输入方式,将接收到的数据显示出来。

2.3 供电部分

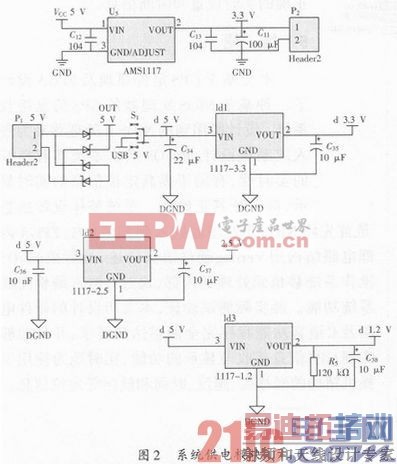

因FPGA各管脚所需输入电压包括3.3 V,2.5 V和1.2 V,12864液晶需要5 V,GPS模块所需电压为3.3 V,因此整个电路板需要多种供电电压,供电电路的设计思想是输入5 V电压,再通过电平转换电路转换出其他所需要的电平。

系统供电模块如图2所示。其中电源与地之间的电容主要作用是去除电源中耦合的其他信号,以减小甚至是消除这些信号对电源的影响。

[p]

3 系统软件设计

FPGA内部使用Quartus内嵌的工具SoPC Builder搭建NIOSⅡ处理器,并用Verilog硬件描述语言来描述FPGA内部电路结构,而μC/OS实时操作系统的植入及系统的控制程序则是由C语言编程完成的。

3.1 FPGA内部逻辑实现

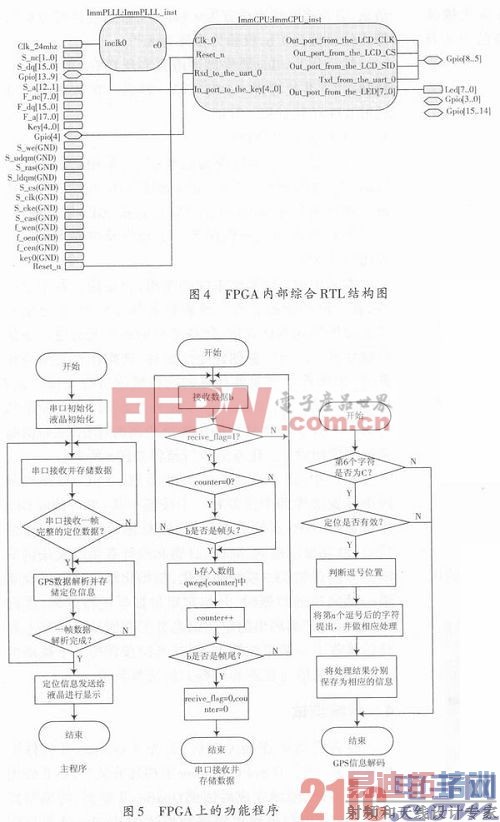

首先构建NIOSⅡ处理器,包括一个CPU和它的内存单元、JTAG和UART部分,如图3所示。

从图3中可以看出NIOS处理器和外围设备及接口的大概结构,各部分通过Avalon总线连接起来,并可以自动分配地址和中断。

根据设计对实时性的需要,其中NIOS软核选择NIOSⅡ/f,它占资源最多,但速度最快,并且功能最多;RS 232串口根据NMEA-0183协议,为了获取GPS定位信息,必须将波特率设置为9 600 b/s,数据位设置为8 b,停止位设置为1 b,校验为设置为无。

然后用Verilog硬件描述语言实现FPGA内部逻辑,包括NIOSⅡ处理器、锁相环等。最后,FPGA内部综合后的RTL结构如图4所示。[p]

3.2 系统功能程序设计

在构建好NIOS处理器的基础上,采用C语言编程将μC/OS实时操作系统移植到处理器中,并编写实现设计功能的程序,如接收CPS定位数据、GPS信息解码、延时和LCD液晶显示程序等。主程序及主要子程序流程图如图5所示。

本文中μC/OS操作系统的使用,即是建立若干个任务,将实现功能的各程序函数放入各任务中,并分别对任务设置不同的优先级,任务之间的通信是通过发送信号量实现。当任务创建完成之后,将操作权交给操作系统,由操作系统对各任务的执行顺序进行安排。μC/OS操作系统可以实现在一个任务挂起时,马上开始执行另一个处于等待状态的优先级最高的任务,从而提高系统的实时性。任务的执行流程如图6所示。

设计中,出于对系统功能的考虑,在μC/OS操作系统中设置这样四个任务和一个按键中断:串口接收GPS定位数据,GPS定位数据解码,液晶显示经纬度和速度信息,液晶显示航向、时间、日期和设计者信以及按键中断。开机首先GPS模块初始化,初始化结束串口接收完第一帧完整的数据时,开始对定位数据进行解码;当解码完成后,把解码出的定位信息显示在液晶显示屏上并开始接收下一帧定位数据;通过五向按键的上下拨动可以实现定位信息在液晶屏幕上的交替显示。

4 系统测试

检查完电路连接无误后,首先在QuartusⅡ软件中建立工程,然后在SoPC Builder中构建好的NIOSⅡ处理器进行编译,编译完成后回到QuartusⅡ界面,将编写好的对FPGA内部电路逻辑进行描述的Verilog语言程序写入到工程里,对其进行编译,结果如图7所示。

从图中可以看出该设计占用的FPGA内部资源。然后将编译生成的FPGA配置文件下载到FPGA片外的EPCS4芯片中,至此,FPGA配置完成,下面开始对软件程序的测试。本设计的软件调试在NIOS IDE软件环境下完成。首先,在NIOS IDE软件环境下新建一个工程,在选择工程模板时可以选择Hello MicroC/OS-Ⅱ,这样在工程建立之时,μC/OS操作系统就已经被嵌入使用,接下来在NIOS IDE工程内输入用C语言编写的功能程序,对工程进行编译,验证程序的正确性。

在分别完成硬件电路和软件程序测试的基础上,将FPGA的硬件配置文件下载到电路中的片外EPCS4芯片中,将软件程序下载到已经构建好的NIOSⅡ处理器中,然后进行总体测试。

连接上GPS天线,程序下载完成并等待一段时间后,天线收到定位数据,系统开始解码并显示定位信息,这时液晶屏上显示第一屏定位信息,即经纬度和速度信息,如图8所示。此时,若按下五向按键的向下键,液晶显示信息翻屏,显示第二屏定位信息,包括航向、时间、

日期和设计者信息。

将五向按键分别向上和向下拨动,液晶屏显示信息可以在第一屏和第二屏之间进行切换。可见系统设计正确,能够提供正确的实时位置和时间信息。

5 结语

本文基于GPS定位原理及FPCA设计了一种基于NIOS处理器的CPS信息接收系统,设计所用到的NlOSⅡ处理器专为嵌入式系统设计,μC/OS操作系统具有良好的实时性,有助于提高定位信息的实时显示,以保证其正确性。系统整体设计思想是首先将NIOSⅡ处理器嵌入到FPGA内,FPGA内部电路结构用Verilog硬件语言描述,然后把μC/OS操作系统移植到处理器内部,通过C语言编程完成系统功能。经实际测试验证,本文所设计的硬件电路及C语言功能程序完全能够达到要求,并且能够实现GPS信息接收与显示的功能,实时地为使用者提供精确的经纬度、速度、时间和航向等定位信息。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:赛灵思借20nm/3D

IC技术抢攻Smarter

Systems商机

下一篇:可将数据转换器IP成功集成到系统芯片的12种设计技