- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的高速加密卡设计与实现

摘要为增强数据信息的安全性,设计了一种基于FPGA的高性能加密卡。该加密卡通过PCI Express总线与主机通信,由FPGA芯片内置的Nios ll软核处理器和PCI—E硬核分别实现控制器模块与通信接口模块功能;采用SM1、RSA算法对数据进行加密或解密。将加密卡的数据通信和算法控制等功能集成在单片FPGA芯片上实现,优化了电路结构、提高了加密卡的稳定性和可靠性。实际测试结果表明,所设计的加密卡功能正确,运算速度快,达到了预期的目标,具有良好的应用前景。

关键词信息安全;FPGA;PCI Express;NiosⅡ软核;加密

计算机网络技术以及各种网络应用的快速发展,在给社会、企业、个人带来便利的同时,也由于目前网络无法有效防止传输信息被第三方非法窃取和修改,而产生信息安全性问题。采用信息加密技术是解决信息安全的有效手段,目前信息加密技术主要分为软件加密和硬件加密。软件加密的优势在于其成本及工艺难度低,而加密速度依赖于计算机的性能,消耗了大量系统资源,且安全性和可靠性差。硬件采用专用加密卡实现,具有较高的安全性和可靠性,是现代信息加密技术的发展方向。加密卡采用的总线技术经历了ISA(Industrial Standard Archit ecture)总线、PCI(Peripheral Component Interconnect)总线和PCI Express(Peripberal Component Interconnect Express,PCI—E),目前的硬件加密卡主要采用PCI总线或PCI Express与DSP(Digital Signal Processing)芯片组合的方式,PCI总线或PCI—E总线负责与上位机通信,DSP芯片作为CPU(Central Processing Unit)。随着计算机总线技术的发展,PCI总线已逐渐被具有更高传输性能的PCI—E总线取代,所以采用PCI总线的加密卡将逐渐被淘汰,采用PCI Express总线的加密卡通过桥接芯片实现PCI—E总线,虽然这种方式面向事务处的接口实现简单,但需要两片单独的芯片,导致加密卡的结构复杂、控制分散、灵活性较差。基于上述因素,本文选用可编程逻辑器件(Field Programmable CateArray,FPGA)设计实现了一款高速率、高可靠性的硬件加密卡,通过FPGA内部资源实现PCI—E总线和CPU功能。

1 加密卡设计

加密卡的基本功能是数据加解密。本文所设计加密卡可实现的主要功能包括:SM1算法、RSA(Rivest-Shamir-Adleman)算法、密钥管理、权限管理、随机数生成等。SM1算法是高性能分组密码算法,具有较高的加解密速率,用于对大量数据进行数据加解密操作;RSA算法是目前较优秀的公钥方案之一,具有较高的安全性,但其加解密速度较慢,主要用于对少量数据进行数字签名操作;密钥管理是保证加密卡安全性的重要组成部分,主要包括密钥的生成、存储、备份和删除等功能;权限管理是为增强加密卡的安全性而设计的一种权限管理机制,只有通过身份认证后的操作命令才能被加密卡接受,以此有效地防止加密卡信息泄露;随机数生成采用专用数字物理噪声源实现,负责产生真随机数序列。

1.1 加密卡硬件结构

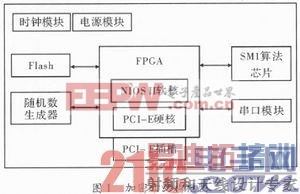

加密卡主要由控制器模块、算法模块、通信接口模块等组成。控制器是加密卡的核心模块,其根据主机发送的命令控制加密卡的整体操作;通信接口模块负责完成加密卡与主机之间的数据通信。设计选用Altera公司的CycloneIV CX系列的EP4CGX30 FPGA芯片,采用FPGA芯片内置的NiosII软核处理器和PCI—E硬核来分别实现控制器模块和通信接口模块功能,分别代替现有加密卡中的DSP芯片和PCI—E桥接芯片,这种实现方式将控制器和通信接口以及其他逻辑功能模块等集成在单片FPGA中,使加密卡的控制集中、结构简单、集成度高,在保证信息安全性的同时,使加密卡具有更高的灵活性和可靠性。图1为所设计的加密卡结构框图。

1.2 FPGA内部电路

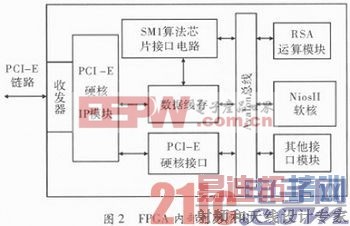

加密卡的主要控制功能被集成在FPGA中实现。其内部主要功能结构框图如图2所示。加密卡所执行的操作由主机发起,具体操作流程:(1)首先PCI—E总线接口获取FPGA内部数据缓存的控制权,通过该接口将主机中的数据存储到FPGA内部的数据缓存中。(2)当数据全部存入数据缓存中后,将数据缓存的控制权交给NiosII软核,NiosII软核读取数据缓存中的数据,然后依据操作命令控制算法模块和各种功能模块进行相应的操作,并将操作结果存储到数据缓存中。(3)当NiosII软核控制操作完成后,释放数据缓存的控制权并启动PCI—E总线接口,NiosII软核等待接受下一次的操作命令。(4)PCI—E总线接口将数据发送给主机,完成加密卡的一个操作流程。

1.2.1 PCI—E总线接口

PCI—E总线是新一代总线标准,采用了目前业内流行的点对点的串行连接,具有较高的传输速率。PCI—E总线1.x版和2.x版的单通道速率分别为2.5 Gbit·s-1和5 Gbit·s-1,均采用8 b/10 b编码,最新的PCI—E总线3.0版兼容1.x版和2.x版,同时可采用128 b/130 b编码,单通道速率可达8 Gbit·s-1。虽然PCI—E总线在传输速率方面具有突出的优势,但是其体系结构复杂,设计难度大。

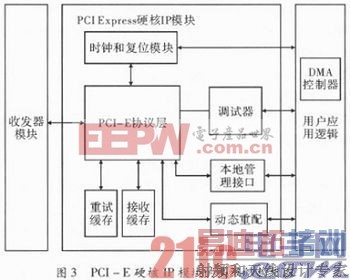

设计选用的FPGA芯片,其内置收发器是可独立操作的全双工高速收发器,支持8 b/10 b编码,单通道最大速率为2.5 Gbit·s-1,能够满足PCI—E总线的速率要求;其内置的PCI—E硬核占用较少的FPGA资源,能够实现PCI—E总线物理层、数据链路层以及传输层的功能,支持根端口与端点配置和x1、x2、x4通道模式,符合PCI—E 1.1基本规范协议和电气特性要求,可通过Avalon总线与FPGA内部的其他模块互联,是一个完整的PCI—E协议解决方案。图3为PCI—E硬核IP(Intellectual Property)模块的高级结构框图,内部包含2 kB的重试缓存和4 kB的接收缓存。本次PCI—E总线接口采用PCI—E硬核的x1通道、端点配置模式和DMA读写方式,DAM读写方式不需要主机中的CPU参与,使PCI—E总线接口可以直接和主机中的内存进行数据交互,适合大批量的数据传输。DMA读写方式通过Altera公司提供的SOPCBuilder工具中的DMA控制器实现,并且通过该工具实现PCI—E硬核、高速收发器和DMA控制器的级联组成PCI—E总线接口。

主机向PCI—E总线接口发送数据的过程:(1)主机向加密卡发送数据时,首先将其内存起始地址、硬件存储器地址、数据长度等信息写入PCI—E总线接口的寄存器中。(2)PCI—E总线接口检测到寄存器中的信息后,向主机发送读请求。(3)主机接收到这些读请求后,将数据从内存中取出,组包后发送给FPGA。(4)PCI—E总线接口将接收到的数据包转换成自定义的数据格式,存储到数据缓存中。(5)当主机将待发送的数据发送完毕后,给PCI—E总线接口发送一个中断信号,告知此次数据传输完成,至此完成主机向PCI—E总线接口发送数据的操作。[p]

PCI—E总线接口向主机发送数据的过程:(1)PCI—E总线接口检测到由FPGA内部发送的启动PCI—E总线接口信号后,首先向主机发送中断信号,然后将数据缓存的数据组包后发送给主机。(2)主机接收到PCI—E总线接口的中断信号后,将PCI—E总线接口发送来的数据存入内存中。(3)PCI—E总线接口发送完数据后再次向主机发送中断信号,至此PCI—E总线接口向主机发送数据操作完成。

1.2.2 NiosII软核设计

NiosII软核处理器是Altera公司推出的第二代集成在FPGA内部的可配置的32位RSIC(Reduced InstructionSet Computer)嵌入式处理器,具有经济型、标准型和快速型3种,占用少量的FPGA资源,其中快速性NiosII软核性能较高,速度较快,可获得超过250DMIPS(Dhrystone Million Instructions executed Per Second)的性能。为使加密卡达到最快的运算速度,本次选用快速型NiosII软核处理器作为CPU,其通过Avalon总线与SM1算法芯片接口电路、数据缓存、PCI—E硬核接口以及其他接口模块等互联,共同组成硬件结构。基于NiosII的软核处理器采用C语言进行加密卡软件部分设计,软件主要功能是根据主机发送的命令控制加密卡完成数据加解密、密钥管理、权限管理和随机数生成等操作。同时通过NiosII软核指令与自定义硬件模块相结合,以软硬件协同的方式完成RSA算法电路的设计。

1.2.3 RSA算法设计

加密卡中的RSA算法操作主要包括密钥生成、密钥存储和加解密。到目前为止,密钥长度为1 024位的RSA算法已经无法保证加密数据的安全性,因此本次加密卡中的RSA算法采用2 048位的密钥。RSA算法操作中的密钥生成和密钥存储部分需要生成随机数,并对大量数据进行存储和转换,用硬件实现难度大,且效率不高,所以本次采用基于NiosII软核的软件方式实现该部分操作。RSA算法中的加解密操作需要对大位数的数据进行模幂运算,运算复杂,虽已有成熟的软件实现方式,但是该种方法实现的RSA算法运算速度慢,无法满足设计要求,而硬件实现方式已有成熟的算法,运算速度快,所以本次RSA算法的加解密部分采用硬件方式实现,通过NiosII软核控制RSA运算模块完成加解密操作。

模幂运算是RSA加解密的核心,可以通过模乘运算来实现,本次采用蒙哥马利算法实现模乘运算,该算法利用移位和加法代替了复杂的乘、模操作,易于在硬件上实现。NiosII软核中定制的RSA加解密运算指令的输入为密钥、数据长度和启动信号,输出为运算完成信号。当NiosII软核接收到RSA运算命令后,通过定制的模幂运算指令向RSA运算模块写入密钥和数据长度信号,然后启动该运算模块,RSA运算模块接收到Nios II软核的启动信号后,从数据缓存读取待运算数据进行加解密运算,运算完成后将运算结果存入数据缓存中,并向NiosII软核发送完成信号,NiosII软核接收到RSA运算完成信号后启动PCI—E总线接口,将运算结果发送给主机。这样采用软硬件结合的方式实现RSA加解密功能,不但能够保证RSA运算的正确性,降低RSA算法实现的复杂度,而且比采用纯软件实现方式提高了运算速度。

1.2.4 SM1接口电路设计

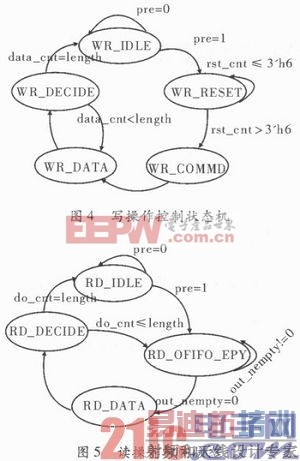

在FPGA内设计有一个专用SM1算法芯片的接口控制电路,用于控制SM1算法芯片实现数据的加解密操作。SM1算法芯片采用双总线命令和组包操作方式,具有较高的运算速率。所以接口电路主要由写状态机和读状态机组成,分别控制对SM1算法芯片进行写数据操作和读运算结果操作。接口电路的工作原理:加密卡上电后,首先对SM1算法芯片进行硬件复位,然后检查由NiosII软核发送的SM1算法启动信号,若该信号有效,则同时启动写状态机和读状态机,这样能够在进行写数据操作时,也读取运算结果值,从而提高SM1算法命令的执行速率。图4和图5分别为写操作状态机和读操作状态机的设计。

2 设计实现

设计采用NiosII Eclipse开发软件完成加密卡软件程序设计,采用QuaxtusII 11.0工具软件完成加密卡硬件电路设计,并对所设计的软硬件进行了整合和仿真验证。在验证设计的正确性后,完成了对FPGA内部整体电路的布局及综合,并制作成加密卡样品。在Windows系统下对所设计的加密卡连续测试168 h,加密卡工作正确;和已有的基于DSP和PCI—E桥接芯片设计的加密卡进行测试比较,结果如表1所示,本次设计的加密卡能够正确地完成各项功能,同时RSA算法的运算速度为5.9次/s,SM1运算速度为295 Mbit·s-1,较已有加密卡RSA运算的3.5次/s和SM1运算的240 Mbit·s-1有了大幅提高,所以本次加密卡在保证可靠性的同时,运算速度更快。

3 结束语

基于增强信息安全的思想,设计了一种基于FPGA的低成本、高性能的加密卡。采用FPGA内部资源实现了加密卡的控制器模块、算法模块、通信接口模块和各种接口等主要功能。并对两种不同结构设计方式的加密卡进行了性能比较测试,结果表明采用FPGA单芯片结构设计方式的加密卡功能正确,电路板结构简单,可靠性强并且具有更高的灵活性和运算速度,达到了预期的目标。目前所设计的加密卡只集成了SM1和RSA算法,今后根据需要,可在FPGA内部通过扩展硬件或软件的方式来增加其它的加密算法功能,所以,该加密卡实用性强,具有可扩展性,在信息安全领域具有良好的发展前景。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...