- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

FPGA设计开发软件ISE使用之: 片上逻辑分析仪(ChipScope Pro)使用技巧

6.7 片上逻辑分析仪(ChipScope Pro)使用技巧

在FPGA的调试阶段,传统的方法在设计FPGA的PCB板时,保留一定数量的FPGA管脚作为测试管脚。在调试的时候将要测试的信号引到测试管脚,用逻辑分析仪观察内部信号。

这种方法存在很多弊端:一是逻辑分析仪价格高昂,每个公司拥有的数量有限,在研发期间往往供不应求,影响进度;二是PCB布线后测试脚的数量就确定了,不能灵活地增加,当测试脚不够用时会影响测试,测试管脚太多又影响PCB布局布线。

ChipScope Pro是ISE下一款功能强大的在线调试工具。面对这些问题,ChipScope Pro都可以有效地解决。

6.7.1 ChipScope Pro概述

ChipScope Pro是针对Xilinx Virtex-II pro/ Virtex/ Virtex-II/ Virtex-EM/ Spartan-IIE/ Spartan-IIE 系列FPGA的在线片内信号分析工具。它的主要功能是通过JTAG口,在线实时读取FPGA的内部信号。

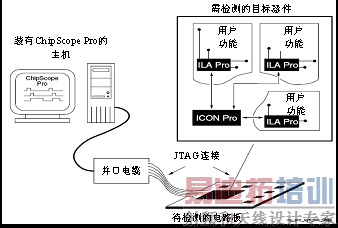

ChipScope Pro的基本原理是利用FPGA中未使用的BlockRam,根据用户设定的触发条件将信号实时地保存到这些BlockRam中,然后通过JTAG口传送到计算机,最后在计算机屏幕上显示出时序波形。ChipScope Pro应用的框图如图6.34所示。

图6.34 ChipScope Pro应用框图

其中ILA、ICON是为了使用ChipScope Pro观察信号而插入的核。ChipScope Pro工作时一般需要用户设计中实例化两种核:一是集成逻辑分析仪核(ILA core,Integrate Logic Analyzer core),该核主要用于提供触发和捕获的功能;二是集成控制核(ICON core,Integrated Contorller core),负责ILA core和边界扫描端口(JTAG)的通信。

一个ICON core可以连接1~15个ILA core。ChipScope Pro工作时,ILA core根据用户设置的触发条件捕获数据,然后在ICON core控制下,通过边界扫描端口上传到计算机,最后用ChipScope Pro Analyzer显示信号波形。

6.7.2 ChipScope Pro设计流程

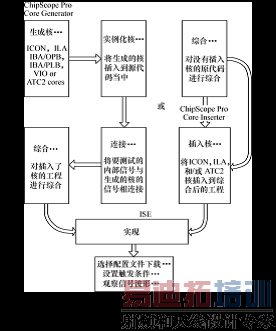

ChipScope Pro工具箱中包含了3个工具:ChipScope Pro Core Generator、ChipScope Pro Core Inserter、ChipScope Pro Analyzer,使用ChipScope Pro在线调试工具的FPGA设计流程如图6.35所示。

由上述流程可知,ChipScope Pro有两种使用方法。

第一种是由ChipScope Pro Core Generator根据设定条件生成在线逻辑分析仪IP核,包括ICON core、ILA core、ILA/ATC core和IBA/OPB core等,之后设计人员在原HDL代码中实例化这些核,然后进行综合、布局布线、下载配置文件,就可以利用ChipScope Pro Analyzer设定的触发条件,观察信号波形。

第二种是原代码完成综合后,由ChipScope Core Inserter工具插入ICON core和ILA core等核,它能自动完成在设计网表中插入这些核的工作,而不用手动在HDL代码中实例化这些核,在实际中应用的比较多,也是推荐大家使用的方法。下面就重点介绍ChipScope Pro Core Inserter和ChipScope Pro Analyzer的使用,这里以ChipScope Pro 8.2i为例来介绍。

[p]6.7.3 ChipScope Pro Core Inserter简介

ChipScope Pro Core Inserter的启动有两种方式。

(1)直接在Windows环境下运行“开始”/“程序”/“ChipScope Pro 8.2i”/“ChipScope Pro Core Inserter”命令。运行后即可得到ChipScope Pro Core Inserter的用户界面,如图6.36所示。

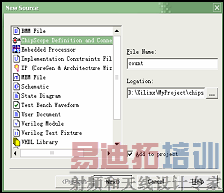

(2)可以通过新建资源的方法,如图6.37所示。

新建ChipScope Pro Inserter资源后,系统自动生成扩展名为cdc的文件。如图6.38所示,双击扩展名为cdc的文件即可启动ChipScope Pro Inserter界面。需要注意的是,在双击扩展名为cdc的文件时,系统会先对该工程文件进行综合。综合完成后才会启动ChipScope Pro Inserter。

图6.36 ChipScope Pro Core Inserter用户界面

图6.37 新建ChipScope Pro Inserter资源对话框 图6.38 新建ChipScope Pro Core Inserter资源后的界面

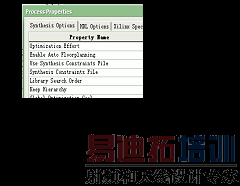

这里在综合前必须先对综合属性进行设置,如图6.39所示,在综合属性对话框中对“synthesis options”/“keep Hierarchy”选项进行设置。设置“keep Hierarchy”为“Yes”或“Soft”。

双击扩展名为cdc的文件,系统完成综合后,会自动启动ChipScope Pro Core Inserter。设计者通过ChipScope Pro Core Inserter对触发单元个数、触发宽度、触发条件、存储深度、采样时刻等参数进行设置。设置完毕后,在ISE下完成布局布线,下载配制文件,即可用ChipScope Pro Analyzer进行观测。

下面对ChipScope Pro Core Inserter的各项设置做详细的说明。

1.用户界面

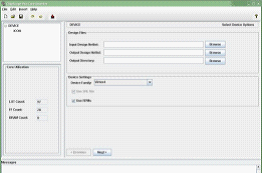

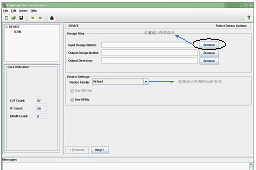

启动ChipScope Pro Core Inserter后,显示如图6.40所示的界面。在“Input Design Netlist”文本框中设置输入设计网表的路径。设置好后,“Output Design Netlist”和“Output Directory”会自动生成,设计者也可自己指定。

图6.40 ChipScope Pro Core Inserter用户界面

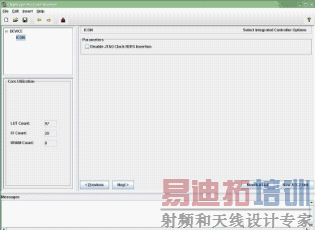

如果是通过新建资源的方法启动ChipScope Pro Core Inserter,这几项显示为灰色,无需设计者设置,系统会自动找到设计网表文件。在“Device Family”下拉列表中选取设计所用的FPGA后,就可单击“Next”按扭,进入“Select Integrated Controller Options”对话框,如图6.41所示。

图6.41 “Select Integrated Controller Options”对话框

2.“Select Integrated Controller Options”对话框设置

在如图6.40所示的“Select Device Options”对话框中,可以指定是否禁止在JTAG时钟上插入BUFG。如果选中此项,JTAG时钟将使用普通布线资源,而不是全局时钟布线。这样会在JTAG时钟线上产生较大的布线延时。因此在全局时钟资源足够用的情况下,应该尽量使JTAG时钟使用BUFG资源。即使由于全局时钟资源不够而不得不禁用BUFG时,也最好附加相应约束,使延迟抖动尽量小。推荐设计者在使用时不选此项。

单击“Next”按钮,进入“Select Integrated Logic Analyzer Options”对话框,如图6.42所示。

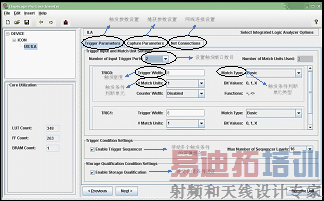

图6.42 “Select Integrated Logic Analyzer Options”ILA对话框

3.“Select Integrated Logic Analyzer Options”对话框设置

如图6.42所示,可以看到在“Select Integrated Logic Analyzer Options”ILA对话框下有3个选项卡,可对触发参数、捕获参数、网线连接进行设置。

“Trigger Parameters”选项卡可对触发端口数目,每个触发端口的宽度、触发条件判断单元、触发条件判断单元的个数和类型等进行设置。

(1)触发端口数目。

在设计中可以根据需要设置多个触发端口,每个ILA Core最多可以有16个输入触发端口,每个触发端口下又可设置多个触发条件判断单元,但各个触发端口包含的触发条件判断单元数量之和不能大于16。

(2)触发端口设置。

一个完整的触发端口设置包括:触发宽度、触发条件判断单元个数及类型的设置。触发宽度是指触发端口包含信号线的个数。通过触发条件判断单元进行判断,当信号线上的信号满足设定的条件时,ChipScope Pro就可将其捕获并存储在BlockRam中,用于在ChipScope Pro Analyzer中显示波形。

对触发条件可以设置个数和类型。当有多个触发条件时,可以将触发条件设置为几个触发条件的逻辑组合。触发条件判断单元实际为比较器,其类型可以有以下几种,如表6.4所示。

[p]表6.4 触发条件判断单元的类型

类 型数值类型匹 配 功 能Bit/Slice说 明

Basic0、1、X=、<>8用于一般信号比较,是一种节约资源的类型

Basic(w/trans)0、1、X、R、F、B=、<>、transition detection4用于控制信号的比较,可以检测跳变的发生

Extend0、1、X=、<>、>、>=、<、<=2当主要考虑数据的大小时,用于地址或数据信号大小的比较

Extend(w/trans)0、1、X、R、F、B=、<>、>、>=、<、<=、transition detection2当数据和地址信号的大小和跳变都需要考虑时,可以用于检测跳变的发生

Range0、1、X=、<>、>、>=、<、<=、in range、not in range1当数据和地址的大小需要考虑时,可以用于检测数值是否在一定范围内

Range(w/trans)0、1、X、R、F、B=、<>、>、>=、<、<=、in range、not in range、transition detection1当数据和地址的大小和跳变都需要考虑时,可以用于检测跳变和数值是否在一定范围内

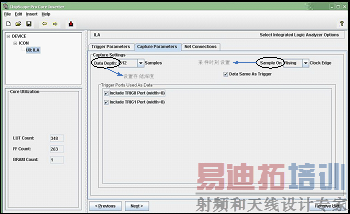

“Capture Parameters”选项卡可以对存储深度、采样时刻等参数进行设置,如图6.43所示。

图6.43 “Capture Parameters”选项卡设置

所谓存储深度,是指在满足触发条件后,要存储多少数据,用于最终的波形显示。ChipScope Pro可能的最大存储深度为16384,最大数据位宽为256bit。实际的数据存储深度和位数由FPGA内部剩余的BlockRam的数量决定。

对于“Data Same As Trigger”选项,有时要观测的信号就是设置的触发条件中的信号,此时选中此项即可。有时设定了触发条件后,想观察别的数据信号,这时可以不选中此项,数据与触发信号完全独立。

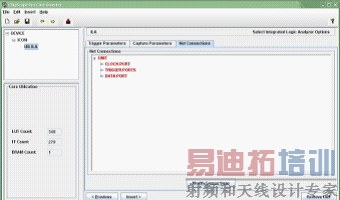

“Net Connections”选项卡可以设置触发端口信号线与要观测的信号的连接,要观测哪些信号,就将这些信号与端口的信号线连接即可,如图6.44所示。

图6.44 “Net Connections”选项卡设置

设置的连接信号可以分为3类:时钟信号(CLOCK PORT)、触发端口信号(TRIGGER PORTS)和数据信号(DATA PORT)。单击“Modify Connections”按钮会出现如图6.40所示对话框。

图6.45 网线连接对话框

设置完所有信号后,端口名字会变为黑色,否则为红色。设置完上述各项后,单击“Inserter”按钮,逻辑分析仪的网表就插入到原来的设计网表当中。之后在ISE下完成布局布线并下载后,就可以用ChipScope Pro Analyzer进行观测了。

6.7.4 ChipScope Pro Analyzer简介

将逻辑分析的核插入设计当中后,就可以运行ChipScope Pro Analyzer进行观测了,ChipScope Pro Analyzer的启动方式有两种。

(1)直接运行“开始”/“程序”/“ChipScope Pro 8.2i”/“ChipScope Pro Analyzer”。

(2)在ISE下启动。

如图6.46所示,双击“Analyze Design Using ChipScope”即可启动,ChipScope Pro Analyzer界面如图6.47所示。

图6.46 从ISE中直接启动ChipScope Pro Analyzer

图6.47 ChipScope Pro Analyzer用户界面

ChipScope Pro Analyzer使用步骤如下。

1.单击![]() 图标,打开JTAG并口连接电缆

图标,打开JTAG并口连接电缆

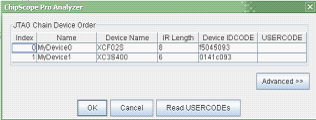

在此之前要保证已将JTAG与器件连接好,如果连接无误,会出现如图6.48所示的对话框。

对话框中会显示JTAG连接的FPGA类型和所用的配置器件类型,这里使用的FPGA为Spartan 3系列,配置器件选用的是XCF02S。

图6.48 JTAG正常连接后提示

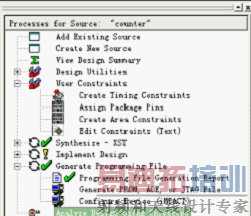

2.下载配置文件

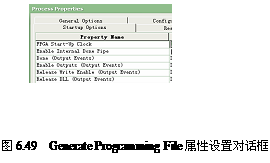

在ISE下完布局布线后,生成配置文件*.bit文件。注意:ChipScope Pro采用JTAG方式观测FPGA内部信号,这就要求在生成下载文件时。在“Generate Programming File”的属性对话框(如图6.49所示)中设置“Startup Options”/“FPGA Start-Up Clock”为JTAG Clock,否则ChipScope Pro将无法正确配置器件。

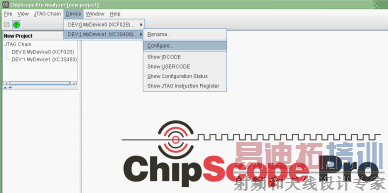

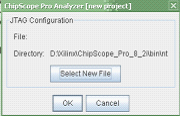

下载配置文件时,选择“Device”/“DEV1”/“Configure”选项,如图6.50所示。单击后会出现如图6.51所示的对话框,选择要下载的*.bit文件,对FPGA进行配置。

图6.50 配置FPGA

图6.51 选择配置文件对话框

3.设置触发条件

成功完成对FPGA的配置后,会出现如图6.52所示界面。

图6.52 成功完成配置后用户界面

如图6.52所示,ChipScope Pro Analyzer的界面由两部分组成。

左边一栏为工程视窗和信号列表。工程视窗的下拉列表中有“Trigger Setup”、“Waveform”选项。双击后,就会有相应的视窗在右边显示。信号列表中列出了所有信号,在这里可以增加或删除视图中的信号,对信号重命名,也可以将信号组合为总线以便于观察。

[p]右边一栏主要有两个视窗:一个为“Trigger Setup”,用于设置触发条件;一个为“Waveform”用于观察波形。设置触发条件包括设置触发条件函数(Match)、触发条件(Trig)和捕获参数(Capture),下面分别介绍。

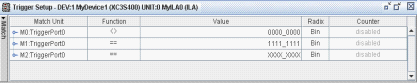

(1)“Match”选项卡。

主要完成触发条件函数的设置。所谓触发条件函数是与表6.4中的匹配功能相对应的。要设置数值大小和函数,即选择:=、<>、>、>=、<、<=某数值时,才满足触发条件。当有多个条件时,可以分别设置每个条件的要求满足的函数和数值,如图6.53所示。

图6.53 “Match”选项卡设置对话框

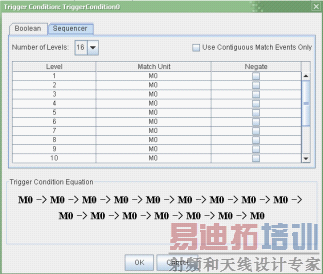

(2)“Trig”选项卡。

主要用于设置触发条件。在“Match”下设置了触发所需要满足的条件。当有多个条件时这里可以设置是让哪一个条件起作用,也可以将条件设置为几个条件的逻辑组合。或者是将几个条件设置为“条件链”,即当依次满足条件链设置的各个条件后,才可以捕获数据,如图6.54所示。

图6.54 “Trig”选项卡设置对话框

如图6.54所示,单击“Trigger Condition Equation”下的选项,会弹出如图6.55所示的对话框。在对话框中,有两个选项卡。在“Boolean”选项卡下,可以设置哪一个条件起作用,也可将条件设置为几个条件的逻辑组合;在“Sequencer”选项卡下,可以设置条件链,如图6.55所示。当依次满足条件链下的几个条件后,就被触发。

图6.55 “Sequencer”选项卡设置对话框

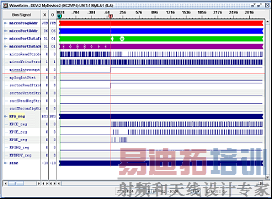

4.观测波形

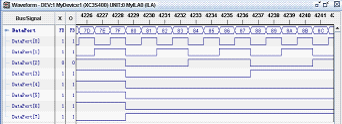

触发条件设置好后,单击左上角的![]() 按钮开始执行。当满足触发条后,ChipScope Pro开始采集数据,采集到一定数目后(该数目取决于存储深度),就可以观察波形了。如图6.56为ChipScope Pro显示波形的效果图。

按钮开始执行。当满足触发条后,ChipScope Pro开始采集数据,采集到一定数目后(该数目取决于存储深度),就可以观察波形了。如图6.56为ChipScope Pro显示波形的效果图。

在波形显示窗口下可对波形进行放大![]() 和缩小

和缩小![]() ,也可以进行局部放缩

,也可以进行局部放缩![]() 。当要观察总

。当要观察总

图6.56 ChipScope Pro波形显示效果图

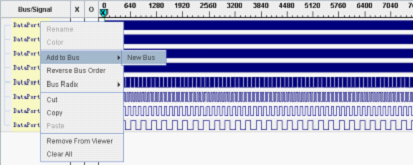

线数据时,可以先选中所有总线数据,然后单击右键,选择“Add to Bus”/“New Bus”即可,如图6.57所示。

图6.57 组合总线数据

添加成功后,就可以在新生成的bus下看到总线数据。如图6.58所示,图中DataPort为新生成的总线,设计者可以根据需要修改总线的名称。

图6.58 总线数据生成结果

6.7.5 小结

本节对在线逻辑分析工具ChipScope Pro作了详细介绍。通过本节的学习,读者应该掌握ChipScope Pro的设计流程以及使用方法。

ChipScope Pro本身的功能很强大,在调试阶段应用很广泛。它可以观察FPGA内部的任何信号,使用也比较简单,希望读者能够很好地掌握。

为了让读者能够尽快地熟悉这一工具的使用,在6.8节给出一个简单的实例,分别应用两种设计流程来完成,读者可参照这一例程来进一步熟悉ChipScope Pro的使用。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:FPGA设计开发软件ISE使用之:

典型实例-增量式设计演示

下一篇:FPGA设计开发软件ISE使用之:

增量式设计(Incremental

Design)技巧