- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA应用于倍频电路的预置可逆分频器设计

摘要:首先分析了应用于倍频电路的预置可逆分频器的工作原理,推导了触发器的驱动函数。

并建立了基于simulink 和FPGA 的分频器模型,实验结果表明分频器可以实现预置模和可逆分频功能,满足倍频电路需要。

1. 前言

锁相环是倍频电路的主要实现方式,直接决定倍频的成败。传统的锁相环各个部件都是由模拟电路实现的,随着数字技术的发展,全数字锁相环逐步发展起来,全数字锁相环的环路部件全部数字化,通常由数字鉴相器、数字环路滤波器、压控振荡器以及分频器组成,全数字锁相环中的分频器要求模可预置且可根据实际需要进行可逆分频[2]。由于现有的电路均不能满足上述要求,本文首先采用simuink 和FPGA 开发了应用于倍频电路的变模可逆分频器。

2. 变模可逆分频器的工作原理

变模分频器的基本原理是设置一个符合函数,在分频过程中,触发器的输出与预置模比较,当触发器的输出与预置模一致时,则给出符合信号,强迫计数器进入所希望的状态,即初始状态,随后计数器则按照卡诺图确定的程序继续工作,直到最后一个状态,即由地址码确定的第N-1 个状态,再强迫分频器回到初始状态[3]。所以每个触发器应当受到两个控制函数的控制,即:

f—正常的由卡诺图得到的控制函数;

F—强迫分频器进入的希望状态;

T—符合函数;

当符合函数T = 1时,F 不起作用,P = f ,分频器按正常程序分频;当T = 0,F 起作用,P = F ,强迫分频器跳变到所希望的状态。

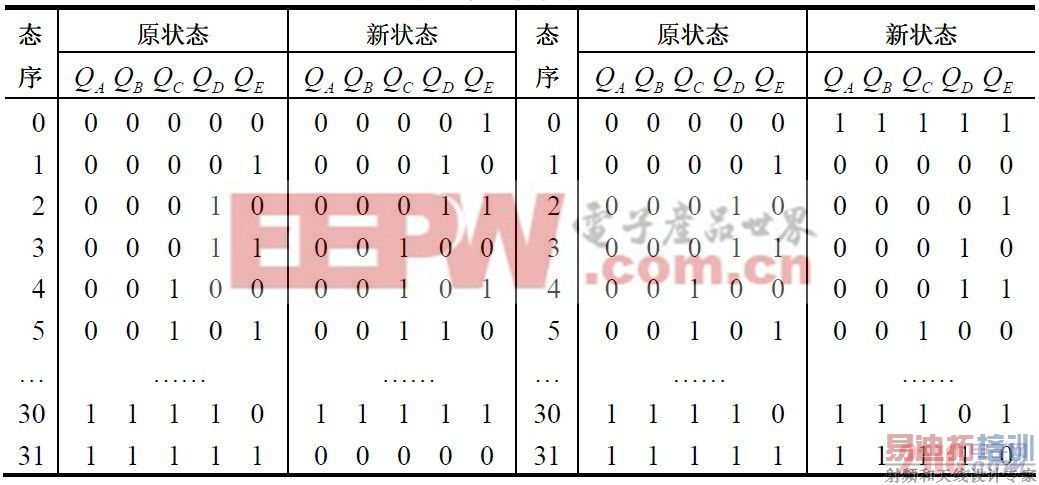

表1 状态转换表

(注:表1 为状态转换图,其中左半部分为递增分频器状态转换表,右半部分为递减状态转换表。表2 为计数值与各触发器当前值的关系。)

[p]

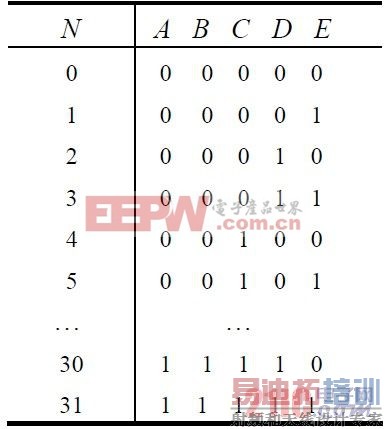

表2 计数值与各触发器当前值的关系

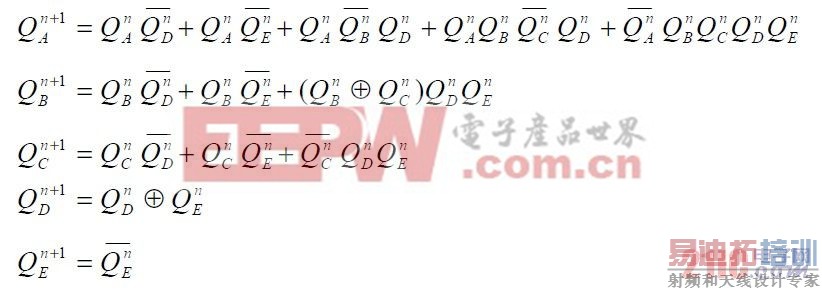

加法分频器的驱动方程为:

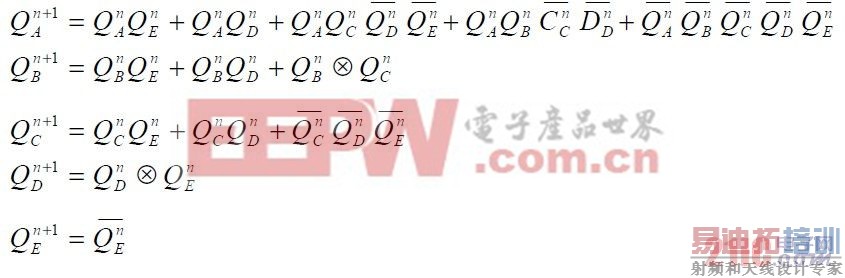

减法分频器的驱动方程为:

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:NGB中间件标准因素简析

下一篇:在PowerPCB中加泪滴操作的方法