- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

简述DDS原理及其基于FPGA的实现

DDS同 DSP(数字信号处理)一样,是一项关键的数字化技术。DDS是直接数字式频率合成器(Direct Digital Synthesizer)的英文缩写。与传统的频率合成器相比,DDS具有低成本、低功耗、高分辨率和快速转换时间等优点,广泛使用在电信与电子仪器领域,是实现设备全数字化的一个关键技术。在各行各业的测试应用中,信号源扮演着极为重要的作用。但信号源具有许多不同的类型,不同类型的信号源在功能和特性上各不相同,分别适用于许多不同的应用。目前,最常见的信号源类型包括任意波形发生器,函数发生器,RF信号源,以及基本的模拟输出模块。信号源中采用DDS技术在当前的测试测量行业已经逐渐称为一种主流的做法。利用它来设计符合自己需要的DDS电路是一个很好的解决方法。

1 DDS的基本原理

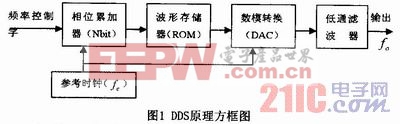

DDS的主要思想是从相位的概念出发合成所需要的波形,其结构由相位累加器、波形存储器、数模转换器、低通滤波器和参考时钟五部分组成,其基本原理框图如图1所示。

综上所述,在采样频率一定的情况下,可以通过控制频率控制字K来控制所得离散序列的频率,经保持、滤波之后可唯一地恢复出此频率的模拟信号。

[p]

2 基于FPGA技术实现DDS的方案

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。FPGA一般来说比ASIC(专用集成芯片)的速度要慢,无法完成复杂的设计,而且消耗更多的电能。但是他们也有很多的优点比如可以快速成品,可以被修改来改正程序中的错误和更便宜的造价。厂商也可能会提供便宜的但是编辑能力差的FPGA.因为这些芯片有比较差的可编辑能力,所以这些设计的开发是在普通的FPGA上完成的,然后将设计转移到一个类似于ASIC的芯片上。另外一种方法是用CPLD(复杂可编程逻辑器件备)。

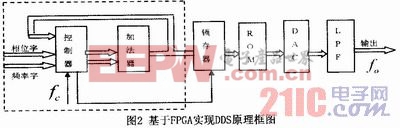

用FPGA实现DDS的基本工作过程为:通过VXI接口电路将生成的数据存入固定数据RAM中,然后用FPGA设计的相位累加器来计算并选择RAM中的数据存放地址,最后将数据给定的频率控制字输出,经DAC转换即实现了任意波形输出。原理图如图2所示。虚线部分可用FPGA来实现。

图2中参考时钟由高稳定的晶体振荡器产生,主要用于控制DDS中各器件同步工作。虚线部分相当于相位累加器,它由N位加法器与N位相位寄存器构成,它实际上是一个计数器。每来一个时钟脉冲,加法器将相位增量数据与相位寄存器输出的累积相位数据相加,把相加后的结果送至相位寄存器的数据输入端。相位寄存器将加法器在上一个时钟作用后所产生的新相位数据反馈到加法器的输入端,以使加法器在下一个时钟的作用下继续与频率控制字相加。由此看来,相位累加器在每一个时钟脉冲输入时,把频率控制字累加一次,相位累加器输出的数据就是合成信号的相位,相位累加器的溢出频率就是DDS输出的信号频率。

3 结束语

采用FPGA设计DDS电路,充分发挥了FPGA在系统可编程的优点,可以通过软件灵活改变相关参数,给设计带来很多方便。用FPGA设计DDS电路较采用专用DDS芯片更为灵活,只要改变FPGA中的ROM数据,DDS就可以产生所需波形数据,并且FPGA的功能完全取决于设计需要,因而具有相当大的灵活性,将DDS设计嵌入到FPGA芯片所构成的系统中,其系统成本并不会增加多少,因此,采用FPGA来设计DDS系统具有很高的性价比。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:基于VHDL

+FPGA

的自动售货机控制模块的设计与实现

下一篇:基于FPGA与RS422的MⅢ总线转换板的设计与实现