- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的水声信号采样存储系统设计

摘要:为了提高水声传感器网络通信系统试验和算法研究的效率,水声传感器网络节点需要具有水声通信的原始波形数据的记录功能。本文设计了一种水声信号采样存储系统,实现了数据变速率AD采集、数据环形存储、数据连续读取、数据飞读等功能。该系统具有结构清晰,集成度高,工作可靠等优点,可以有效提高水声传感器网络试验的效率。

1 引言

近几十年来,随着世界各国对海洋开发和利用步伐的加快,对海洋信息进行连续实时监 测的意义越来越重要。水声无线传感器网络(Underwater AcouSTic sensor network,简称 UW-ASN)是海洋环境立体监测系统中的研究热点,它由大量具有计算和通信能力的传感器 节点组成,各节点被分布在指定的海域,执行连续的协同监测任务。鉴于水声信道的带宽有 限、海洋噪声复杂、具有多途效应和多普勒效应[1],这些特殊性给UW-ASN 中的水声通信、 协议设计等方面带来了很大的挑战,增加了传感器网络设计的复杂性。

为了充分了解水声通信过程中的数据变化,方便对于信道特性分析以及通信方式的选 择,以及大量传感器网络节点之间通信数据的存储,传感器节点必须具备数据采集功能。传 统的水声数据采集存储系统主要由数据采集板卡组成,能够满足数据采集功能,缺点是体积 大,便携性差,难以作为传感器节点的组成部分应用于实际设计中。

本文针对这一问题,提出了基于SOPC(System ON Programmable Chip)的设计方案[2],利 用其配置灵活、扩展性强、接口丰富等优点,以Altera 公司的Cyclone II 系列FPGA 为基 础,设计传感器节点数据采集存储系统,降低了设计的风险,完善了传感器节点功能要求。

2 采样存储系统概述

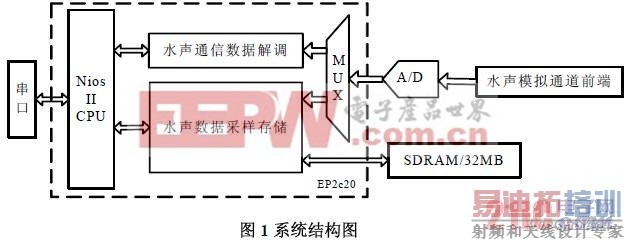

本设计系统的结构如图1 所示,在整个传感器节点的系统当中,将AD 芯片输出的12 位数据,通过设计SDRAM 控制IP 核,实现数据变速率AD 采集、数据环形存储、数据环 形读取、以及数据飞读(实时数据读取)等功能。同时,对于NiosII CPU 设计串口(UART) 协议,以便前置机与传感器节点通信,实现不同命令操作功能,方便对水声试验过程中波形 数据的变化进行仿真处理,以满足试验要求。

本设计采用 MICRO 公司的MT48LC32M8A2 型号容量为32Mbyte 的SDRAM,芯片地 址线为25 位,每个地址存储16 位数据。根据水声通信试验要求,声波频率为40KHz,每 个正弦波采样16 个点,则采样时钟要求至少640KHz,本系统设计采样时钟最大40MHz。 同时,环形存储深度最大为32Mbyte,每次采样存储数据占2byte,则至少可以采样25 秒正 弦波数据。环形存储区域大小,以及采样时钟都可以进行参数化配置,能够满足试验要求。 系统整体分为硬件逻辑设计,与软件程序设计两部分。

[p]

3 系统整体设计

3.1 硬件逻辑设计

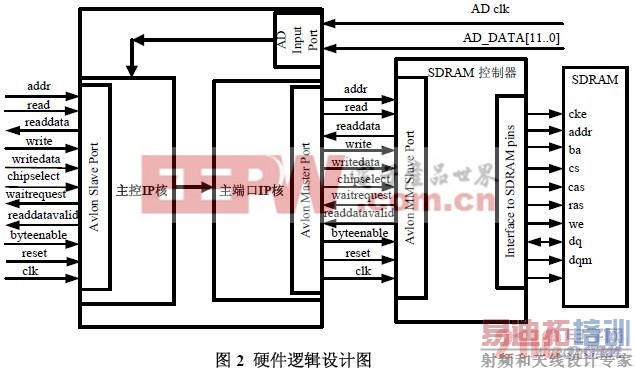

硬件逻辑设计主要包括主控IP 核设计与主端口IP 核设计两部分工作,分别实现对于 AD 采样数据的存储和读取时序控制,以及AVALON 总线的主端口建立的目的。硬件逻辑 利用IP 核模块化,移植性好的特点,方便整合到传感器节点的整体设计当中。作为传感器 节点的组成部分,为水声通信试验的顺利进行提供可靠保证。 硬件逻辑设计图,如图 2 所示。

3.1.1 SDRAM 主控IP 核设计

主控IP 核通过对于QuartusII 自带的SDRAM 控制器进行控制,实现变速率AD 采样的 功能,以及读写SDRAM 的逻辑功能。由于SDRAM 控制器实现了对于SDRAM 芯片的时 序操作,所以读写时序设计是针对SDRAM 控制器进行[3]。

系统读 SDRAM 操作分为数据飞读与数据环形读取两种功能[4]。其中,数据飞读是将当前AD 采样值送回至CPU,并通过串口返回到前置机,方便实时数据监控。对于数据环形 读取SDRAM 操作,通过设置首地址指针寄存器,在每次写操作之后自动加一,实现环形 存储水声通信数据的目的。在每次环形数据读取操作发起之前,预读首地址指针寄存器,以 此为起始地址,始终读取最新时刻的采样存储数据。 读操作过程主要状态机,如图 3 所示。

其中 work 过程包含的独立状态机,由如下四部分构成:

(1)first:片选有效,读使能有效,送读SDRAM 地址。

(2)second:读使能有效,满足SDRAM 控制器读时序要求。

(3)third:判断sdram_read_wait 信号值,如果为1,则维持当前状态,同时读使能信号置位;如果为0,则进入下一状态。

(4)fourth:判断sdram_read_valid 信号值,如果为0,则维持当前状态;如果为1,将读回数据写入读SDRAM 数据寄存器,同时读使能信号复位。

变速率AD 采集与数据环形存储操作主要是由主控IP 核写SDRAM 的过程实现。为保 持采样时刻数据的稳定性,系统对AD 时钟进行分频,通过设置不同分频寄存器,实现变速 率采样的目的。数据环形存储SDRAM 操作是靠每次分频时钟SDRAM_WRITE_CLK 的上 升沿触发,基本时序过程与读过程状态机类似。系统从0 地址开始写操作,一旦写满预设存 储区域,则从下一写时刻开始,数据写入初始地址,以此类推,实现环形存储操作。同时, 读写操作不能进行同时进行,通过读写选择控制器的设置,分别按照不同状态进行操作。

[p]

3.1.2 主端口IP 核

因为SDRAM 主控IP 核在NiosII 软核CPU 总线控制下作为从端口,所以不能主动发起 读写操作,因此必须新建第二条AVALON 总线,设计读写主端口IP 核,才能实现读写外接 SDRAM 芯片的功能。主端口IP 核的时序操作,是对主控IP 核的时序转接,面向SDRAM 控制器进行控制。根据读写使能信号不同,进行不同时序传送。

3.2 软件程序设计

NiosII CPU 作为软核,可方便进行模块化操作,具有可移植,可配置,易整合的特点。 在本设计当中,软件设计主要实现以下五种主要功能:单点写SDRAM,单点读SDRAM, 数据飞读,连续写SDRAM,连续读SDRAM 的功能。在程序当中留有接口,方便其他功能 整合,符合模块化设计的要求。

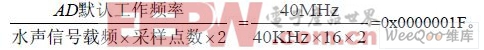

首先,完成功能的初始化,主要是设置选择操作模式与存储 AD 数据的时钟分频系数。 作为SDRAM 的读操作必须满足写满之后,方可进行,所以初始化主控IP 核为写SDRAM 操作。设置分频系数可以按照如下公式计算:

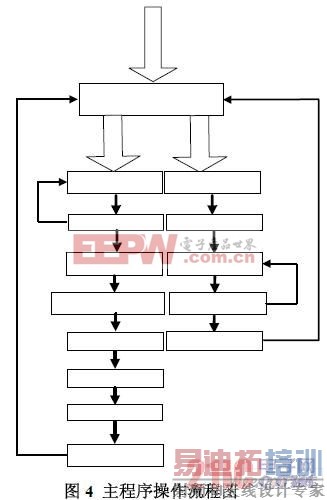

其次,通过对于串口进行协议解析,分别实现五部分预设功能。主程序操作流程如图4所示。

实现的五部分功能依次为:

(1) 单点写SDRAM 操作:CPU 给出地址,数据,以及写操作选择信号。

(2) 连续写SDRAM 操作:CPU 只是给出写操作选择信号,由主控IP 核将AD 数据写入至SDRAM 环形存储区域内。

(3) 数据飞读操作:只需要读取飞读数据寄存器,可以将当前状态AD 输入值送回至CPU,侦测当前状态。

(4) 单点读SDRAM 操作:CPU 送出读SDRAM 地址,然后选择读操作,设置控制寄存器为0x00000001,启动读操作。最后将读回数据通过串口实时回传。

(5) 连续读SDRAM 操作:是将基本读操作进行循环执行。设置串口回传缓冲区为80 字节,连续读SDRAM 数据并连续填写缓冲区,一旦填满,则启动串口发送。同时,读地址在每次读操作结束后自动加一,当操作次数达到环形空间最大存储数量时,停止连续读操作。

4 结束语

本设计作为水下无线传感器网络(UW-ASN)节点的设计组成部分,具有结构清楚,功 能完善,整合性强,性能可靠的特点。设计整体架构的模块化操作以及可编程性,使得整个 设计开发的具有灵活性与低风险性。经项目试验验证,该数据采集与存储设计满足传感器节 点的功能要求,为水声通信试验顺利进行以及水下无线传感器网络的功能完善提供可靠保证。

本文创新点:在系统功能设计当中,充分考虑了模块的可重用性和可移植性,通过IP核的设计实现底层驱动,提高系统集成度,充分发挥了SOPC技术的优势。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...