- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的单片机外围接口电路设计

摘要:利用现场可编程门阵列 FPGA实现单片机的外设接口电路可以简化单片机系统的硬件电路,提高系统的集成度、可靠性和系统设计的灵活性。本文介绍了基于 FPGA的单片机外设接口电路的基本设计方法,分别给出了各个功能模块的设计思路和实现方法。所有功能的实现全部采用 VHDL进行描述。

0 引言

单片机具有性价比高、功能灵活、易于人机对话、数据处理能力强等特点。单片机应用系统通常由键盘、显示器、通信接口、存储器、A/D、D/A电路等部分组成。传统的单片机系统经常要用标准的逻辑电路或专用的接口芯片来组成外围电路,如地址译码、I/O扩展等功能通常由标准的TTL/COMS逻辑电路或各种专用接口芯片实现,这样就会使系统的芯片数增多,接线复杂,从而使电路板面积增大、可靠性和 EMI性能减低,难以实现设计的小型化、集成化和高可靠性。而可编程门阵列FPGA的LCA结构和它丰富的内部资源可以用来设计各种组合逻辑和时序逻辑电路,因此使用FPGA设计单片机的外围电路能够大大简化系统硬件结构,使系统的设计、修改和扩展都变的十分灵活方便。本文通过对FPGA器件进行功能设计,取代传统单片机系统中外设接口用的标准逻辑电路和专用的接口芯片,使单片机系统的硬件电路大大简化并提高其可靠性。当需要改变系统性能时,可以通过对FPGA重新编程而不用改变硬件电路,提高了系统设计的灵活性。

1 系统设计方案

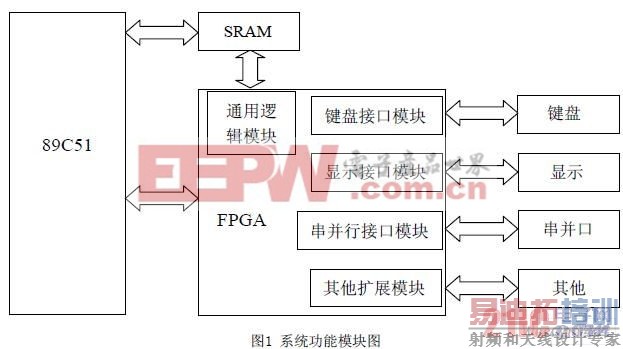

根据一般单片机系统设计的需要,本文所设计的系统具有以下几个功能模块,如图1所示。

1 )通用逻辑模块:根据具体的情况产生各种不同的逻辑电路及控制信号,代替传统的标准逻辑芯片。本文将其设计为扩展存储器时用到的地址锁存器。

2 )键盘接口模块:代替传统的单片机与键盘的接口电路,用 FPGA编程完成消除抖动及按键识别功能。本文将其设计为4×4扫描键盘的通用接口。

3 )显示接口模块:代替传统的单片机与显示器的接口电路,用 FPGA编程完成译码、扫描等功能。本文将其设计为4位七段动态 LED接口。

1 )串并行接口模块:实现单片机与其外设的串行或并行数据通信。本文将其设计为串行通信接口模块。

2 )其他扩展模块:实现单片机的一些其他常用功能,如 PWM驱动、A/D、D/A转换的控制等。

本设计所采用的FPGA器件是 ALTERA公司的Cyclone-TM系列芯片 EP1C6Q240C8,它具有5980个逻辑单元, 92160个比特的嵌入 RAM。系统开发工具为硬件描述语言VHDL,开发平台为Quartus Ⅱ。

[p]

2 系统模块实现

2.1 通用逻辑模块

FPGA可以设计成各种组合逻辑和时序逻辑电路,完成锁存、三态输出、多路选择、编译码、计数、寄存等功能。在实际应用中可以根据需要选择相应的功能模块组成符合设计要求的逻辑功能。

本系统中设计的为扩展存储器时用的地址锁存器(功能与带三态缓冲输出的8D锁存器

74LS373相似),其 VHDL描述为: process(oe,enable,d) begin if e="1' then

q=ZZZZZZZZ;

else if enable='1' then q=d; end if;

end if;

end procESS; 其中oe为三态门的使能信号,当 oe为低电平时三态门处于导通状态,允许q输出到外部,当 oe为高电平时三态门处于断开状态,输出处于浮空状态; enable为锁存控制信号,当做锁存器用时,应使oe为低电平,这时,当 enable为高电平时,锁存器输出状态与输入状态相同,当enable从高电平返回到低电平(即下降沿)时,输出不变,即输入端的数据锁入锁存器中。

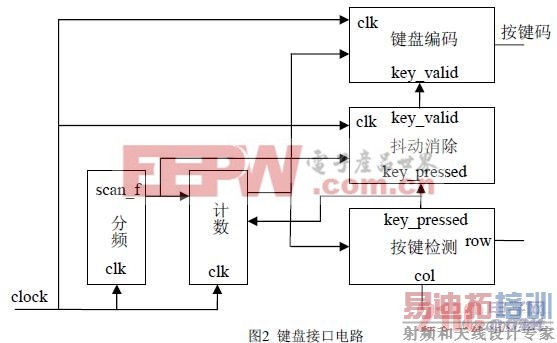

2.2 键盘接口模块键盘是单片机应用系统中一个很重要的部件,它能实现向系统输入数据、传送命令等功 能,是人工干预系统工作的重要手段。本文所设计的键盘接口电路框图如图2所示,由分频电路、键盘扫描计数器电路、键盘按键检测电路、按键抖动消除电路和键盘编码电路等组成。

其中clock为时钟脉冲, col为键盘的列输入,row为键盘的行输出,scan_f为扫描频率, key_valid为按键确定信号,butt_code为按键值。首先,将外部时钟信号分频为适合键盘的扫描频率;计数器的计数值输出到按键检测电路,检测使用者是否按下键盘,同时输出到键盘编码电路对键盘数值编码;当使用者按下键盘时,按键检测电路的 key_pressed将为0,并输出到计数器使计数停止,同时抖动消除电路在确认使用者正确按键后,输出按键确定信号。

2.3 显示接口模块

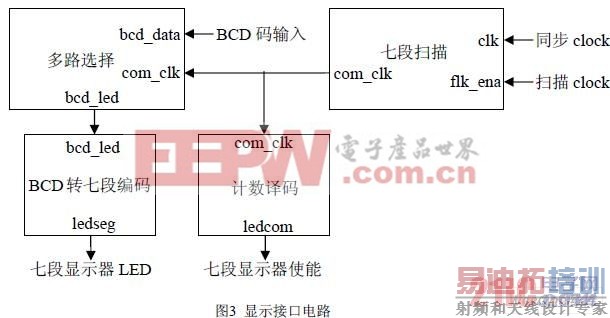

显示功能是单片机应用系统中实现人机对话的基本功能之一,用户通过灵活的显示方式方便的了解系统的工作情况。在简单的应用系统中常用LED数码管或LCD显示器显示数据或工作状态。本文设计的为一个4位七段动态 LED数码管显示接口电路,电路框图如图3所示,它由BCD多路选择器、BCD对应七段显示器编码电路、计数译码电路和七段显示器扫描电路等组成。其中clk为同步时钟脉冲信号, flk_ena为扫描时钟脉冲信号, bcd_data为输入的BCD码,ledseg为七段显示器数值输出, ledcom为七段显示器输出使能。

2.4 串并行接口模块

虽然大多数单片机都带有通用的串行接口,但自行设计的接口意味着更大的使用灵活性,特别是FPGA的高速特性允许更高的数据传输速度,在实用中有重要意义。作为范例, 本文设计了基于RS232-C标准的异步串行通信接口,它主要由数据总线接口、控制逻辑、波特率发生器、发送和接收等部分组成,其功能主要包括微处理器接口,用于数据传输的缓冲器(Buffer)、帧产生、奇偶校验、并转串,用于数据接收的缓冲器、帧产生、奇偶校验、串转并等。

[p]

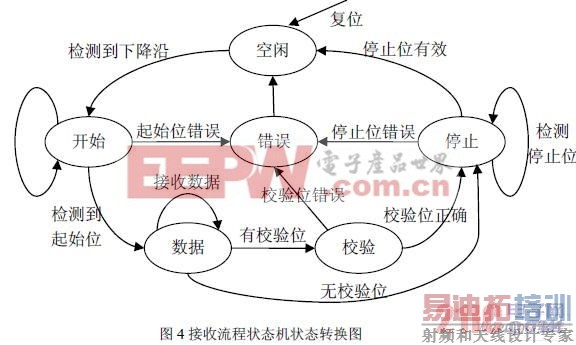

2.4.1 接收模块

异步串行通信是逐个字符进行传输的,并且传送的每一个字符格式都相同,均以一位起始位开始,中间有若干位数据位,然后是一位校验位(可选),昀后是停止位,停止位后面是不定长度的空闲位。这样就保证了起始位开始处一定有一个下跳沿。接收逻辑首先通过检测数据的下降沿来检测起始位,产生采样时钟,然后利用采样时钟来采样串行输入数据,在缓冲器中做移位操作,同时产生校验位,在第 8位处比较校验位是否正确,在第 9位处比较停止位是否为高,然后产生错误指示信号。本文采用状态机进行设计,其 FSM状态转换图如图 4所示。

2.4.2 发送模块

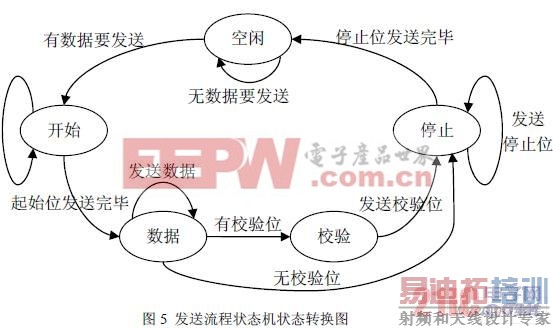

发送部分检测控制信号,当有数据要发送时只要按顺序依次发送 1位起始位、 5-7位数据位、一位校验位(带校验时)和 1位(或 1.5位、2位)停止位即可。其 FSM状态转换图如图 5所示。

停止位发送完毕

无数据要发送发送停止位

3 结束语

将设计下载到芯片中,综合报告显示只消耗了FPGA很少的一部分资源。整个系统的功耗也大为降低。由于FPGA为大规模集成电路,其集成度和工作速度随着技术进步和产品升级不断提高,所以用FPGA实现单片机外围接口电路可以大大改善单片机系统的性能,系统的外围逻辑越是复杂,FPGA的潜力越能得到更好的发挥。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:PCB板电路中的数字地和模拟地设计方法

下一篇:eda技术软件介绍