- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

XC9500系列CPLD遥控编程的实现

摘 要: 简单介绍了XC9500系列CPLD器件及其系统内编程(ISP)性能,接着讲述了XC9500系列CPLD器件遥控编程的实现方法,并重点介绍了在遥控编程系统中应用微控制器(lntel 8031)实现嵌入式ISP的软硬件设计。

关键词: CPLD 遥控编程 ISP微控制器

测温结果数据比较

1 XC9500系列CPLD器件及其ISP性能

XC9500系列CPLD器件是由多个功能块(FB)和IO块(IOB)组成,可用开关矩阵Fast CONNECT完全互连的子系统,IOB提供输入和输出的缓冲,每个FB提供具有36个输入和18个输出的可编程逻辑容量。Fast CONNECT开关矩阵连接所有的FB的输出和FB的输入,对于每个FB,12至18个(取决于封装的引脚数)输出和有关的输出使能信号直接驱动IOB。

所有XC9500系列CPLD器件都是系统内编程的,最小达一万次编程/擦除次数,支持扩充的IEEE 1149.1边界扫描标准,XC9500的结构特性着重满足系统内编程的要求,增强的引脚锁定能力可以避免重做昂贵的印制板,扩充的JTAG指令集允许编程模式和系统内诊断的各种控制。由于JTAG在其权限内把ISP的性能扩充到1149.1的测试标准中,XC9500系列CPLD器件可以通过JTAG接口实现ISP性能。XC9500系列的系统内编程性能,不仅为现场编程和调试提供了方便,允许用户编程和再编程已经安装在系统印制板上的XC9500系列器件来改进样机、更新制造流程;而且正是由于系统内编程性能使得摇控编程成为可能。下面对XC9500系列CPLD器件摇控编程的实现方法做一介绍。

2 XC9500系列CPLD器件遥控编程的实现方法

对CPLD器件的编程,传统的方法都是现场工程师通过PC机来实现的,PC机上必须有EZTag或者JTAG编程器软件,并且PC机必须通过Xchecker或JTAG电缆和目标板相连,然后将JEDEC编程数据下载到目标板的CPLD器件中去。这种传统的编程方法要求工程师必须亲临现场,这就带来一个问题,那就是当产品销售以后,如果要对它升级(主要是指升级CPLD器件的功能)就十分麻烦。本文所要介绍的遥控编程不同于传统的编程方法,它不需要工程师亲临现场,只需在系统设计时将编程控制电路加入到嵌入式系统中去即可实现。

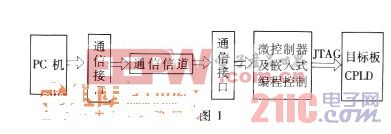

遥控编程的方框图如图1所示。要实现遥控编程,关键在于通信和嵌入式下载技术。通信部分包括通信接口和通信信道,它完成远程数据传输,即将本地PC机生成的CPLD器件编程数据传输到远程的目标系统的嵌入式下载模块(即图中所示的“微控制器及嵌入式编程控制”部分);嵌入式下载技术是指用微控制器通过JTAG接口实现对XC9500系列CPLD器件编程。通信可采用现有的各种通信技术,例如通过电话线用调制解调器实现通信以及通过电缆、激光和无线电等实现通信,在本文对通信的实现不做过多的介绍,下面只以简单的红外收发器为例加以说明,重点介绍微控制器及嵌入式编程控制的软硬件实现。

3 微控制器及嵌入式编程控制的实现

3.1 硬件设计

微控制器及嵌入式编程控制硬件电路如图2所示,由微控制器lntel 8031、时钟、地址锁存器74ls373、程序存储器27512、数据存储器RAM(包括XSVF格式数据存储器)、XC95108及数据输入接口等几部分组成。图中8031不仅可用来对CPLD进行编程控制,而且还可实现其它控制和处理,因为设计中使用了一片XSVF(Xilinx Serial Vector Format格式数据存储器,在XC95108的控制下可以在后台实现数据通信,并将XSVF格式数据存储到XSVM RAM中,当数据接收完毕时再中断微控制器,在微控制器的中断服务子程序中通过JTAG接口实现对目标CPLD器件编程。从图中可见,除了XC95108、数据输入和XSVF RAM部分外,其它部分和常见的8031应用系统一样,这里不再赘述,下面主要讲述数据输入和XC95108的内部功能。

[p]

数据输入由红外收发器实现(如可用Siemens公司的IRM3105),它所接收到的数据是由PC机生成的按RS232格式打包的XSVF格式编程数据文件,收发器通过UART(Universal Asynchronous Receiver Transmitter) 接口和XC95108相连。

XC95108包含URAT接收器、时序控制状态机及总线控制器等。URAT接收器对接收到的数据进行校验,并且去掉起始位和结束位,如果接收正确则通知时序控制状态机数据接收就绪,如果接收不正确则给出错误指示。

时序控制状态机是遥控编程的核心,包括四种状态,即HIGH、LOW、DOWNLOAD和ISP。XSVF文件的第一、二个字节为传输的字节总数,在状态HIGH和LOW时字节总数的高低字节被保存到一个变量中,当在DOWNLOAD状态时,每当往XSVF RAM写入一个字节,该变量的值减1,同时XSVF RAM的地址增1。一旦全部XSVF文件都写入XSVF RAM中,状态机便进入ISP状态,此时中断微控制器,微控制器响应中断并进入中断服务子程序。中断服务子程序根据XSVF RAM中的信息通过JTAG对XC9500 CPLD器件进行编程。

总线控制器根据时序控制状态机控制XSVF格式数据存储器的数据总线的切换,当在DOWNLOAD状态时,总线控制权交由XC95108;当在ISP状态时,总线控制权交由8031;当在HIGH和LOW状态时,总线为高阻状态。

3.2 XSVF文件的生成

上面提到过远程端接收到的数据为XSVF文件,XSVF文件是由本地PC机生成的,它是如何生成的呢 首先将设计数据输入,开发系统进行设计转换生成JEDEC器件编程文件;然后,由Xilinx公司提供的软件EZTagTM自动读取JEDEC文件并转换成SVF文件,SVF格式是专门用来描述IEEE 1149.1(JTAG)总线操作的格式,SVF文件中不仅包含CPLD的编程数据,也包含有编程命令,但由于SVF格式为ASXII码,因要求较大内存,不适合嵌入式应用;最后,由软件svf2xsvf将SVF格式转换成XSVF格式,XSVF格式为压缩的二进制格式,占用存储空间小,因而更适合嵌入式应用。

3.3 嵌入式ISP编程流程

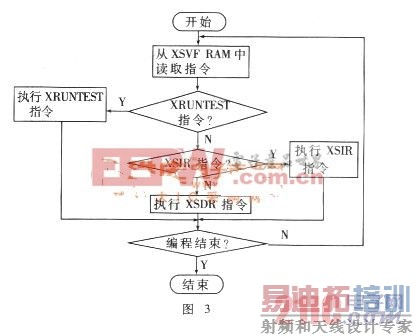

XC9500通过四线测试存取端口TAP(Yest Access Port 和TAP控制器来执行系统内编程和IEEE 1149.1边界扫描测试(JTAG)。TAP包括TCK、TMS、TDI和TDO四个引脚,TAP控制器是16状态的状态机,控制边界扫描电路按照TMS运行,执行由IEEE规定的状态图(详细内容参见参考文献1,下面所提到的状态,如Shift-1R、Shift-DR等包含在16个状态之中)。微控制器根据XSVF文件提供的指令和数据激励TAP端口,在TAP控制器的控制下实现XC9500 CPLD的ISP编程。流程图如图3所示。

XSVF格式的编程文件包含编程指令和数据,编程指令主要有三条,即XRUNTEST、XSIR和XSDR。微控制器读取指令后进行解释,并根据指令执行相应的操作。

XRUNTEST指令指定在执行下一条XSIR和XSDR指令之前在Run-Test/ldle状态停留的时间,指令之后紧接的4个字节为时间数值(毫秒数);当微控制器读取的指令为XSIR时,便为TMS和TCK提供激励直至进入Shift-IR状态,然后读取指定的数据长度值和数据,并将数据送到TDI口;微控制器读取XSDR指令时,首先读取将要在Shift-IR状态输出的数据,再触发TMS和TCK直接进入Shift-IR状态,并保持TMS为低,停留在Shift-IR状态,将XSVF文件数据输出到TDI口,并存储从TDO口接收到的数据,在所有数据都输出到TDI口之后,TMS变高进入Exit-1-DR状态,然后将从TD0输入的值和TDO预期值相比较,如果不匹配则转出错处理,如匹配则重新进入Run-Test/ldle状态。微控制器循环地从XSVF RAM中读取指令和数据并执行,直到编程结束。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:FPGA与CPLD的比较

下一篇:多层复合布线板之弯曲PCB简介