- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

逻辑器件的同步设计

在设计逻辑和电路时,经常会遇到这样的问题。即采用普通集成电路实现的设计移植到FPGA/CPLD逻辑器件时,其设计无法正常运行。另外,有些设计己经在逻辑器件申实现或通过了仿真测试。但经过重新布线设计后,该设计不能正常工作。出现这些问题,基本上是在设计中出现了异步设计。典型的异步电路有以下几种。

(1)组合环路

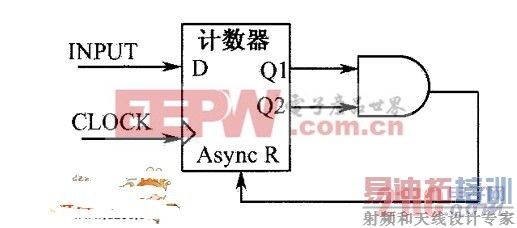

组合环路是数字逻辑设计中不稳定性和不可靠性最常见的原因之一。在同步设计中,所有的反馈环路都应该包括寄存器。组合环路直接建立没有寄存器的反馈,违反了同步设计的原则。例如,当把一个寄存器输出通过组合逻辑反馈给同一个寄存器的异步引脚时,就会产生组合环路,如图1所示。

图1 组合逻辑反馈的异步电路

组合环路是高风险的设计结构,这是因为组合环路的功能通常依靠环路逻辑的相对传播延迟。正如所讨论的,传播延迟可能改变,那么环路行为也可能发生改变。

(2)延迟链路

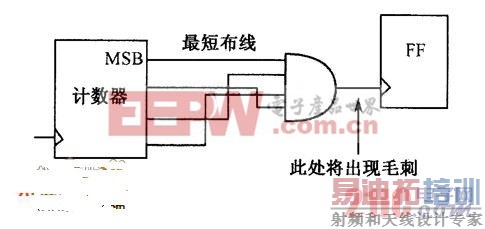

当两个以上连续的单输入单扇出节点引起延迟时就会产生延迟链路,通常把反相器连在一起增加延迟。延迟链通常由异步设计引入,有时用来解决其他组合逻辑引起的竞争冒险,如图2所示。FPGA延迟会随每次布局布线的变化而改变,延迟链可能引发不同的设计问题,包括增加了设计对工作条件的敏感性,减小了设计的可靠性,从而不利于移植到其他器件结构上。在设计中要避免使用延迟链,而应采用同步设计。

图2 延迟链引发设计问题

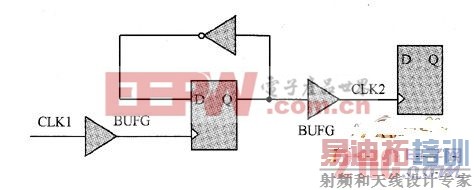

(3)异步计数器

在低速且小规模的集成电路设计中,经常采用异步结构进行计数器或分频器设计,如图3所示。因为这种电路结构简单,连线较少。但这种电路结构非常容易产生竞争冒险现象,并且无法提供电路的工作速度。

图3 异步计数器结构产生竞争冒险现象

综合以上因素,为提高逻辑设计的可靠性,在逻辑设计时应尽可能地采用同步设计。另外,由于FPGA器件的内部结构特性,采用同步设计可以有效地利用器件中的逻辑资源。在同步设计时,只要逻辑延迟不等于或大于时钟周期就可以避免毛刺对逻辑运行的影响,使系统稳定地同步于系统时钟。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...