- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的数字三相锁相环优化设计

摘要:数字三相锁相环中含有大量乘法运算和三角函数运算,占用大量的硬件逻辑资源。为此,提出一种数字三相锁相环的优化实现方案,利用乘法模块复用和CORDIC算法实现三角函数运算,并用Vetilog HDL硬件描述语言对优化前后的算法进行了编码实现。仿真和实验结果表明,优化后的数字三相锁相环大大节省了FPGA的资源,并能快速、准确地锁定相位,具有良好的性能。

关键词:FPGA;三相锁相环;乘法复用;CORDIC

0 引言

在PWM整流器、不间断电源(UPS)、有源电力滤波器(APF)等需要并网的电力电子装置控制中,获得电网电压的相位是系统控制的前提。一般都采用锁相环PLL来获取电网电压的相位。三相电网电压可能存在三相不平衡,电压有谐波、频率、相位突变。为了全面反映电网电压的真实状况,采用三相锁相环来锁定电网电压相位角,而且三相锁相环的抗干扰能力更强。采用现场可编程门阵列(FPGA),并以硬件方式实现三相锁相环,可充分体现FPGA硬件的高速性,且不受CPU资源的制约。

本文对数字三相锁相环的系统原理和算法实现进行了研究,并对三相锁相环在FPGA中实现的算法进行了优化设计。通过采用乘法模块复用和基于坐标旋转数字式计算机(CORDIC)的算法计算含有三角函数的坐标转换模块,节省了数字三相锁相环实现所需的硬件开销。用硬件描述语言Verilog HDL设计出了整个三相锁相环系统。该三相锁相环在以Altera公司芯片CyconeⅡEP2C15AF256C8为主芯片的实验板上进行了验证。

1 三相锁相环的基本原理

1.1 锁相环基本原理

锁相环一般由鉴相器(PD)、环路滤波器(LF)、压控振荡器(VCO)组成。锁相环是一个相位反馈系统。鉴相器把周期性的输入信号与VCO反馈来的相位信号进行比较,得到一个相位误差;误差经环路滤波器进行滤波,环路滤波器的输出被用作控制信号送入VCO,用来消除输入、输出信号的相位差。

1.2 三相锁相环的结构与原理

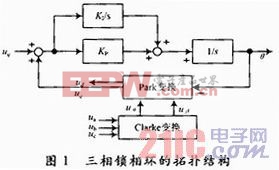

三相锁相环的拓扑结构如图1所示。

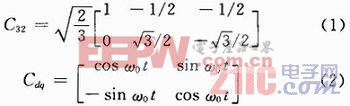

数字三相锁相环的关键模块是矢量控制中的2个系统变换:从a-b-c三相静止坐标到α-β两相静止坐标的Clarke变换(C32)和从α-β两相静止坐标到d-q两相旋转坐标(基波同步速为ω0)的Park变换(Cdq):

[p]

[p]

式中:U为电压的有效值。

锁相环未锁定时q分量为一交流分量,与已设的分量q*=0比较得到一直流分量,以此完成鉴相。直流分量再经过由PI控制器组成的低通滤波器控制压控振荡器,最终使得ω与ω0相等,q分量为0,达到锁相。

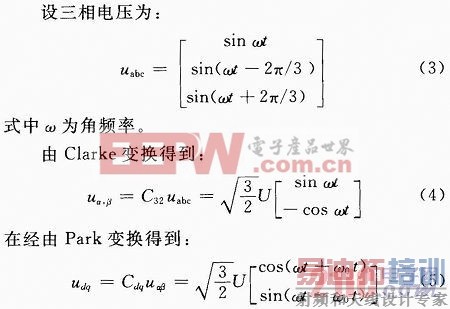

2 三相锁相环的系统仿真

根据图1三相锁相环的拓扑结构,在Matlab/Simulink中搭建系统仿真模型。三相电压为220 V,采样频率为fs=5 kHz,压控振荡器的中心频率为f=50 Hz,通过仿真调整,最终确定Kp=0.02,K1=0.001,使锁相环锁相的速度与精度达到最佳效果。图2(a)是三相锁相环在0.05 s内的三相电压ua,ub,uc仿真波形;图2(b)是三相锁相环在0.05 s内的两相旋转坐标下ud,uq仿真波形,d轴分量大约在0.01 s稳定为0,即0.5个周期达到锁相;图2(c)是三相锁相环在0.05 s内的三相电压a相位角θ与VCO输出相位角θ*的仿真波形,θ与θ*在0.01 s基本完全重合,达到锁相。结果表明,三相锁相环可在0.5个周期内快速、准确地锁定电网电压。

[p]

3 三相锁相环的FPGA设计

3.1 未优化的三相锁相环的FPGA结构

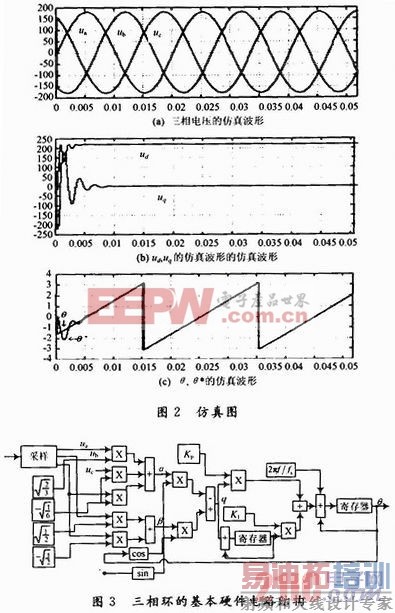

根据图1三相锁相环的拓扑结构及原理,三相锁相环的基本硬件结构如图3所示。

首先通过采样,将三相电压离散化并处理为32 b有符号数,经过Clarke变换与相应的参数相乘后相加得到两相静止坐标的分量μα,μβ。共有5个乘法运算,3个加法运算。然后是Park变换,在此三相锁相环中只需要μq分量,需要2个乘法运算,2个三角函数计算,1个加法运算。后面的PI控制器需要2个乘法运算,2个加法运算。最后是VCO需要2个加法运算。整个运算过程共需要9个乘法运算,9个加法运算,2个三角函数运算。

从对三相锁相环的基本结构分析可知,整个过程需要9个乘法运算,2个三角函数运算。在FPGA中实现乘法运算和三角函数运算会消耗大量的资源。特别是传统的查表法三角函数运算在消耗大量资源的同时还存在精度问题。

3.2 三相锁相环的优化设计

由于该设计采用25 MHz的系统时钟,而采样频率为5 MHz,所以设计的时序余量非常大。依据面积和速度的平衡与互换的基本原则,针对乘法运算多的特点,采用乘法复用,系统中只保留一个乘法模块,通过合理选择,达到时分复用。

在Park变换中存在的三角函数运算,可以通过CORDIC算法优化。CORDIC算法是通过基本的加法和移位运算来代替乘法和三角函数运算的,特别适合矢量旋转的运算。使用迭代的方法,多步完成要旋转的角度。CORDIC算法可以实现如式(6)所示的运算。

式中:x0,x1为初始坐标;θ为要旋转角度;y0,y1为最终的坐标。通过对式(6)的分析与Park变换相比较可以发现,只要把角度取负,就可以通过CORDIC算法完成整个Park变换的运算。

优化后系统的硬件结构如图4所示。

4 结语

本文分析了三相锁相环的基本原理。针对FPGA的特点对锁相环进行了优化设计,并利用Verilog HDL硬件描述语言编码实现。该设计可直接用于PWM整流器、UPS等控制系统中。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:基于FPGA的逆变控制系统的研究

下一篇:快速实现SHA-1算法的硬件结构