- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于Camera接口的船用导航雷达显示设计

摘要 介绍了基于ARM的Camera接口船用导航雷达显示设计。通过FPGA将雷达回波转换成ITU—R BT601/656视频信号,将视频信号送入ARM的Camera接口,存贮在帧缓存存储器,ARM的显示控制器以DMA的方式读取帧缓存数据,与人机界面在显示控制内部混合叠加后直接送显示器显示。该设计实现了雷达的回波和人机界面的同步显示,满足了船用导航雷达系统的显示要求,并在工程上验证了该设计的有效性。

关键词 雷达;FPGA;Camera;显示控制器;同步显示

船用导航雷达是测定本船位置和预防冲撞事故不可缺少的系统,其能够准确捕获其他船只、陆地、航线标志等物标信息,并将其显示在显示屏上。船用导航雷达与军用雷达相比成本较低,因此多采用基于嵌入式ARM(Advanced RISC Machines)设计的小型化平台。小型化平台计算机软件实现回波显示的方式,对计算机资源的开销较大,且实时的回波显示对软件的处理流程要求也较高,因此实现回波显示硬件设计成为必要。

通过FPGA(Field Programmable Gate Array)将雷达回波转化成视频信号,送至ARM的Camera接口,以视频图像的方式与人机界面在显示控制内部混合叠加,实现雷达的回波和人机界面的同步显示,成为解决小型化雷达终端回波显示的可行方案。

1 工作原理

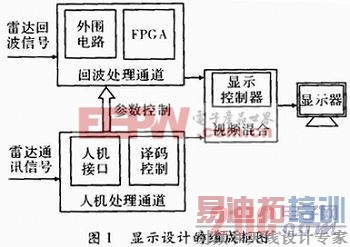

船用导航终端显示设计的组成框图如图1所示,主要由3部分组成。回波处理通道由FPGA和外围电路组成,主要完成雷达信号接口匹配、回波采样、回波峰选处理、扫描坐标变换处理、余辉尾迹控制、时序控制和视频格式编码等功能。人机处理通道由ARM计算机组成,由载入的软件完成二次显示信息处理、操控窗口控制、工作参数设置以及与系统和整机的通信等。视频混合模块由ARM的显示控制器实现,在行、场同步控制信号的控制下,DMA(Direct Memory Access)的方式读取系统内存中显示数据,完成雷达回波和人机接口的叠加显示。

2 显示设计及实现

船用导航雷达终端的显示设计主要有回波的实时校正、回波近区覆盖/远区分裂补偿、ITU—R BT601/656视频编码、显示控制器混合叠加等多个功能模块的设计。

2.1 雷达回波数据的峰选实时校正

显示器半径的像素数量一般不等于雷达触发的距离采样数量,所以回波的显示处理均需要峰选。峰选就是将显示量程内的所有回波采样值按显示像素分组,在每组内选择最大值作为对应显示像素的辉度值,每组回波采样值的数目为峰选系数,按照峰选系数进行处理。峰选系数N由式(1)计算,N一般取小数点后两位

![]()

式中,N为峰选系数;R为显示量程,单位km;f为峰选始终频率,单位MHz;M为显示像素。

软件根据显示模式及量程计算出峰选系数后,由端口置入FPGA,FPGA根据峰选系数,将对应的峰选校正值存贮在内部ROM(Read-Only Memory)中,实时读取校正。

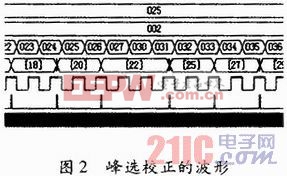

例如,峰选系数为2.25,在Altera Quartus中仿真的波形如图2所示。

[p]

2.2 回波近区覆盖、远区分裂的补偿

雷达显示系统接收的是雷达触发、雷达回波和方位信号,是一个极坐标系,显示时以行场同步扫描的方式进行,是一个直角坐标系。由于从极坐标转换成直角坐标固有的非线性影响,以及方位与雷达触发的异步关系,会出现回波的近区重叠和远区分裂的现象。解决近区的覆盖,在写入帧缓存的回波值之前,先读出该地址原有值,若大于则写入,否则保持原值。远区回波分裂采用两种方法补偿;(1)增加坐标转换查表法中正、余弦函数值的精度;(2)采用插值的方法,在一次方位处理完成后,在下一次触发前再以当前的回波值辅以新的方位进行显示处理。

插值的示意如图3所示。捅值的数量由雷达显示半径决定,而一般插值后的个数应大于或等于显示圆周的像素点,这样才能保证回波充满显示器所有像素,避免出现回波的分裂。由于转换过程中的非线性,近区不需要插值,为解决时序紧张的问题,可选择从某一显示距离开始插值,即远区补偿。

2.3 ITU—R BT601/656视频编码

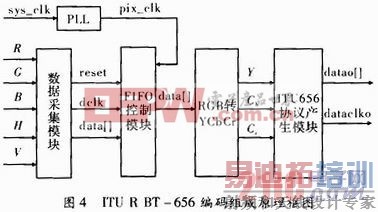

Camera接口支持两种接口的输入视频(1)ITU RBT-601 YCbCr 8位标准。(2)ITU R BT-656 YCbCr8位标准。前一种标准输出行场同步信号、8位宽度的数据信号和数据同步时钟,后一种标准的不输出行场信号,将定时基准码和行场消隐数据编在8位数据信号中,由Camera接口捕捉定时基准码实现数据的行场同步。设计采用ITU R BT-656 YCbCr 8位标准,视频数据的转换和编码由FPGA完成,组成原理框图如图4所示。

数据采集模块实现R(Red)、G(Green)、B(Blue)数据的同步处理,以便稳定的写入FIFO。FIFO控制模块完成对FIFO的读写控制和数据的缓存。RGB转YCbCr模块将输入的RGB数据转换成相应的YCbCr数据,R、G、B信号到Y、Cb、Cr转换公式为

Y=16+0.275R+0.504G+0.098B

Cb=128-0.148R-0.291G+0.4329B

Cr=128+0.439R-0.368B-0.071B (2)

ITU656协议产生模块用于控制产生ITU R BT-656YCbCr 8位标准的视频数据和同步时钟。

2.4 Camera接口

ITU R BT-601/656视频送至ARM的Camera接口,内部的测试样板可用来校准输入同步信号作为HREF(行信号)和VSYNC(场信号),CatchCam实时捕捉ITU信号。Camera接口内存在两个通道:一是Preview Scaler(以下简称P通道),用来产生较小的图像,用于预览;二是CodecScaler(以下简称C通道),用来产生编解码用途的视频信号。P通道和C通道各自保持独立。

Camera接口有4个DMA端口,分别是在AHB总线上进行预览的MSDMA输入,进行编解码的MSDMA输入,P通道颜色转换后输出DMA,C通道颜色转换后输出DMA。MSDMA读取Y:Cb:Cr4:2:2、Y:Cb:Cr4:2:0或RGB图像。4个主端口支持各种各样的应用,寄存器可分别设置4个DMA端口的使能。

Camera接口不能为默认优先级AHB总线的设备,其优先级必须与其他循环或通知仲裁优先级设备区别开,并保持独立,为保证显示的流畅性,包含Camera接口的AHB总线须比其他Multi—AHB总线的优先级高。[p]

2.5 显示控制器混合叠加

显示控制器有一个用于转换图像数据的模块,用于本地总线的后处理器或系统内存中的视频缓冲区到外部LCD驱动器接口的图像数据传输。显示控制器由VSFR、VDMA、VPRCS、VTIME和视频时钟产生器组成。VSFR包括可编程寄存器和调色板存储器,用于配置显示控制器,VDMA用于显示DMA,可将帧存储器内的视频数据转换到VPRCS。VPRCS接收VDMA发出的视频数据,转换为需要的数据格式后,如8 bit或16 bit像素,将视频数据直接发送到显示设备上。VDMA有5个通道和3个本地输入接口。为混合运行,CSC(Color Space Conversion)模块将YCbCr数据改变为RGB数据。显示控制器数据流模块图如图5所示。

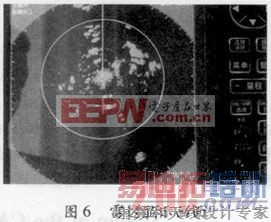

通过Camera接口送来的雷达回波窗口与其他窗口在显示控制器内完成了视频窗口同步混合。最终在显示器上显示的雷达画面如图6所示。

3 结束语

基于FPGA和嵌入式处理器ARM设计的船用导航雷达显示系统,利用FPGA完成雷达回波的标准转换和视频的编码,再通过Camera接口完成视频数据的接收,并在显示控制器内通过使用特殊的DMA—VDMA,未使用CPU,直接将视频数据显示在屏幕上,从而节省CPU资源,实现了雷达回波和人机界面的同步显示,满足了船用导航雷达系统的显示要求。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:PCB板级屏蔽腔及系统设计开发简介

下一篇:多层线路板的应用介绍