- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

CPLD器件在单片机控制器中的使用

自动控制的对象五花八门、品种繁多,要求控制器能够模块化、标准化、灵活配置;进入商品经济时代,允许设计者的开发周期越来越短,从几年、几月缩短到几月、几天;有时合同临近结束前,用户还会提出更改设计条款的要求。因此,需要设计者开发出适应性强、便于修改、配置灵活的控制器,以满足用户需求,争得商机。

从成本考虑,有时以单片机为核心器件,量身度造地为被控对象设计专用控制器,仍是一种较好的选择。

CPLD器件与单片机结合优势互补、相得益彰

单片机的一些优缺点

单片机具有强大的信息处理、逻辑分析、决策判断等能力,借助程序,通过输入/输出接口,实时检测被控对象的状态,控制其当前或预计的行为,组成智能化仪器设备。

但是,单片机存在不可克服的缺点和弱点,如:

低速 单片机靠执行指令来完成各种功能,不论多高的工作时钟频率或多么好的指令时序,其排队式串行指令执行方式使得工作速度和效率大打折扣。在高速实时仿真、高速数据采集等方面显得力不从心。

复位工作方式 单片机工作之初,需花一段时间经历复位过程;工作时,在某种干扰性突变情况下,也会复位,复杂的复位过程很可能就是工作不可靠的根源。

程序跑飞 偶然因素,会引起程序跑飞。虽然有“看门狗”或其他抗干扰措施,在极复杂的情况下,单片机的程序仍存在跑飞的可能,从而进入“死机”。

在单片机系统中,单片机的芯片通过印制板与系统中由其他集成电路组成的逻辑电路相连。一旦改变设计,可能重新制版,加长了开发周期。

CPLD器件的一些优缺点

随着微电子技术飞速发展,集成电路规模越来越大,产生了复杂可编程逻辑器件CPLD和现场可编程门阵列FP2GA(两种器件有类似之处,以下用CPLD器件简称),这些器件含有数量众多的可编程逻辑宏单元或逻辑块,他们能够任意组合,设计成功能各异的逻辑电路。

CPLD器件输入引脚的箝位电平和输出引脚的原始电平可预先设定,一开机立即就能达到预定电平,状态明确。各逻辑宏单元或逻辑块的输入信号仅需几ns~几十ns就反映到输出端,信号传输效率很高,适合高速采样等场合。

可编程逻辑宏单元或逻辑块之间的相互连线在同一封装内,受外界干扰影响小,电磁兼容(EMC)性能好。然而,对设计者来说,CPLD器件最大的优点在于可现场编程。改变逻辑关系时,无需更改外部线路板,只需用图形语言程序或硬件描述语言程序来改变电路,生成下载编辑软件,通过下载电缆输入CPLD器件即可,非常方便,特别有利于新品试制,大大缩短了开发周期。

CPLD器件虽然可任意组成各种逻辑电路,但在信息处理、逻辑分析、决策判断等“智能”方面比不上单片机,虽说可用CPLD器件仿真单片机,但毕竟有差距,一般多用作“状态机”或辅助逻辑电路。

CPLD器件和单片机结合能优势互补

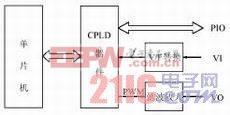

如果把两者结合起来,组成的控制器就能优势互补、相得益彰。大量工业控制的对象不属高速调节系统,这时,图1示例的控制线路比较节省硬件开销,适合CPLD器件的特性,容易调试,抗干扰能力强。

图1 基于单片机和CPLD器件的控制器方框图

若是高速调节系统,应采用并行A/D转换集成电路,用作输入信号VI的采样、转换电路。

[p]

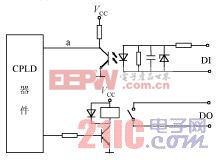

开关型接口

CPLD器件与外部设备的开关型的输入/输出端,可按图2所示方式连接,构成类似于PLC可编程控制器的开关型接口。有些设计者在a点处插入了整形电路,其实,当CPLD器件与单片机结合时,可借助滤波软件,消除抖动的影响,使得线路简洁。经实际使用,效果很好。

图2 开关型输入/输出接口

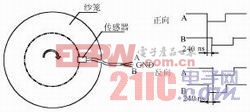

在高速采样或利用脉冲信号的竞争现象而工作的场合,CPLD器件比单片机更具有优越性。例如,某型号分条整经机,纱笼直径650~1000mm,需要判别转向。纱笼高速运转时,A,B二路信号的时间差最小约240ns。这样的时间差距,单片机很难处理;有时候又需要操作工人转动纱笼,调整位置,速度往往几乎为零,并可能反复变换方向。

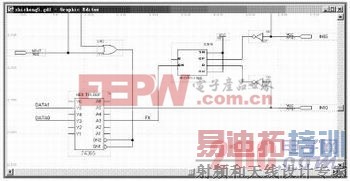

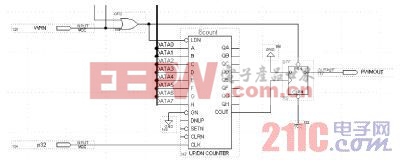

采用CPLD器件,组成如图4所示的判向电路,A路信号从IN05引脚输入,B路信号从IN10引脚输入,方向信号从数据总线的DATA0取出(波形见图5),传送给单片机。供单片机检出和脉冲计数。

这项应用的难点,不仅在于高速时判别转向,还在于工人转动纱笼时,情况复杂多变。虽说传感器内部配备了斯密特整形电路,当纱笼低速穿越传感器时,拉长跨越门槛电平的时间,会产生一串不稳定的跳变,发生计数错误。

图3 纱笼传感器信号及波形示意图

图4 判向电路

借助单片机的特殊处理程序和CPLD器件中其他逻辑电路,该整经机项目的控制器不论高速还是低速,都能可靠地检出方向和脉冲个数,未发生过错误。

图5 判向电路的仿真波形图

模拟信号接口

模拟信号输入接口

当控制对象不需要高速采样、高速调节时,采用图1控制器方框图中所示的模数转换形式,能够充分发挥CPLD器件逻辑宏单元可编程的长处。V/F转换器把输入的电压信号转为频率信号,供CPLD器件中的计数器(图1中未画出)计数,从而把模拟量转换成数字量。该计数器的字长、进制、模式根据需要可任意编程设定,比使用单片机内的计数器灵活方便。此处不详叙。

当控制对象为高速系统时,可采用并行A/D转换集成电路,这时宜采用并行口控制,可通过单片机或CPLD器件按常规方式对A/D电路的进行。

模拟信号输出接口

输出的调节信号,可采用脉宽调制(PWM)波形加低通滤波器方式,很方便地实现数模转换。PWM频率越高,滤波效果越好,数模转换通道如图6所示。

[p]

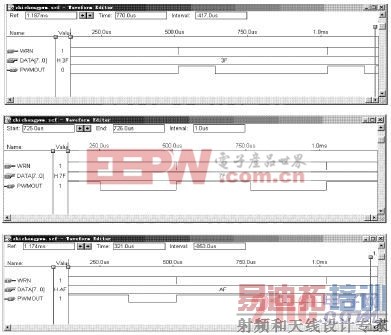

图7是在CPLD器件内设计的一个8位计数器PWM波形发生器的示例。填入不同的计数初值,将在PWMOUT端相应输出不同占空比的脉冲串(见图8)。

图6 数模转换通道示意图

图7 8位计数器PWM波形发生器示例图

图8 脉宽调制波形比较图

在图7中,时钟脉冲从P32引脚输入,WRN是写选通信号输入端,PWMOUT是输出端。

如果只使用CPLD器件,PWM波的周期和脉宽形成电路会比较复杂。结合单片机以后,PWM波形的周期就是单片机定时访问该计数器的WRN信号的周期,脉宽由单片机通过数据总线(DATA0~7)填入的计数初值决定。减少了CPLD器件内可编程逻辑宏单元或逻辑块数量的消耗。在图6中,整形电路主要起限幅、隔离作用。限幅之后,使幅度保持一致,并加大脉冲的上升沿和下降沿的陡削度,保证后级转换的电压幅度主要取决于脉宽,减少附加误差。

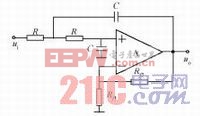

滤波电路影响到转换的线性度,根据不同的课题要求,可采用无源滤波器、有源一阶、二阶低通滤波器。巴特沃兹型滤波器具有平坦的通带幅频特性,最适于本转换电路方式的需要。以图9所示巴特沃兹二阶低通滤波器为例,其截止频率fo为:

图9 二阶低通滤波器

截至频率fo应该大于信号带宽边沿,但是要远小于PWM信号的频率。滤波器R,C的取值直接影响转换后的纹波幅度和转换速率,两者对R,C的要求正相反,应均衡考虑。必要时,通过实验选取合适的数值。

脉宽调制(PWM)波加低通滤波而实现数模转换的电路,其精度主要取决于计数器的字长、PWM的频率、低通滤波器的形式和元件选型。注意到这几点,转换效果令人满意。本文以8位计数器举例,实际应用中,考虑种种因素,一般采用10~14位计数器。

图6中的功率放大级主要是把滤波器输出的信号,以适当的放大、反馈形式,转换成符合Ⅱ型仪表、Ⅲ型仪表规定的电压、电流信号,或转换成其他触发控制信号,以便与被控对象连接,调节其工作状态。

结语

CPLD器件的物理机制像74系列、CD4000系列集成电路那样,纯属硬件电路,十分可靠。繁杂的开发工作是依赖功能强大的EDA软件实现的,入门门槛较低,易于初学者上手。目前正被越来越多的设计者青睐,普及推广只是时间问题。

随着微电子技术的发展,相信CPLD器件会有长足的进步,可能会与微机日益紧密结合,以致两者间界限模糊,你中有我,我中有你。

研制产品时,使CPLD器件与单片机的有机结合,不但缩短了开发周期,而且控制器配置灵活、修改方便、适应性强,加大了研制的自由度。容易满足用户的多元需求,从而争得商机。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:应用CPLD实现交通控制系统芯片设计

下一篇:自动断电的CPLD