- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

可编程逻辑器件的应用参考

引言

随着大规模超大规模可编程逻辑器件的发展,逻辑器件日益以其低廉的价格及灵活的设计方式、丰富完备的功能而广泛应用于电子线路设计中。采用CPLD可对逻辑电路功能进行综合集成,根据需要设计最小的单元,节约系统资源,极大的减少了电路板上功能模块及模块间连线。同时以其灵活的设计及在线升级方式对系统进行修改升级,减少了对电路板本身的修改,提高了系统整体可靠性,节约了制版费用,缩短了设计的周期。

但可编程逻辑器件使用中还有诸多需要注意的细节,特别是对于才开始应用其进行设计的电子线路设计人员,只有把握住这些细节才能成功的进行设计。

应用基础

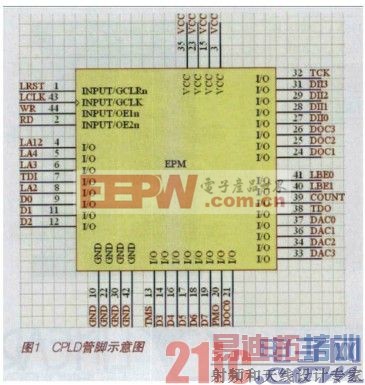

在设计之前需要对逻辑器件进行了解,以MAX7000系列为例,器件管脚设置如图1。这是将CPLD器件应用于PCI接口逻辑的一个示例,实现对PCI接口芯片输出的本地控制信号的译码及部分功能模块的嵌入式设计。

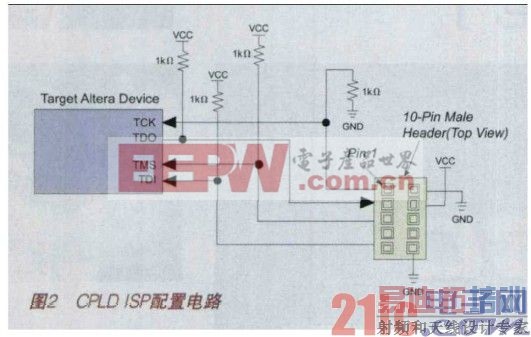

元件除去电源部分所需管脚,剩下的大部分是I/O口,可定义为系统所需控制管脚。需要注意几个全局信号控制脚,如GCLK、OE等管脚可用于整个逻辑器件工作时序的控制,一般用于全局信号的连接。同时需要注意的是TDI、TMS、TDO、TCK四个管脚是与在线编程相关的程序下载管脚,必要时候也可作为通用的管脚使用。ALTERA元件的下载线可以购买或是自行制作,资料比较完备。要实现在线编程,CPLD元件部分的PCB设计时需要注意,几个下载管脚不是悬空的,都必须进行上拉、下拉设计,电路如图2。这点容易忽略,而导致下载软件无法发现下层的器件,相关说明在文档“In-System Programmability”中。

在操作系统中安装相应的下载线驱动,就可在其图形化的设计软件中发现可编程控制器件,并对其进行在线编程、调试。

[p]

控制逻辑设计

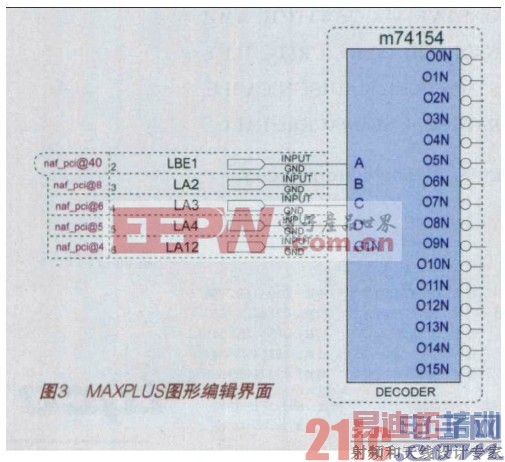

CPLD的巨大优势体现在其灵活性,可根据需要设计组合逻辑,减少了分离元件的使用,提高了系统的集成程度及可靠性。对于一般的应用采用MAX+plus编辑软件就可以完成,其界面简单,所有功能都集成于菜单中,可方便完成设计、综合、仿真、下载的全过程。图3为是应用74LS154对应软核设计的PCI接口译码电路,从而在CPLD内部实现4-16译码。电路图中可标明其用到的管脚,还可根据需要进行配置,以便于外部PCB设计的布线优化。

应用ALTERA公司的硬件开发语言AHDL及通用的VHDL等硬件描述设计语言,能实现软核的自主开发,同时可实现同步仿真,验证设计的逻辑正确性。以下是一个数字分频器设计示例。

SUBDESIGN NDivide

(

clk :INPUT;

clkoutD :OUTPUT;%偶分频输出%

BXCOUNTout[3..0] :OUTPUT;

COUNTAOUT[2..0] :OUTPUT;

)

VARIABLE

%偶分频变量%

COUNTD[3..0] :DFF;%小于16分频器,偶

数分频器%

clkRegD :DFF;

BEGIN

%偶分频部分%

COUNTD[].clk=!(clk);

clkRegD.d=!clkRegD.q;

clkoutD=clkRegD.q;

IF (COUNTD[].q==1) THEN%根据分频数定,2的n+1分

频,此处为4分频,2分频时clkRegD.clk=!clk即可%

COUNTD[].d=0;

ELSE

COUNTD[].d=COUNTD[].q+1;

END IF;

clkRegD.clk=COUNTD0.q;

END;

[p]

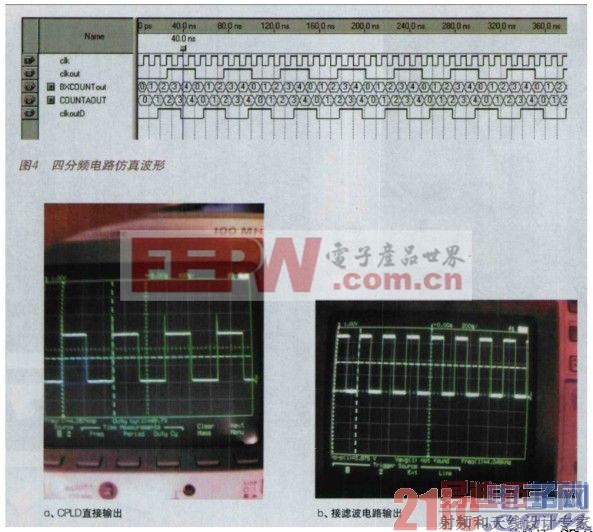

该程序仿真波形如图4,实现了四分频电路的逻辑设计、实现。

PCB电路设计

应用CPLD还需注意其输出脚状态改变时所产生的高频的脉冲,会对下一级器件带来严峻的考验。因此在 PCB设计中必须进行相应的处理,才能有效抑制脉冲的极值,同时保证上升沿的陡直。图5为一脉宽调制软核的输出效果图。该模块实现精度为8位的脉宽调制,方波信号基频为4kHz,由33M的PCI时钟分频得来。系统只应用最简单的阻容滤波电路来降低脉冲值。

该图为直接输出与滤波输出两种条件下的示波器显示图,在图a中没有采取滤波措施,可以看到在上跳沿处为4V左右的尖峰脉冲,相比稳定的高电平3V输出高出1V。而图b是经简单的阻容滤波电路后输出,上跳沿脉冲的峰值明显得到抑制。较大的改善了系统的性能。

结束语

应用可编程逻辑器件,可加速开发的进程,在器件提供的方针环境中进行功能的仿真验证,可及时发现设计中的缺陷。但是自带的仿真器本身也并非完美,在电路设计完成后还需进行更细致的验证。CPLD的广泛应用给电子线路设计人员有更大的发挥空间,更灵活的设计方式,极大的提高了设计效率。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...