- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

FPGA中可配置逻辑块(CLB)

录入:edatop.com 点击:

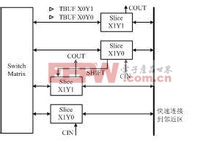

CLB是FPGA内的基本逻辑单元。CLB的实际数量和特性会依器件的不同而不同,但是每个CLB都包含一个可配置开关矩阵,此矩阵由4或6个输入、一些 选型电路(多路复用器等)和触发器组成。开关矩阵是高度灵活的,可以对其进行配置以便处理组合逻辑、移位寄存器或RAM。在Xilinx公司的FPGA器件中,CLB由多个(一般为4个或2个)相同的Slice和附加逻辑构成,如图1-3所示。每个CLB模块不仅可以用于实现组合逻辑、时序逻辑,还可以配置为分布式RAM和分布式ROM。

典型的CLB结构示意图

典型的CLB结构示意图Slice是Xilinx公司定义的基本逻辑单位,其内部结构如图1-4所示,一个Slice由两个4输入的函数、进位逻辑、算术逻辑、存储逻辑和函数复用器组成。算术逻辑包括一个异或门(XORG)和一个专用与门(MULTAND),一个异或门可以使一个Slice实现 2bit全加操作,专用与门用于提高乘法器的效率;进位逻辑由专用进位信号和函数复用器(MUXC)组成,用于实现快速的算术加减法操作;4输入函数发生 器用于实现4输入LUT、分布式RAM或16比特移位寄存器(Virtex-5系列芯片的Slice中的两个输入函数为6输入,可以实现6输入LUT或 64比特移位寄存器);进位逻辑包括两条快速进位链,用于提高CLB模块的处理速度。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:目前FPGA的应用主要是三个方向

下一篇:解决SoC

FPGA设计难题

射频和天线工程师培训课程详情>>