- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的全新数字化PCM中频解调器设计

摘要:为了对中频PCM信号进行直接解调,提出一种全新的数字化PCM中频解调器的设计方法。在实现过程中,采用大规模的FPGA芯片对位帧同步器进行了融合,便于设备的集成化和小型化。这种新型的中频解调器比传统的基带解调器具有硬件成本低和误码率低等优点。

关键词:FPGA;PCM;中频;解调器

在传统的数据接收处理流程中,遥测接收机将接收到的射频信号进行两次下变频到零中频,然后经过D/A输出基带信号;PCM数据流经过位同步、帧同步后恢复出数据,通过数据处理计算机将数据进行显示和存储。随着现代电子技术的迅猛发展,高速A/D芯片的出现和大容量FPGA芯片的成熟应用,高度集成的数字化解调技术应运而生,笔者提出了一种基于FPGA的全新数字化的PCM中频解调器的设计方

案。本方案具有高度的集成性,较低的误码率,硬件资源少、实现简单等优点。

1 功能和设计要求

1.1 中频解调器的功能

中频解调器主要完成对接收机70 M中频信号进行数字化处理,然后通过位同步器重建码元时钟、恢复串行数据和码型转换;通过帧同步器完成字、帧同步,对齐帧结构数据格式,并将串行数据流转换为并行数据流;最后通过计算机将数据进行存储和处理。其主要功能组成如图1所示。

1.2 中频解调器的技术要求

中频解调器的位速率、帧长等多项指标都是可编程设置的,具体指标如下:

1)输入频率:70MHz;

2)输入信号强度:(-10±5)dBm;

3)位速率范围100 kbps~5Mbps可编程;

4)码型:NRZ_L/M/S可选择;

5)字长:8;

6)帧长:8~10224可编程;

7)同步码长度:4~32位;

8)同步码位置:在前或在后;

9)输出:USB接口输出。

2 设计思路和方案

2.1 高速A/D采样设计

自软件无线电的概念提出后,模拟信号数字化是软件无线电设计中的关键所在。在软件无线电的设计中,A/D模块完成模拟信号到数字信号的转换,A/D采样频率的选择会对原有信号以及后面数字信号处理产生重要的影响,所以如何选择合适的采样频率是中频解调器的关健设计之一。采样定理主要包括Nyquist采样定理和带通采样定理,对于信号频谱分布在频带(fL,fH)上的带通信号进行采样,通常采用带通采样定理,来选取合适的采样频率。

根据带通信号采样理论公式,采样速率fs满足:

![]()

式中,n取能满足fs≥2(fH-fL)的最大正整数,则用fs进行等间隔采样所得到的信号采样值能准确地恢复原信号。

本系统中频带宽最大为10 M,因此ADC模块选用40 MHz的采样频率、12位量化。[p]

2.2 数宇变频及滤波器设计

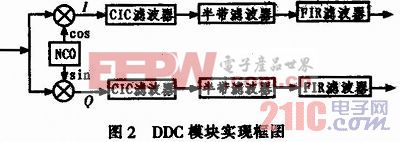

变频模块的设计是整个设计的关键部分之一。如图2所示,该模块由NCO、CIC滤波器、半带滤波器和FIB滤波器组成。NCO通过与A/D之后的中频信号进行混频,从而得到基带频率的I、O两路正交信号,这两路信号分别通过CIC滤波器、半带滤波器以及FIR滤波器的抽取和滤波,最终得到要求速率的数字信号,从而实现数字信号由中频频率到基带频率的转变。

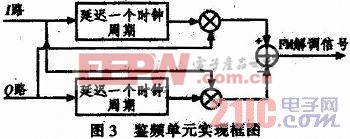

2.3 鉴频单元设计

从理论上来说,可以直接利用频率是相位对时间的微分关系来实现鉴频。假设瞬时频率为f(t),瞬时相位为φ(t),同相分量为I(t),正交分量为Q(t),则根据:

这就是利用I(n)、Q(n)计算瞬时频率f(n)的近似公式。

数字鉴频单元实现结构如图3所示。

2.4 跟踪环路设计

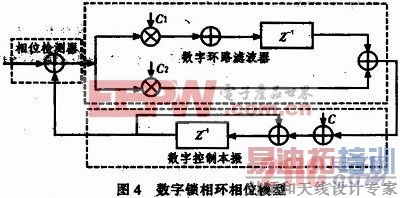

本系统设计中采用的是均匀采样二阶DPLL。

典型均匀采样二阶DPLL相位模型可以用图4来表示,它由相位检测器PD、数字环路滤波器(Digital Loop Filter)和数字控制本振(Numeri cally Control Oscillator)组成。在这个DPLL中,相位检测器PD根据输入相位或计算相位误差。相位误差通过数字环路滤波DLF并用于控制数字控制本振RCO的瞬时输出相位。在图4中,系数C1和C2是数字环路滤波器(DLF)的参数,是影响环路带宽和环路响应时间的重要参数,而C是确定DPLL中心频率的常数。这种DPLL的最大优点就是具有线性相位,从而保证了捕获时间小和锁相范围大的性能。[p]

均匀采样二阶DPLL误差传递函数幅频特性具有明显的高通特性,而且通带截止频率基本上和环路自由振荡频率一致,所以理论上只要恰当地选择环路自由振荡频率就可以得到我们所希望的等效高通滤波器。特别是当通带截止频率很小时,高通特性的性能会更好,因为通带将更加平坦。所以用这种方法实现窄带高通滤波器要比常规的FIR和HR滤波器都经济。因此,利用均匀采样二阶DPLL误差传递函效的高通特性滤除缓慢变化的载波频偏和多谱勒频率成份,实现等效的开环频率跟踪。

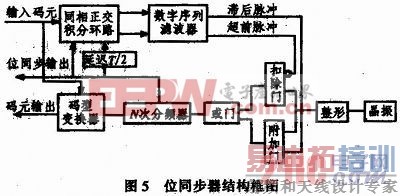

2.5 位同步设计

本设计方案中的位同步器主要由同相、正交积分环路、数字序列滤波器、分频器和码型变换器几部分组成。其结构原理如图5所示,下面将分别说明各个主要组成部分的原理与实现的功能。

同相正交积分环路主要用于实现对接收信号和同步信号的鉴相,利用匹配滤波的原理,比较接收到的信号和晶振产生经过分频后的信号两者之间的相位差,输出超前或滞后脉冲,用于调整位同步脉冲的相位。同相积分器在清除时刻的采样输出极性,取决于输入码元的极性,而与同步与否以及相位误差的极性无关。因此,可以将同相积分器的输出经过保持电路后再进行过零检测来得到码元转换的信息。

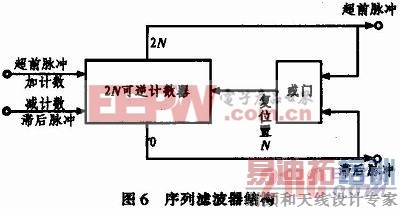

当存在噪声时,如果超前、滞后脉冲直接用于环路相位调节,将产生相位抖动,特别是在信噪比低或接近予零的情况下,问题更加严重。为此,环路中需要使用序列滤波器。这种滤波器专门用于鉴相器输出的超前或滞后脉冲的情况。它由计数容量为2N的可逆计数器构成,其结构如图6所示。

可逆计数器对超前脉冲进行向上计数,对滞后脉冲进行向下计数。在开始计数时,可逆计数器的状态为N,当超前脉冲比滞后脉冲多N个时,可逆计数器计满到容量2N,同时输出一个推后控制脉冲,以便用它去控制本地估算信号的相位推后一步。与此同时,或门就输出一个脉冲,将可逆计数量N,重新开始计数。而当滞后脉冲比超前脉冲多N个时,可逆计数器的计数值为0,同时输出一个提前控制脉冲,以便用它去控制本地估算信号的相位前移一步。这时,或门也输出一个脉冲,将可逆计数置N,重新开始计数。[p]

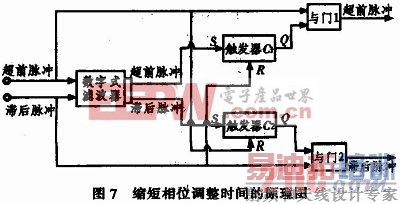

当锁相环路进入同步状态之后,超前或滞后脉冲产生的概率趋于相等。而由噪声引起的超前或滞后脉冲也是等概率的。因此,在这种情况下,计数器在N值上下徘徊,超前脉冲和滞后脉冲之差达到计数容量N的概率是很小的。所以,在锁相环路同步的状态下,序列滤波器通常是没有输出的。这就减少了由噪声引起的对锁相环路的误控作用。滤波器有效的滤除了噪声对环路的干扰,而且在同步状态下不产生附加的相位抖动。计数容量N的取值很重要,直接影响着环路的过渡过程。N取得大,对抑制噪声有利,但同时又加大了环路进入同步状态的时间,使得环路带宽变窄。反之,N取得小,可以加速环路的同步,而对噪声的抑制能力就随之降低,环路带宽变宽。因此根据实际情况以及不同的信噪比,选择不同的N值。本设计的随机徘徊滤波器采用可变模(N值可编程)设计,加大了可编程码同步器的灵活性。但是,加入数字序列滤波器后,虽然抗干扰性能有改善,但却使相位调整速度减慢了。若位同步脉冲的相位超前较多,鉴相器数要输出N个超前脉冲才能使位同步脉冲的相位调整一次,调整时间增加了N倍。为此给出了一种缩短相位调整时间的原理图如图7所示。

当输入连续超前(滞后)脉冲多于N个后,数字序列滤波器输出一超前(滞后)脉冲,使触发器GI(C2)输出高电平,打开与门1(与门2),输入的超前滞后脉冲就通过与门加至相位调整电路,如果鉴相器还连续的输出超前(滞后)脉冲,那么此时触发器的输出已使与门打开,这些脉冲就可以连续的送至相位调整电路,而不需要再等待N个。对随机干扰来说,输出的使零星的超前(滞后)脉冲,这会使触发器置“0”,这时电路的作用和数字序列滤波器相同,仍具有良好的抗干扰性能。N次分频器是一个简单的除N计数器。N次分频器对脉冲加减电路的输出脉冲再进行N分频,得到整个数字锁相环路输出的位同步时钟信号fclk。同时,因为fclk=CLK/2N,因此通过改变分频值N可以得到不同的环路中心频率。

2. 6 帧同步设计

输入数据流经过串/并转换后,与本地帧同步码进行同或运算,产生32位相关结果再与屏蔽位相与,屏蔽掉无关位后进入全加网络,经全加运算,以6位二进制码输出,然后与门限值进行比较。大于门限值表示接收到帧同步码。三态逻辑电路保证帧同步器在3个固定模式(搜索、校核、镇定)上工作。在搜索态,不使用窗口,符合相关器输出即认为是帧同步码。一旦接收到帧同步码,由搜索态转入校核态。位/字计数器、字/帧计数器复位,二者开始计数,这个过程一直持续到字/帧计数器达到预定的字/帧数。这时字/帧计数器输出一特定信号至窗口产生器,以预期检测位为中心产生窗口脉冲。利用帧同步码的周期性,下一个检测位应落在窗口脉冲宽度内,三态逻辑产生第二个帧标志脉冲。若在窗口范围内,没有帧码,在统计意义上多半是虚警,三态逻辑从校核重新返回到搜索态。在校核态,只有连续通过预定的校核帧数,帧同步器才进入锁定态。在锁定态,即使在帧同步码发生漏检或数据错误的情况下,帧标志脉冲也由本地产生。从而避免了由于帧同步码的漏检而造成的数据丢失。连续漏检超过预定的保护帧数,帧同步即返回搜索态,否则将重新计数,一直保持在锁定态。

3 测试结果和分析

在实验室内使用一个性能指标较高的下变频器和该设备配合进行了测试,测试结果见表1。从测试结果来看该设备能够在1~3Mbps的位速率范围内完成数据的可靠解调,误码率在允许范围之内。

在后续长时间拷机测试过程中,该解调器工作性能稳定。在使用信号源对该解调器测试时,输入信号强度在0~30dBm内范围变化,输入调制信号频率在100 kbps~5Mbps范围内变化时,该解调器也能够很好地工作,说明了全新数字化中频解调器的设计是稳定可靠的,可以进行下一步工程化研制。而该设计的集成度高、体积尺寸小,便于小型化设计应用等优点体现了该设计的优越性,将来必定会得到越来越广泛的应用。

4 结束语

目前应用范围较广的解调器解调位速率比本设计要高,在10Mbps以上,因此本设计的下一步的改进方向是将解调能力进行扩展,这主要取决于所选择的FPGA内部锁相环的时钟和FPGA的容量及数据处理速度。

文中方法只是对从中频直接进行采样、鉴频、进行位帧同步的验证,实践证明该方法设计有效,测试结果接近理想值,下一步目标是完成工程化研制,投入实践应用。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...